PSS-4

advertisement

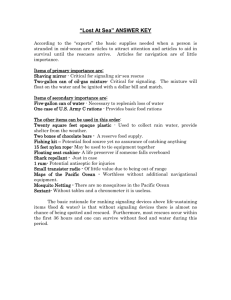

A Novel Signaling Technique for High-speed Wireline Backplane Transceiver: Four Phase-shifted Sinusoid Symbol (PSS-4) Kejun Wu∗† , Peng Liu∗† , and Qiaoyan Yu‡ ∗ Department of Information Science and Electronic Engineering, Zhejiang University, Hangzhou, 310027, China Key Laboratory of Mathematical Engineering and Advanced Computing, Wuxi, 214083, China ‡ Department of Electrical and Computer Engineering, University of New Hampshire, Durham, NH 03824, USA † State Abstract—This paper proposes a novel four phase-shifted sinusoid symbol (PSS-4) signaling technique to relief high-speed wireline backplane transceiver to reduce large intersymbol interference. The four-level pulse amplitude modulation (PAM-4) and other existing amplitude modulation techniques have been widely used to simplify transceiver equalization design for highly dispersive channels. Unfortunately, PAM-4 and other methods reduce the symbol rate at the expense of signal-to-noise ratio (SNR) and thus limit the bit-error-rate (BER). The proposed PSS4 signaling avoids large SNR degradation by using four phaseshifted symbols to transmit two-bit data. The experimental results show that with sufficient equalization, our PSS-4 signaling can achieve over 2 dB larger SNR than the conventional non-returnto-zero (NRZ), Duobinary, and PAM-4 signaling techniques. In addition, for a target BER of 1E-12, the proposed PSS4 signaling has the largest sampling range comparing against existing backplane signaling techniques. Furthermore, compared with NRZ-based backplane transceiver, PSS-4 signaling reduces the equalizer power consumption by 24%. I. I NTRODUCTION As the industry-standard data rate of wireline backplane communication approaches 25 Gb/s and beyond [1], [2], the performance of backplane transceiver integrated on chip becomes challenged. Signal integrity issues, such as attenuations, reflections, intersymbol interference (ISI), and crosstalk, make the backplane channel band-limited. Conventional equalization optimization techniques in backplane transceivers [3]–[5], have constraints for next generation high-speed electrical serial links, i.e., 25-28 Gb/s [1]. The transceiver needs to incorporate equalizers with large number of taps to cancel the ISI [2]. However, it is power-hungry for implementing such a complex feed-forward equalizer (FFE) in the transmitter and a decisionfeedback equalizer (DFE) in the receiver. To relax the equalizer design, an area of intensive research in recent years deals with multi-level signaling techniques, such as four-level pulse amplitude modulation (PAM-4) [6], [7] and Duobinary [8], [9]. Although the symbol rate of PAM-4 can be reduced to half of non-return-to-zero (NRZ), This work was supported in part by State Key Laboratory of Mathematical and Advanced Computing Program, IBM Visiting Scholar Program under the grant VS201303X, Huawei Technologies Co. Ltd Research Program, NSFC under the grants 60873112 and 61028004, and National High Technology Research and Development Program of China under the grant 2009AA01Z09. ∗ The corresponding author is Peng Liu, Email: liupeng@zju.edu.cn. 978-1-4799-3432-4/14/$31.00 ©2014 IEEE 2141 a drawback of it is that for a given maximum voltage limit, the distance between each voltage level is only one third of NRZ, resulting in a 9.5 dB of signal-to-noise ratio (SNR) penalty [10]. Therefore, it is imperative to investigate an optimal signaling technique for the high-speed wireline backplane application. This paper proposes a four phase-shifted sinusoid symbol (PSS-4). This novel signaling technique for wireline backplane transceiver reduces the symbol rate by half but with only 3 dB SNR penalty. On the other hand, PSS-4 signaling is more spectrally-efficient than other existing backplane signaling techniques, resulting in better performance and lower power consumption in equalizers. The PSS-4 signaling technique employed on the wireline backplane transceiver is the major focus of this work. The rest of the paper is organized as follows. Section II details the key circuits of PSS-4 signaling codec, and compares with the conventional NRZ, Duobinary, and PAM-4 signaling techniques. The experimental results of the signaling techniques evaluation are discussed in Section III, and Section IV concludes the paper. II. S IGNALING T ECHNIQUE Standards bodies are now examining how to increase the throughput of high-density backplane links to 25 Gb/s and beyond [11], [12]. One method for achieving this is to construct premium backplane links utilizing advanced materials and connectors. Another approach is to reuse legacy backplanes by employing PAM-4 or other signaling at half of the baud rate. To attack the large SNR degradation problem of multiamplitude modulation, a phase modulation technique (i.e., four phase-shifted sinusoid symbol (PSS-4)) is proposed. The codec of PSS-4 signaling for backplane communication is depicted in Fig. 1. As an example of 25 Gb/s data rate, regarding that the symbol rate is 12.5 Gbaud/s, we use half cycle of the sine wave as the transmission symbol. Therefore, a four-phase shifted symbol of 6.25 GHz half-cycle sine wave is transmitted in each unit interval (UI), selected by even and odd data of 12.5 Gb/s. The circuit design is also shown in Fig. 1. It is implemented by a 4-to-1 current-mode logic (CML) selector, integrated with inductive-peaking technology for bandwidth enhancement. This is the encoding process. A 6.25 GHz clock with two orthogonal phases is used for DFE decision in the receiver. The two decision time points are A and B, i.e., 20 VDD 90° 0° Decision Points VDD 270° 180° Data_Odd Data_Odd Data_Even Data_Odd Data_Even 0° 180° 270° A Channel 4-to-1 Selector 90° Coding 1 1 80ps 0 0 0 1 1 0 B L L 12.5 Gb/s Odd bit L L 12.5 Gb/s Even bit 6.25 GHz clock 0.707 0 20ps 60ps -0.707 Fig. 1. The codec of proposed PSS-4 signaling. ps and 60 ps for an unit interval of 80 ps, as shown in the figure. All the latches used in the encoder and decoder are CML latches. The power spectral density of PSS-4 and PAM-4 can be expressed as (1) and (2) ΦP SS−4 = 1 Tb (sinc2 (4Tb (f + 6.25))+ 2 sinc2 (4Tb (f − 6.25))) ΦP AM −4 10 = Tb sinc2 (2Tb f ) 9 (1) (2) where Tb is the bit period and f is the frequency. We can see the energy of PSS-4 signal has been shifted up to 6.25 GHz. For a given data rate, PAM-4 and PSS-4 reduce the symbol rate by half, suffering less attenuation due to smaller Nyquist frequency. Moreover, the power spectral distribution of PSS-4 is more concentrated than that of PAM-4. The SNR is defined as the square of the mean of the outer-most symbol divided by the sum of the variances of the individual error terms (e.g., ISI, crosstalk, Gaussian noise, jitter-induced amplitude error, etc.), which is given by (3) SN R = D2 σ2 (3) TABLE I. E XPERIMENTAL S ETUP Data rate Transmitter deterministic jitter Transmitter random jitter Transmitter output rise-time (20%-80%) AWGN 2-sided power spectral density, N0 /2 Receiver random jitter 25 Gb/s 3.2 ps 0.35 ps 18.6 ps -114 dBm/Hz 0.35 ps where M is the number of voltage levels. From (4), the symbol error rate can be translated to a corresponding SNR value. The SNR margin is defined as the SNR at the decision point minus the SNR required to achieve the target BER. According to (4), in order to achieve BER of 1E-12, the SNR values of NRZ, Duobinary, PAM-4, and PSS-4 must be 16.9 dB, 23.0 dB, 26.5 dB, and 19.9 dB, respectively. As can be seen, the SNR penalty of PAM-4 and Duobinary are 9.5 dB and 6.1 dB comparing with NRZ. Fortunately, the SNR penalty of PSS-4 is reduced to only 3.0 dB. Comparing NRZ and PSS-4, one can see that the SNR must be 3.0 dB larger for PSS-4 to achieve the same symbol error probability. That is to say, if the channel loss difference between Nyquist frequency of NRZ and PSS-4 is larger than 3.0 dB, PSS-4 can be an alternative signaling to NRZ. Comparing to the PAM-4 signaling, the PSS-4 signaling technique can alleviate SNR penalty. III. E XPERIMENTAL R ESULTS A. Experimental Setup where D is the voltage space. The expression for the probability of a symbol error, i.e., Pe , can be calculated as (4) s 1 SN R Pe = (1 − )erf c( ) (4) M 2(M − 1)2 2142 The backplane transceiver is modeled in behavior-level using M AT LAB. In order to evaluate the performance against different channel characteristics and various noise scenarios, multiple channel models are estimated. These backplane models are provided by IEEE 802.3 ap Task Force [13] and varied PSS-4 for T 20 Fig. 3. PAM-4 PSS-4 Average B32 M32 T20 Molex5 Molex4 Molex3 Molex2 Tyco7 PSS-4 for T yco1 PSS-4 for Molex1 3 Duobinary Molex1 6 NRZ -4 Tyco6 9 -2 Tyco5 12 0 Tyco4 SNR (dB) 15 2 Tyco3 18 4 Tyco2 21 6 Tyco1 SNR Margin /dB (BER=10 -12 ) 24 SNR margin comparison of four signaling techniques. 0 3 3 3 3 3 3 3 3 3 3 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 1.0E+00 1.0E-02 SNR for PSS-4 using different equalization schemes. 1.0E-04 B. Equalization Selection As illustrated in Fig. 2, various equalization schemes are evaluated for PSS-4 signaling in the case of Tyco1, Molex1, and T20 channels. With a certain number of the equalizer taps, performance gets minor improvement as the number of taps increases further. For Molex1 channel, 3-tap FFE plus 9-tap or 10-tap DFE is basically sufficient. But this equalization configuration cannot be enough for Tyco1 and T20 channels, until the number of DFE taps is increased to 15 or 16. The combination of 3-tap FFE (FFE3) and 16-tap DFE (DFE16) is sufficient for compensating most of the channel loss. Therefore, the combination of 3-tap FFE (FFE3) and 16-tap DFE (DFE16) is sufficient for compensating most of the channel loss. We make performance comparison of the conventional NRZ, Duobinary, PAM-4, and PSS-4 signaling techniques for backplane transceivers. The equalization scheme of 3-tap FFE plus 16-tap DFE is chosen for evaluation. C. Signaling Techniques Comparison Fig. 3 shows SNR margin results. According to the figure, NRZ has better performance than Duobinary and PAM-4, with 1.4 dB and 1.9 dB SNR margin larger on average, respectively. With sufficient equalization compensating, systems with different signaling techniques can get close to or even exceed the target BER of 1E-12, meaning that most of the ISIs have been cancelled. In such a case, PAM-4 has a SNR penalty of 9.5 dB over NRZ, making it difficult to exceed NRZ on BER (also represented as ’SNR margin’). The performance degradation also occurs for Duobinary, but not as much as PAM-4. As 2143 1.0E-08 NRZ Duobinary PAM-4 PSS-4 1.0E-10 4 5 0. 0. 1.0E-12 -0 .5 with different geometry structures of on-board transmission line, different dielectric material, etc. The channel models described in .s4p files are translated into frequency response in .m code, for both insertion loss data and crosstalk data. Other electronics noise rather than crosstalk is modeled as additive white Gaussian noise (AWGN), referred as power spectral density, N0 /2. The effects of rise time and fall time are added to the simulator by reshaping the symbol pulse to its rise/fall time. The SNR margin is used as a figure of merit for evaluation. The experimental parameters of simulation system are shown in Table I. 1.0E-06 3 3 0. 3 2 3 0. 3 1 3 0. 3 0 3 -0 .1 3 -0 .2 3 BER Fig. 2. 3 -0 .3 DFE tap number 2 3 4 -0 .4 FFE tap number Sampling Position (UI) Fig. 4. Bathtub curve of four signaling techniques. a result, the SNR margin of Duobinary is between NRZ and PAM-4. With only 3.0 dB SNR penalty, the PSS-4 signaling has larger SNR margin than NRZ, 2.0 dB larger on average. Fig. 4 shows the bathtub curve of four signaling techniques for the case of Tyco1 channel, with the crosstalk, noise, and jitter are taken into consideration. With a target BER of 1E-12, only NRZ and PSS-4 have the opening eyes. The sampling point can be shifted within about 0.16 UI for PSS-4, while that of NRZ is only 0.11 UI. With a BER of 1E-6, the sampling range would be 0.30 UI for PSS-4 and 0.21 UI for NRZ. PAM-4 has the smallest sampling range of 0.07 UI due to the large SNR degradation. It is worth noting that PSS4 signaling has the widest reliable sampling range in these signaling techniques. D. Power Estimation Equalizers are power-hungry elements of backplane transceiver, for these circuits are usually implemented in current-mode logic (CML). We make a power estimation of equalizers based on four signaling techniques. For a fair comparison, we make a hypothesis that both FFE combiner and DFE summer are implemented by current-mode resistor-load architecture, which is widely used in high-speed transceivers. In this case, the power consumption of equalizers is proportional to the total current, which is summed by the current of each tap [14]. Therefore, the total power consumption of equalizers is proportional to the absolute value of tap coefficient, presented as PF F E,DF E = P0 ∗ n−1 X i=0 |Ci | (5) NRZ 3.0 Duobinary PAM-4 technique. Experimental results show that PSS-4 signaling technique has larger SNR margin over other backplane signaling techniques in the case of aggressive equalizer combination scenarios. In the future, we will make a further design space exploration on the equalization schemes and signaling techniques for high-speed wireline backplane transceivers. PSS-4 Power (P0) 2.5 2.0 1.5 1.0 0.5 R EFERENCES Average B32 M32 T20 Molex5 Molex4 Molex3 Molex2 Tyco7 Molex1 Tyco6 Tyco5 Tyco4 Tyco3 Tyco2 Tyco1 0.0 [1] Fig. 5. Power consumption of FFEs and DFEs based on four signaling techniques. [2] TABLE II. P OWER C ONSUMPTION OF S IGNALING C IRCUITRY FOR D UOBINARY, PAM-4, AND PSS-4 (NRZ HAS NO SUCH COST ) Signaling Technique Module Encoder Duobinary Decoder Encoder PAM-4 Decoder PSS-4 Encoder Decoder Sub-circuit Power (mW) Adder XOR DFF Comparator*2 OR 4-to-1 Selector DFF Comparator*3 Thermocode/Binary 2-to-1 Serializer 4-to-1 Selector 1-to-2 Deserializer DFF*2 15.21 1.86 10.16 0.21 0.54 1.89 9.70 0.32 9.02 18.61 2.28 21.12 16.03 27.23 [3] 27.98 0.75 11.59 39.32 [4] 27.73 23.40 39.43 [5] 16.03 where P0 is the power consumption for tap coefficient equals to 1.0, n is the tap number, and Ci is the coefficient of ith tap. Fig. 5 shows the power estimation of these signaling techniques. Due to the high bandwidth efficiency of proposed PSS4 signaling, it can reduce the coefficient values of equalizers. As the figure shows, PSS-4 signaling technique can reduce the equalizer power dissipation by an average of 24%, compared with NRZ. Rather than NRZ, other three signaling techniques need extra cost for codec circuits. Transistor-level simulation has been done using Cadence Spectre simulator on TSMC 65nm CMOS technology. Encoder and decoder are implemented according to the design in Fig. 1. The detailed power dissipations for sub-circuitry of each encoder and decoder are listed in Table II. As the table shows, the encoders of PAM-4 and PSS-4 signals consume less power than Duobinary because the clock frequency is reduced by half. However, the most powerhungry sub-circuit in encoder and decoder modules is CML latch. Therefore, DFF, serializer, and deserializer dissipate large amount of power for encoding and decoding. IV. [6] [7] [8] [9] [10] [11] [12] [13] C ONCLUSION The growing demand for higher backplane communication bandwidth pushes next-generation I/O data rates towards 25 Gb/s and beyond. To increase the throughput of high-density backplane links and attack the large SNR degradation problem of multi-amplitude modulation, we propose PSS-4 signaling 2144 [14] “Common Electrical I/O (CEI) - electrical and jitter interoperability agreements for 6G+ bps, 11G+ bps, 25G+ bps I/O. Optical Internetworking Forum,” Sep. 2011, http://www.oiforum.com/public/ documents/OIF CEI 03.0.pdf. J. F. Bulzacchelli, C. Menolfi, T. J. Beukema, D. W. Storaska, J. Hertle, D. R. Hanson, P.-H. Hsieh, S. V. Rylov, D. Furrer, D. Gardellini, A. Prati, T. Morf, V. Sharma, R. Kelkar, H. A. Ainspan, W. R. Kelly, L. R. Chieco, G. A. Ritter, J. A. Sorice, J. D. Garlett, R. Callan, M. Brändli, P. Buchmann, M. Kossel, T. Toifl, and D. J. Freidman, “A 28-Gb/s 4-tap FFE/15-tap DFE serial link transceiver in 32-nm SOI CMOS technology,” IEEE J. Solid-State Circuits, vol. 47, no. 12, pp. 3232–3248, Dec. 2012. A. L. Pola, D. E. Crivelli, J. E. Cousseau, O. E. Agazzi, and M. R. Hueda, “A new low complexity iterative equalization architecture for high-speed receivers on highly dispersive channels: Decision feedforward equalizer (DFFE),” in Proc. IEEE Int. Symp. Circuits Syst., May 2011, pp. 133–136. J. Kim, E.-H. Chen, J. Ren, B. S. Leibowitz, P. Satarzadeh, J. L. Zerbe, and C.-K. K. Yang, “Equalizer design and performance trade-offs in ADC-based serial links,” IEEE Trans. Circuits Syst. I, vol. 58, no. 9, pp. 2096–2107, Sep. 2011. T. Beukema, M. Sorna, K. Selander, S. Zier, B. L. Ji, P. Murfet, J. Mason, W. Rhee, H. Ainspan, B. Parker, and M. Beakes, “A 6.4Gb/s CMOS serdes core with feed-forward and decision-feedback equalization,” IEEE J. Solid-State Circuits, vol. 40, no. 12, pp. 2633– 2645, Dec. 2005. J. Lee, M.-S. Chen, and H.-D. Wang, “Design and comparison of three 20-Gb/s backplane transceivers for duobinary, PAM4, and NRZ data,” IEEE J. Solid-State Circuits, vol. 43, no. 9, pp. 2120–2133, Sep. 2008. B. Min, K. Lee, and S. Palermo, “A 20Gb/s triple-mode (PAM-2, PAM4, and Duobinary) transmitter,” Microelectronics J., vol. 43, no. 10, pp. 687–696, Oct. 2012. W. T. Beyene and A. Amirkhany, “Controlled intersymbol interference design techniques of conventional interconnect systems for data rates beyond 20 Gbps,” IEEE Trans. Adv. Packag., vol. 31, no. 4, pp. 731– 740, Nov. 2008. K. Hu, L. Wu, and P. Y. Chiang, “A comparative study of 20-Gb/s NRZ and duobinary signaling using statistical analysis,” IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 20, no. 7, pp. 1336–1341, Jul. 2012. D. G. Kam, T. J. Beukema, Y. H. Kwark, L. Shan, X. Gu, P. K. Pepeljugoski, and M. B. Ritter, “Multi-level signaling in high-density, high-speed electrical links,” in Proc. IEC DesignCon, 2008. A. Healey and C. Morgan, “A comparison of 25Gbps NRZ & PAM-4 modulation used in legacy & premium backplane channels,” in Proc. IEC DesignCon, 2012. A. Healey, C. Morgan, and S. Megha, “Beyond 25 Gbps: A study of NRZ & multi-level modulation in alternative backplane architectures,” in Proc. IEC DesignCon, 2013. “Backplane channel model,” http://grouper.ieee.org/groups/802/3/ap/ public/channel model/archive/. J. F. Bulzacchelli, M. Meghelli, S. V. Rylov, W. Rhee, A. V. Rylyakov, H. A. Ainspan, B. D. Parker, M. P. Beakes, A. Chung, T. J. Beukema, P. K. Pepeljugoski, L. Shan, Y. H. Kwark, S. Gowda, and D. J. Friedman, “A 10-Gb/s 5-tap DFE/4-tap FFE transceiver in 90-nm CMOS technology,” IEEE J. Solid-State Circuits, vol. 41, no. 12, pp. 2885–2900, Dec. 2006.