CMOS-MEMS Variable Capacitors for Reconfigurable RF Circuits

Submitted in partial fulfillment of the requirements for

the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

John R. Reinke

B.E.E., Electrical Engineering, University of Minnesota

M.S., Electrical Engineering, Carnegie Mellon University

Carnegie Mellon University

Pittsburgh, PA

May, 2011

© John Reinke 2011

All rights reserved.

ii

Acknowledgements

First, I am grateful to Tamal Mukherjee and Gary Fedder for serving as my advisors during

my graduate studies at Carnegie Mellon University. Their guidance has been invaluable, and their

commitment to producing quality students has made the CMU MEMS lab a nurturing

environment. Their sense of humor and understanding helped immensely during the inevitable

frustrations of research.

My colleagues from the MEMS lab have been both helpful and entertaining. Leon Wang has

provided many important insights as he served as resident circuits guru. Peter Gilgunn has

inspired me to work harder and always strive for excellence. Nathan Lazarus and Yu-Jen Fang

were always willing to participate in random musings about science and technology. Abhishek

Jajoo, Sarah Bedair, and Fernando Alfaro helped me get my research off the ground. Amy Wung

and Kristen Dorsey deserve much credit for actually trying to foster a social environment within

the lab.

Many thanks to Suresh Santhanam and the staff of the Nanofabrication Facility for the many

CMOS-MEMS chips they have fabricated. They have battled through phenomenon such as the

mystery gunk and always managed to produce quality devices.

Last but certainly not least, I am thankful for the support of my family back home in

Minnesota. My family has been a needed refuge during holidays and vacations. I am truly lucky

to have them in my life.

This work was funded by the Industrial Technology Research Institute (ITRI) and by

government support under and awarded by DoD, Air Force Office of Scientific Research,

National Defense Science and Engineering Graduate (NDSEG) Fellowship, 32 CFR 168a.

iii

Abstract

Microelectromechanical systems (MEMS) variable capacitors have demonstrated excellent

performance in terms of tuning ratio and quality factor (Q) at radio frequencies (RF). These

characteristics can enhance existing RF circuits and enable frequency-reconfigurable circuits.

However, MEMS are typically not monolithically integrated with complementary metal-oxidesemiconductor (CMOS) processes. To achieve integration with CMOS, this work uses maskless

post-CMOS processing to create two types of CMOS-MEMS variable capacitors, the gap-tuning

capacitor and the digital capacitor. To show that these capacitors enable frequency-reconfigurable

circuits, the digital capacitor was used to develop the first CMOS-MEMS phase shifter.

The CMOS-MEMS gap-tuning capacitor uses lateral electrothermal actuation to control the

gap between electrodes. A mechanical latch maintains the capacitance without consuming static

power. This capacitor achieved series and shunt tuning ratios up to 6.9:1 and 5.7:1, respectively,

with a Q of 80 at 1 GHz. Millions of actuation cycles were demonstrated without failure

However, the gap-tuning capacitor had several disadvantages, specifically large device variation,

a non-linear distribution of capacitance values, and low capacitance density, which inspired

development of the digital capacitor.

The CMOS-MEMS digital capacitor consists of many switched capacitors that are organized

into capacitive bits to produce a linear distribution of capacitance values. This capacitor uses

both vertical electrothermal actuation and lateral electrostatic actuation to achieve large tuning

ratios without sacrificing capacitance density. The maximum capacitance state is maintained by

electrostatic force to prevent static power consumption. The digital capacitor achieved series and

shunt tuning ratios up to 73:1 and 19:1, respectively, with a Q of 369 at 1 GHz. Compared with

that of the gap-tuning capacitor, the capacitance density was increased by 5x and the device

variation was reduced by 4x. Reliability tests revealed evidence of mechanical fatigue after

iv

millions of actuation cycles, but no catastrophic failures occurred.

The CMOS-MEMS phase shifter consists of a micromachined transmission line periodically

loaded with digital capacitors. The digital capacitors were modified to achieve a shunt tuning

ratio of 7.2:1 with a Q of 18.8 at 30 GHz. The phase shifter produced an average insertion loss

and maximum phase shift of 2.9 dB and 337.5°, respectively, at 32 GHz.

v

Table of Contents

Chapter 1. Introduction ............................................................................................................... 1

1.1. Motivation ........................................................................................................................ 1

1.2. MEMS Variable Capacitors ............................................................................................. 2

1.3. Thesis Statement .............................................................................................................. 9

1.4. Contributions .................................................................................................................. 10

Chapter 2. CMOS-MEMS Background.................................................................................... 12

2.1. CMOS-MEMS Process .................................................................................................. 12

2.2. Electrothermal Actuation ............................................................................................... 17

Chapter 3. Gap-tuning Capacitor .............................................................................................. 23

3.1. Motivation ...................................................................................................................... 23

3.2. Topology ........................................................................................................................ 28

3.3. Analysis .......................................................................................................................... 33

3.4. Design............................................................................................................................. 38

3.5. Characterization ............................................................................................................. 41

3.6. Discussion ...................................................................................................................... 57

Chapter 4. Digital Capacitor ..................................................................................................... 61

4.1. Motivation ...................................................................................................................... 61

4.2. Topology ........................................................................................................................ 64

4.3. Analysis .......................................................................................................................... 67

4.4. Design............................................................................................................................. 74

4.5. Characterization ............................................................................................................. 78

4.6. Discussion ...................................................................................................................... 99

Chapter 5. Phase Shifter ......................................................................................................... 102

5.1. Motivation .................................................................................................................... 102

5.2. Topology ...................................................................................................................... 104

5.3. Analysis ........................................................................................................................ 108

5.4. Design........................................................................................................................... 111

5.5. Characterization ........................................................................................................... 114

5.6. Discussion .................................................................................................................... 123

Chapter 6. Conclusions ........................................................................................................... 126

6.1. Summary ...................................................................................................................... 126

6.2. Contributions ................................................................................................................ 128

6.3. Future Work ................................................................................................................. 130

6.4. Final Thoughts.............................................................................................................. 135

References ................................................................................................................................... 137

Appendix A. Electrical Characterization ................................................................................ 142

A.1. Network Analyzer Settings .......................................................................................... 142

A.2. Open-short De-embedding ........................................................................................... 143

A.3. Extracting an Equivalent Circuit Model....................................................................... 145

A.4. Matlab Code ................................................................................................................. 157

Appendix B. List of Cadence Layouts .................................................................................... 166

vi

List of Tables

Table 1.1: Variable Capacitor Characteristics ................................................................................ 6

Table 3.1: Gap-Tuning Capacitor Design Parameters .................................................................. 40

Table 3.2: Electrical Characteristics of the Gap-tuning Capacitor ............................................... 45

Table 3.3: Gap-Tuning Capacitor Results..................................................................................... 58

Table 4.1: Digital Capacitor Design Parameters ........................................................................... 77

Table 4.2: Electrical Characteristics of the Initial Digital Capacitor ............................................ 83

Table 4.3: Electrical Characteristics of the Updated Digital Capacitor ........................................ 98

Table 4.4: Digital Capacitor Results ........................................................................................... 100

Table 5.1: Phase Shifter Design Parameters ............................................................................... 112

Table 5.2: Electrical Characteristics of the Phase Shifter Digital Capacitor .............................. 118

Table 5.3: Electrical Characteristics of the Phase Shifter ........................................................... 122

Table 5.4: Comparison of Phase Shifters .................................................................................... 124

Table 6.1: Comparison of Integrated Variable Capacitors.......................................................... 129

Table B.2: List of Cadence Libraries .......................................................................................... 166

Table B.1: List of Cadence Layouts ............................................................................................ 166

vii

List of Figures

Fig. 1.1. Diagram of capacitance tuning by changing the (a) gap (b) overlap area (c) dielectric.

All capacitors have length L, width W, and gap g before part of the structure undergoes

displacement d. Capacitance calculations ignore the effects of fringing fields. ............................. 2

Fig. 2.1. Cross-section of the CMOS-MEMS process flow (a) beginning with CMOS chip (b)

after the vertical oxide etch (c) after the vertical silicon etch (d) after silicon release etch. ......... 13

Fig. 2.2. SEM image of (a) 20 µm squared released from the substrate (b) 60 µm square anchored

to the substrate. These test structures were fabricated using the 0.18 µm BiCMOS process from

TowerJazz. .................................................................................................................................... 14

Fig. 2.3. Diagram of a vertical electrothermal actuator beam. The polysilicon resistor for heating

can either be lumped near the anchor point or distributed along the length of the actuator beam.20

Fig. 2.4. Diagram of a lateral electrothermal actuator beam. The offset metal layers are switched

to the opposite side of the beam halfway along the length to produce guided-end motion at the

tip. ................................................................................................................................................. 21

Fig. 2.5. Microscope image of lateral electrothermal actuator (a) deflected due to residual stress

(b) after heating. (c) Focused-ion beam image of electrothermal actuator beam cross-section. ... 22

Fig. 3.1. Concept of the actuation method for the gap-tuning capacitor. ...................................... 24

Fig. 3.2. SEM image of the (a) 1st (b) 2nd (c) 3rd (d) 4th design of the gap-tuning capacitor. ........ 25

Fig. 3.3. Vertical misalignment of capacitive beams viewed as (a) SEM image (b) diagram. The

observed vertical misalignment is not as exaggerated as in the diagram but still significant

enough to affect the tuning ratio. .................................................................................................. 26

Fig. 3.4. SEM image of the (a) 1st (b) 2nd (c) 3rd design of the mechanical latch for gap-tuning

capacitors. ..................................................................................................................................... 27

Fig. 3.5. Diagram of gap-tuning capacitor. Arrows denote the directions of self-assembly and

electrothermal actuation displacements for both the gap and latch actuators. Resistor symbols

indicate the location of embedded polysilicon resistors used for electrothermal actuation. The

specific numbers of capacitive, actuator, and interconnect beams are not representative of the

numbers of beams used in the actual device. ................................................................................ 28

Fig. 3.6. Vertical curling of CMOS-MEMS beams. Anchoring MEMS beams at a common

location prevents vertical misalignment. ...................................................................................... 29

Fig. 3.7. SEM image of the mechanical latch for the gap-tuning capacitor. As pictures, the latch

is engaged in an intermediate capacitance position, neither minimum nor maximum capacitance.

....................................................................................................................................................... 31

Fig. 3.8. SEM image of the gap actuator for the gap-tuning capacitor. The shading of the actuator

beams changes half-way along their length because the offset metal layers are switched to the

other side of the beams. ................................................................................................................ 31

Fig. 3.9. Thermal isolation unit viewed as (a) SEM image (b) cross-section diagram. The metal 3

and metal 4 pictured in the diagram are not floating; these metals are connected to ground along a

different cross-section. .................................................................................................................. 32

Fig. 3.10. Cross-section of CMOS-MEMS beams used in the electrothermal gap-tuning

capacitor. ....................................................................................................................................... 33

Fig. 3.11. Diagram of capacitive beams for displacement x. ........................................................ 34

Fig. 3.12. Electric field magnitude for cross-sections of capacitive beams in both minimum and

maximum capacitance positions. The white, unmeshed areas represent the discrete metal layers

of the CMOS-MEMS beams. ........................................................................................................ 35

viii

Fig. 3.13. Capacitance per unit length as a function of vertical offset for different gaps. Vertical

misalignment between capacitive beams has a much larger impact when the gap is small. ........ 36

Fig. 3.14. SEM image of CMOS-MEMS variable capacitor. ....................................................... 41

Fig. 3.15. Microscope image of the gap-tuning capacitor in (a) maximum capacitance position (b)

minimum capacitance position. The latch appears retracted because voltage was applied to the

heating resistors in the latch actuator. ........................................................................................... 42

Fig. 3.16. Microscope image of the latch at position (a) 1 (b) 2 (c) 3 (d) 4 (e) 5 (f) 6. Each

position corresponds to a different capacitance value at which the variable capacitor can be

maintained without consuming power. ......................................................................................... 42

Fig. 3.17. Microscope image of capacitive beams pushed into mechanical contact (a) for the bestperforming capacitor (b) for a capacitor with significant lateral curling. The amount of curling is

small but still has significant effects of the minimum effective air gap. ...................................... 42

Fig. 3.18. Optical profilometer image of electrothermal gap-tuning capacitor. The capacitive

beams are vertically aligned to within 1.6 µm. ............................................................................. 43

Fig. 3.19. S-parameter magnitude as a function of frequency for (a) the minimum capacitance

position (b) the maximum capacitance position. S12 is not plotted because S12 and S21 are

equivalent for passive networks. ................................................................................................... 44

Fig. 3.20. Equivalent circuit model in terms of (a) Y-parameters and (b) lumped circuit elements.

Circuit element values are extracted from measured 2-port network parameters. ........................ 44

Fig. 3.21. Lumped impedances as a function of frequency for (a) the minimum capacitance

position (b) the maximum capacitance position. The series impedance behaves like an RLC

circuit, and the shunt impedances are capacitive below 10 GHz. The self-resonance frequency is

greater than 20 GHz for the minimum capacitance position and decreases to 11 GHz for the

maximum capacitance position. .................................................................................................... 44

Fig. 3.22. Quality factor as a function of frequency. This plot shows the Q for the maximum

capacitance position. ..................................................................................................................... 47

Fig. 3.23. Plot of series capacitance versus latch position. Error bars indicate the 1-σ standard

deviation between different devices based on 7 measurements. ................................................... 48

Fig. 3.24. Capacitance as a function of actuator voltage. Continuous tuning is possible with the

latch retracted. Hysteresis is caused by capacitive beams sticking together as they are being

pulled apart.................................................................................................................................... 48

Fig. 3.25. Capacitance as function of DC bias voltage. With the latch retracted (unlatched),

capacitance beams snap together using less than 5 V. With the latch in place, up to 14 V can be

applied before electrostatic pull-in occurs. ................................................................................... 49

Fig. 3.26. Electrothermal actuator frequency response. The thermal 3 dB frequency limits the

speed of both the gap and latch actuators. .................................................................................... 51

Fig. 3.27. Electrothermal actuator transient response. The 90% rise time is 4.9 ms. .................. 51

Fig. 3.28. Temperature profile of gap-tuning capacitor viewed with quantum infrared

microscope. Voltage is applied to resistors in (a) the gap actuator only (b) the latch actuator only

(c) both the gap and latch actuators. ............................................................................................. 54

Fig. 3.29. Latched capacitance as a function of ambient temperature. While latched in position,

the capacitance remains stable up to 65°C. ................................................................................... 55

Fig. 3.30. Minimum and maximum capacitance as a function of actuation cycles for two DUT‟s.

Maximum capacitance decreased as the variable capacitor was cycled between latch positions. 57

Fig. 3.31. SEM images of mechanical latch after failure (a) zoomed out (b) zoomed in. Repeated

impacts of the latch interface created sub-micron debris on the latch. ......................................... 57

Fig. 4.1. Concept of the actuation method for the switched capacitor. ......................................... 62

ix

Fig. 4.2. Diagram of CMOS-MEMS switched capacitor viewed from above (a) with annotations

(b) with circuit schematic; (c) SEM image of four CMOS-MEMS switched capacitors in parallel.

....................................................................................................................................................... 64

Fig. 4.3. Steady-state thermal circuit for the CMOS-MEMS switched capacitors. ...................... 66

Fig. 4.4. Cross-section of the switched capacitor along the rotor electrode. ................................ 67

Fig. 4.5. Diagram of CMOS-MEMS switched capacitor viewed (a) from above with nominal

layout dimensions (b) from the side with the rotor electrode deflected vertically into minimum

capacitance position. Line A–A’ and line B–B’ show the positions of the cross-sections along the

rotor electrode and stator electrode, respectively. ......................................................................... 68

Fig. 4.6. Normalized parameters as a function of MIM capacitor length. Tuning ratio and

capacitance density are normalized to their respective values for the optimum MIM capacitor

length of 35 µm. ............................................................................................................................ 75

Fig. 4.7. Normalized parameters as a function of actuator beam length. Tuning ratio, capacitance

density, and quality factor are normalized to their respective values for an actuator beam length

of 90 µm to illustrate the tradeoffs necessary for increased tuning ratios. ................................... 76

Fig. 4.8. SEM image of 3-bit digital capacitor. Bits are separated by dummy structures to

improve the temperature uniformity of the electrothermal actuators. Floating electrodes appear

darker due to charging................................................................................................................... 78

Fig. 4.9. Microscope picture of CMOS-MEMS switched capacitors (a) in minimum capacitance

position before actuation (rotor electrodes are deflected out of focus) (b) after electrothermal

actuation (c) in maximum capacitance position after electrostatic actuation. .............................. 79

Fig. 4.10. Profilometer image of bit 3 of the digital capacitor (a) before actuation (b) after

actuation. The rotor beams are not visible when deflected upwards because their angle with

respect to the chip surface is too large for their profile to be captured by the Wyko unless settings

are modified which sacrifice the quality of the image. ................................................................. 79

Fig. 4.11. Microscope image of the 3-bit digital capacitor in state (a) 0 (b) 1 (c) 2 (d) 3 (e) 4 (f) 5

(g) 6 (h) 7. Each capacitive bit is controlled independently to select the desired capacitance. .... 80

Fig. 4.12. S-parameter magnitude as a function of frequency for (a) the minimum capacitance

state (b) the maximum capacitance state. S12 is not plotted because S12 and S21 are equivalent for

passive networks. .......................................................................................................................... 82

Fig. 4.13. Equivalent circuit model in terms of (a) Y-parameters and (b) lumped circuit elements.

Circuit element values are extracted from measured 2-port network parameters. ........................ 82

Fig. 4.14. Lumped impedances as a function of frequency for (a) the minimum capacitance state

(b) the maximum capacitance state. The behavior of |1/(Y11+Y12)| is explained by silicon

remaining beneath the suspended MIM capacitor. The self-resonance frequency is greater than 40

GHz for the minimum capacitance position and decreases to 11.4 GHz for the maximum

capacitance position. ..................................................................................................................... 82

Fig. 4.15. Quality factor as a function of frequency. This plot shows the Q for the maximum

capacitance position with port 2 connected to ground. ................................................................. 84

Fig. 4.16. Plot of series capacitance versus state. Error bars indicate the 1-σ standard deviation

between different devices based on 7 measurements. ................................................................... 85

Fig. 4.17. Plot of series capacitance during an actuation cycle. The x-axis is arbitrary; all

measured points shown were allowed to reach steady-state and maintained for approximately one

minute. “Electrothermal” and “electrostatic” are abbreviated as “ET” and “ES”, respectively. The

plotted data represents a single actuation cycle from a single device and thus may vary over time

or between different devices. ........................................................................................................ 86

Fig. 4.18. Electrothermal actuator frequency response. ................................................................ 87

x

Fig. 4.19. Simulated temperature profile of electrothermal actuator. Symmetry boundary

conditions are applied so the simulation represents an array of many switched capacitors in

parallel........................................................................................................................................... 89

Fig. 4.20. Series capacitance of a 3-bit digital capacitor as a function of ambient temperature. .. 91

Fig. 4.21. SEM images of surface damage caused by repeated temperature cycling at 250°C. The

white boxes indicate the locations of the embedded heating resistors. ......................................... 92

Fig. 4.22. Vertical gap during heating as a function of the number of actuation cycles. A positive

gap indicates that the tip of the rotor electrodes are deflected above the stator electrodes. ......... 93

Fig. 4.23. Diagram of capacitive bit with (a) interwoven actuator beams resulting in large

parasitic capacitance (b) updated topology to reduce parasitic capacitance. ................................ 95

Fig. 4.24. SEM image of 3-bit digital capacitor updated to reduce parasitic capacitance. The

chunk of debris was left in place since manual removal could damage the actuators. ................. 96

Fig. 4.25. Microscope image of the updated 3-bit digital capacitor in state (a) 0 (b) 1 (c) 2 (d) 3

(e) 4 (f) 5 (g) 6 (h) 7. Each capacitive bit is controlled independently to select the desired

capacitance. ................................................................................................................................... 96

Fig. 4.26. S-parameter magnitude as a function of frequency for (a) the minimum capacitance

state (b) the maximum capacitance state. S12 is not plotted because S12 and S21 are equivalent for

passive networks. .......................................................................................................................... 97

Fig. 4.27. Equivalent circuit model in terms of (a) Y-parameters and (b) lumped circuit elements.

Circuit element values are extracted from measured 2-port network parameters. ........................ 97

Fig. 4.28. Lumped impedances as a function of frequency for (a) the minimum capacitance

position (b) the maximum capacitance position. The series impedance behaves like an RLC

circuit, and the shunt impedances are capacitive below 10 GHz. The self-resonance frequency is

greater than 40 GHz for the minimum capacitance position and decreases to 10 GHz for the

maximum capacitance position. .................................................................................................... 97

Fig. 4.29. Quality factor as a function of frequency for the updated digital capacitor. This plot

shows the Q for the maximum capacitance position with port 1 connected to ground. ............... 99

Fig. 5.1. Schematic of phased antenna array. Phase shifters create a variable time delay between

antennas to enable electronic beam steering. .............................................................................. 103

Fig. 5.2. Schematic of distributed MEMS phase shifter (for N = 3 sections) as (a) distributed

components (b) lumped component (c) lumped components with a single shunt capacitances. 104

Fig. 5.3. Diagram of the CMOS-MEMS switched capacitor viewed from above (a) with

annotations (b) with circuit schematic; (c) SEM image of eight CMOS-MEMS switched

capacitors in parallel. .................................................................................................................. 105

Fig. 5.4. Cross-section of the phase shifter (a) along the rotor electrode of a switched capacitor

(b) along a section of transmission line without a switched capacitor........................................ 106

Fig. 5.5. Schematic of 4-bit digital capacitor used in the phase shifter. ..................................... 107

Fig. 5.6: SEM image of phase shifter digital capacitor. The rotor electrodes are vertically

deflected into the minimum capacitance state. “D” indicates dummy bits which are included for

temperature uniformity. .............................................................................................................. 113

Fig. 5.7: SEM image of one CMOS-MEMS phase shifter section. ............................................ 114

Fig. 5.8: SEM image of the CMOS-MEMS phase shifter composed of eight phase shifter

sections. ....................................................................................................................................... 114

Fig. 5.9: Microscope image of CMOS-MEMS digital capacitor (a) before actuation (b) after

actuation in state 10 (1010) with bits 4 and 2 turned on. ............................................................ 115

xi

Fig. 5.10. S-parameter magnitude as a function of frequency for (a) the minimum capacitance

state (b) the maximum capacitance state. S12 is not plotted because S12 and S21 are equivalent for

passive networks. ........................................................................................................................ 116

Fig. 5.11. Equivalent circuit model in terms of (a) Z-parameters and (b) lumped circuit elements.

Circuit element values are extracted from measured 2-port network parameters. ...................... 117

Fig. 5.12. Lumped impedances as a function of frequency for (a) the minimum capacitance

position (b) the maximum capacitance position. The series impedance behaves like an RLC

circuit, and the shunt impedances are capacitive below 10 GHz. The self-resonance frequency is

greater than 40 GHz for the minimum capacitance position and decreases to 10 GHz for the

maximum capacitance position. .................................................................................................. 117

Fig. 5.13. Quality factor as a function of frequency for the digital capacitor used in the phase

shifter. This plot shows the Q for the maximum capacitance position with port 2 left floating. 119

Fig. 5.14: Capacitance of phase shifter digital capacitor as a function of state. State 3 (0011)

indicates that the two least significant bits are turned on. .......................................................... 120

Fig. 5.15: Measured phase shift as a function of frequency for all 16 states. Phase shift is negative

because the time delay increases with increasing capacitance. ................................................... 121

Fig. 5.16: Measured insertion loss as a function of frequency for all 16 states. ......................... 121

Fig. 5.17: Measured reflection as a function of frequency for all 16 states. ............................... 122

Fig. 5.18. S-parameter magnitude as a function of frequency for (a) the minimum phase shift

state (b) the maximum phase shift state. S12 is not plotted because S12 and S21 are equivalent for

passive networks. ........................................................................................................................ 123

Fig. 5.19: Comparison of passive phase shifters. The average insertion loss is plotted versus the

minimum operating frequency. ................................................................................................... 124

Fig. A.1. Layout view of (a) open test structure (b) short test structure (c) DUT. Measurements of

the open and short test structures are necessary to remove the parasitic effects of the probe pads

using open-short de-embedding. „G‟ and „S‟ represent „ground‟ and „signal‟, respectively. ..... 143

Fig. A.2. Equivalent circuit model in terms of (a) Y-parameters and (b) lumped circuit elements.

Circuit element values are extracted from measured 2-port network parameters. ...................... 147

Fig. A.3. Lumped impedance magnitude as a function of frequency for the maximum capacitance

position. The extracted model is compared with measured data. ............................................... 147

Fig. A.4. Series capacitance as a function of frequency. The extracted model is compared with

measured data.............................................................................................................................. 148

Fig. A.5. Series resistance as a function of frequency. The extracted model is compared with

measured data.............................................................................................................................. 148

Fig. A.6. Shunt capacitances as a function of frequency. The extracted model is compared with

measured data.............................................................................................................................. 149

Fig. A.7. Quality factor as a function of frequency. The extracted model is compared with

measured data.............................................................................................................................. 150

Fig. A.8. S-parameter magnitude as a function of frequency. The extracted model is compared

with measured data. S12 is not plotted because S12 and S21 are equivalent for passive networks.

..................................................................................................................................................... 151

Fig. A.9. Equivalent circuit model in terms of (a) Z-parameters and (b) lumped circuit elements.

Circuit element values are extracted from measured 2-port network parameters. ...................... 152

Fig. A.10. Lumped impedance magnitude as a function of frequency. The extracted model is

compared with measured data. .................................................................................................... 152

Fig. A.11. Capacitance to ground as a function of frequency. The extracted model is compared

with measured data. .................................................................................................................... 153

xii

Fig. A.12. Shunt resistance as a function of frequency. The extracted model is compared with

measured data.............................................................................................................................. 153

Fig. A.13. Series resistances as a function of frequency. The extracted model is compared with

measured data.............................................................................................................................. 154

Fig. A.14. Series inductances as a function of frequency. The extracted model is compared with

measured data.............................................................................................................................. 155

Fig. A.15. Quality factor as a function of frequency. The extracted model is compared with

measured data.............................................................................................................................. 156

Fig. A.16. S-parameter magnitude as a function of frequency. The extracted model is compared

with measured data. S12 is not plotted because S12 and S21 are equivalent for passive networks.

..................................................................................................................................................... 156

xiii

Chapter 1.

Introduction

This chapter introduces the subject of CMOS-MEMS variable capacitors by outlining the

motivation and goals of this work. Section 1.1 proposes multi-band radio as the motivation for

developing MEMS variable capacitors. Section 1.2 explains why CMOS-MEMS variable

capacitors are necessary when semiconductor variable capacitors are readily available. The thesis

statement is presented in Section 1.3, and the contributions of this work are listed in Section 1.4.

1.1. Motivation

Consumer radio systems are transmitting and receiving data over an increasing number of

frequency bands. Modern cellular phones use four different frequency bands for transmitting

voice and a fifth frequency band for wireless local area networking [1]. Multiple frequency bands

are required to provide different functions and so that the total bandwidth is large enough to

accommodate many users. Multi-band operation is currently achieved by using multiple narrowband circuits, each of which is capable of operation over a single frequency band. For example,

dual- and quad-band receivers simply include two or four low-noise amplifiers, respectively [2],

[3]. Similarly, dual-band and quad-band transmitters require two or four power amplifiers,

respectively [4], [1]. As the trend for operation over more frequency bands continues, the current

implementation of multi-band radio systems requires more circuits and thus becomes more

expensive.

To reduce the cost of multi-band radio, there are two possible solutions: wide-band circuits

and reconfigurable circuits. Wide-band circuits with a bandwidth spanning multiple frequency

bands would eliminate the need for multiple circuits, but the performance of wide-band circuits

is inferior to that of narrow-band circuits. The ideal solution is reconfigurable circuits, which are

Chapter 1: Introduction

1

tunable narrow-band circuits capable of reconfiguration between different frequency bands.

Reconfigurable circuits have the potential to eliminate the need for multiple circuits while

providing performance typical of narrow-band circuits.

The performance of reconfigurable circuits has been limited by the available tunable

devices. Because many devices must be integrated onto a single CMOS chip to minimize cost,

the tunable devices available at RF are semiconductor variable capacitors. These variable

capacitors perform poorly when designed for large tuning capabilities. To enable reconfigurable

circuits for multi-band radio, this work proposes to use MEMS variable capacitors.

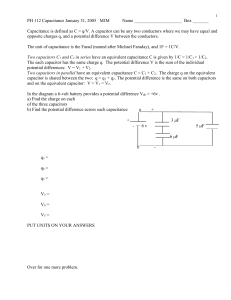

Gap Tuning

d

g–d

C

0 LW

g d

Area Tuning

d

C

Movable Dielectric

Metal

L–d

d

0 L d W

g

C

L–d

0 d r L d W

g

Dielectric (εr > 1)

All objects

have width W

into the page

(a)

(b)

(c)

Fig. 1.1. Diagram of capacitance tuning by changing the (a) gap (b) overlap area (c) dielectric. All capacitors have

length L, width W, and gap g before part of the structure undergoes displacement d. Capacitance calculations ignore

the effects of fringing fields.

1.2. MEMS Variable Capacitors

MEMS variable capacitors are electrical devices whose capacitance value is controlled

through mechanical actuation. Capacitance tuning is accomplished by mechanically changing the

gap [5], overlap area [6], or dielectric [7] between the capacitive electrodes (see Fig. 1.1).

Depending on the nature of the actuation, the tuning range can be continuous from minimum

capacitance to maximum capacitance or consist of a set of achievable discrete capacitance values.

Devices with continuous tuning range are often referred to as variable capacitors or varactors

Chapter 1: Introduction

2

whereas devices with two states, on and off, are referred to as capacitive switches or switched

capacitors. Devices that achieve many discrete capacitance values by using many independently

controlled switched capacitors are referred to as digital capacitors.

1.2.1. Characteristics of MEMS Variable Capacitors

The electrical performance of MEMS variable capacitors is described by three primary

metrics. The tuning ratio, TR, is the ratio of maximum capacitance, Cmax, to minimum

capacitance, Cmin.

TR

C max

C min

.

(1.1)

The quality factor, Q, is the ratio of energy stored to energy dissipated when charge is stored on

a capacitor. Typically, Q is limited by the series resistance, Rs, of the metal path.

Q

1

CRs

,

(1.2)

where ω is the electrical frequency and C is the capacitance. The self-resonance frequency, ωres,

is the frequency at which the variable capacitance resonates due to parasitic inductance, L.

res

1

LC

,

(1.3)

Above the self-resonance frequency, the total imaginary impedance is inductive meaning that the

device no longer functions as a capacitor. All three of these metrics should be maximized to

optimize a variable capacitor.

Several other characteristics of MEMS variable capacitors are also important. Capacitance

density is the ratio of the maximum capacitance to the device area, which is important when the

variable capacitor is monolithically integrated with other devices. The actuation voltage or

Chapter 1: Introduction

3

actuation power is the specified voltage or power required for mechanical actuation. Switching

time is the time required to change the capacitance, which can differ depending on the state of

the variable capacitance. For example, the turn-on time of switched capacitors is often different

from the turn-off time. Reliability is the measure of the lifetime of a variable capacitor, often

characterized by the number of actuation cycles achieved before failure. Power handling is

defined as the maximum power that can be transmitted through the variable capacitors, typically

assuming a 50-Ω source and load impedance. Power handling is limited by either the maximum

voltage or maximum current a variable capacitor can tolerate. Linearity refers to the relationship

between the voltage applied across the capacitor terminals and the stored electrical charge.

Ideally, the charge increases linearly with applied voltage, but all capacitors are nonlinear to

some extent. The linearity of a variable capacitor is often characterized by measuring the 3rdorder input-referred intercept power (IIP3) of a circuit using that variable capacitor.

The mechanical actuation of MEMS variable capacitors can be electrostatic, electrothermal,

piezoelectric, or magnetic. Actuation characteristics vary according to the particular actuator

design, but several generalizations can be stated about the actuation types that hold true for most

designs. Electrostatic actuation produces small displacements (< 10 µm) using high actuation

voltages (> 10 V). The other three types of actuation, electrothermal actuation, piezoelectric

actuation, and magnetic actuation, are at first glance superior because those types produce large

displacements (> 10 µm) using low actuation voltages (< 10 V). Large displacements are

required for high tuning ratios, and low actuation voltages are desirable so that the variable

capacitor can be easily controlled. However, piezoelectric actuation and magnetic actuation are

limited because those two types require piezoelectric and magnetic materials, respectively, which

are difficult to integrate with semiconductors. In contrast, electrostatic actuation and

Chapter 1: Introduction

4

electrothermal actuation can be used with any MEMS technology because those two types of

actuation only require materials that are electrically conductive. Electrothermal actuation requires

power for heating, typically on the order of milliwatts, and the switching time is limited by the

thermal time constant, typically on the order of milliseconds. Because electrical time constants

are on the order of nanoseconds, the switching time of electrostatic actuation is limited only by

the mechanical response, typically on the order of microseconds. Electrostatic actuation is by far

the most popular type of MEMS actuation because the choice of materials is virtually unlimited,

the power consumption is negligible, and the switching time is fast.

1.2.2. Advantages of MEMS Variable Capacitors

Because semiconductor variable capacitors are more mature than MEMS variable

capacitors, semiconductor variable capacitors must be discussed to illustrate the advantages of

MEMS variable capacitors. The three types of semiconductor variable capacitors available in a

standard CMOS process are the diode varactor, the metal-oxide-semiconductor (MOS) varactor,

and the switched metal-insulator-metal (MIM) capacitor. All three of these types have switching

times on the order of nanoseconds and large capacitance densities (> 100 pF/mm2). The diode

varactor and the MOS varactor have high Q‘s (> 100 at 1 GHz), but the tuning ratios of these

varactors are small (< 5:1). Both varactors are fundamentally nonlinear devices because the

varactors only have two electrical terminals such that the applied voltage directly affects the

capacitance value. The switched MIM capacitor, which consists of a MIM capacitor in series

with the channel of a metal-oxide-semiconductor field-effect transistor (MOSFET), has a third

terminal, the gate of the MOSFET, which controls the capacitance and thus is more linear.

Switched MIM capacitors can be designed for large tuning ratios (> 5:1), but Q decreases as the

Chapter 1: Introduction

5

tuning ratio increases. This tradeoff occurs because, for large tuning ratios, the MOSFET must be

small to minimize parasitic capacitance, but a small MOSFET has high channel resistance, which

degrades the Q. None of the semiconductor variable capacitors can simultaneously achieve both

large tuning ratio (> 10:1) and high Q (> 100 at 1 GHz).

TABLE 1.1: VARIABLE CAPACITOR CHARACTERISTICS

Parameter

Switched MIM

Capacitor

University of

University of

University of

Imperial

California– Los California – San California – San College London

Angeles [8]

Diego [9]

Diego [10]

[11]

MEMS

MEMS

MEMS

MEMS

8.6 pF

192 fF

1.00 pF

600 fF

270 fF

63 fF

51 fF

60 fF

Type

CMOS

Cmax

1.11 pF

Cmin

111 fF

Shunt Tuning

10:1

31:1

3.0:1

Ratio

Q at 1 GHz*

9

9

1940

FoM

90

279

5820

(TRshunt*Q)

Self-Resonance

NA

2.7 GHz

> 30 GHz

Frequency*

Capacitance

1000 pF/mm2

NA

≈ 9.5 pF/mm2

Density

Switching

MOSFET

Electrostatic

Electrostatic

Method

Tuning Range

Digital

Analog

Digital

Switching Time

~ 1 ns

NA

< 0.5 µs

Actuation

3.3 V

40 V

32 V

Voltage

Actuation

≈ 0**

≈ 0**

≈ 0**

Energy for 1 pF

* The parameter corresponds to the maximum capacitance state.

* *The power consumed for actuation is negligible.

19.6:1

10:1

265

352

5194

3520

> 10 GHz

17 GHz

≈ 12.8 pF/mm2

12 pF/mm2

Electrostatic

Electrostatic

Digital

8 µs

Analog

NA

40 V

30 V

≈ 0**

≈ 0**

MEMS variable capacitors have demonstrated several advantages over semiconductor

variable capacitors. For comparison, Table 1.1 presents the performance of several MEMS

variable capacitors along with that of a switched MIM capacitor simulated for the 0.35 µm

BiCMOS process from TowerJazz Semiconductor. First, MEMS variable capacitors can provide

the combination of large tuning ratio (> 5:1) and high Q (> 100 at 1 GHz). Large tuning ratios are

made possible by the mechanical displacements produced by MEMS actuators, and the Q‘s are

high because MEMS variable capacitors are composed entirely of metal. Semiconductor devices

Chapter 1: Introduction

6

are limited in Q due to their close proximity to and inclusion of silicon, which is a poor electrical

conductor at RF. The figure of merit (FoM) introduced in Table 1.1 is the product of the shunt

tuning ratio and the Q at 1 GHz for the maximum capacitance.

FoM TRshunt * Q .

(1.4)

Second, MEMS variable capacitors are highly linear because mechanical motion is attenuated

beyond the mechanical resonance frequency, which is typically less than 10 MHz [12]. As a

result, the variable capacitance is not significantly affected by the applied RF voltage. Third, the

power handling of MEMS variable capacitors is often excellent because large voltages (> 10 V)

can be applied without causing electrical breakdown [13].

Due to their advantages, MEMS variable capacitors have been applied to both enhance

existing RF circuits and enable new applications. MEMS capacitive switches proposed to serve

as transmit-receive switches have demonstrated reduced insertion loss when compared with stateof-the-art semiconductor switches [14]. Phase shifters for phased antenna arrays have been

improved using either MEMS variable capacitors or MEMS capacitive switches [15]. MEMS

variable capacitors have been combined with fixed inductors or transmission lines to form highQ tunable resonators for a number of applications. The phase noise of voltage controlled

oscillators has been improved by replacing the semiconductor variable capacitors with MEMS

variable capacitors [16], [17]. Reconfigurable filters have been enabled by the large tuning ratios

available with MEMS variable capacitors [18]. Antenna tuners have been developed to alleviate

source-load mismatch between power amplifiers and antennas [19]. Using this work, narrowband RF circuits, specifically low-noise amplifiers [20] and power amplifiers [21], have been

made reconfigurable by MEMS variable capacitors.

However, there are drawbacks to MEMS variable capacitors. When compared with

Chapter 1: Introduction

7

semiconductor variable capacitors, MEMS variable capacitors are slow, typically switching in

milliseconds or microseconds as opposed to nanoseconds. Capacitance density is low

(< 100 pF/mm2) due to the large dimensions of the MEMS structure, which are typically on the

order of tens or hundreds of microns. For electrostatically actuated MEMS, power consumption

is negligible but the required voltage is often large, on the order of tens of volts [13]. The

opposite is true of electrothermally actuated MEMS; the required voltage is small, on the order of

volts, but power consumption is significant, on the order of tens of milliwatts [22]. Reliability is

not guaranteed since RF MEMS can fail from dielectric charging [23], mechanical creep or

fatigue, or from degradation related to repeated mechanical contact [24].

Fortunately, many of these drawbacks can either be mitigated or tolerated by the target

applications. Faster switching times are desired but not explicitly required for antenna tuners and

many reconfigurable networks. The large area consumption of MEMS is acceptable because, to

form resonators, MEMS variable capacitors are often combined with spiral inductors or

transmission lines, both of which have dimensions on the order of hundreds of microns or larger.

Large voltages for electrostatic actuation can be provided by on-chip CMOS charge pumps if

high voltage CMOS is available [25]. Mechanical latches or electrostatic force [26] can be used

to eliminate the static power consumption of electrothermal actuation [27]. Research on the

reliability of RF MEMS has yielded methods to mitigate dielectric charging [28] and ultimately

achieve billions of actuation cycles without failure [9].

1.2.3. Monolithic Integration

Despite their excellent performance, MEMS variable capacitors are not widely used in RF

circuits because most MEMS variable capacitors are not monolithically integrated with CMOS.

Chapter 1: Introduction

8

Monolithic integration is required because the inclusion of MEMS variable capacitors into RF

circuits as discrete components is simply too expensive to warrant their use. This requirement is

challenging because MEMS fabrication is complicated by the need for integration.

The structural and sacrificial layers necessary for MEMS require additional processing

beyond that of a standard CMOS process, especially when integration with CMOS is required.

Low-temperature micromachining can be used to fabricate MEMS devices directly on top of an

existing CMOS process [29]. Alternatively, MEMS can be fabricated on a separate substrate and

flip-chip bonded onto a CMOS chip [30], [31]. Both methods of integration grant the MEMS

designer the freedom to select the materials and layer thicknesses, but this freedom comes at the

cost of additional lithography steps, which ultimately increases the cost of any system using such

integrated MEMS.

To solve this problem, the post-CMOS micromachining process in [32], hereafter called the

―CMOS-MEMS process‖ can be used for monolithic integration of MEMS devices without using

additional lithography steps. The CMOS-MEMS process uses maskless, post-CMOS etching to

create MEMS devices composed of the metal-dielectric stack of a foundry CMOS process. The

resulting MEMS structure can consist of multiple metal layers connected in parallel for low

resistance. The air gap between the MEMS structure and the remaining silicon substrate is

approximately 50 µm, which minimizes parasitic capacitance to the resistive silicon. Polysilicon

resistors can be embedded within the MEMS structure to act as heaters for low-voltage

electrothermal actuation [22]. These features make CMOS-MEMS a natural choice for

integrating MEMS variable capacitors in a low-cost manner.

1.3. Thesis Statement

MEMS variable capacitors have demonstrated significant advantages over semiconductor

Chapter 1: Introduction

9

variable capacitors but are not cost-effective if included in electrical systems as discrete

components. The typical methods available for monolithically integrating MEMS variable

capacitors with CMOS require additional lithography steps, which increases cost. The CMOSMEMS process is an alternative method for integrating MEMS with CMOS without using

additional lithography steps. Thus, using the CMOS-MEMS process, CMOS-MEMS variable

capacitors can be designed with performance comparable to that of other integrated

MEMS variable capacitors and enable the design of low-cost reconfigurable RF circuits.

To assess the performance of CMOS-MEMS variable capacitors, devices were designed,

fabricated, and characterized. The electrical characteristics were measured to calculate the tuning

ratio, Q, and self-resonance frequency. Actuation methods were tested to determine the switching

times along with voltage and power requirements. The effects of repeated actuation were

analyzed to determine reliability. Results are compared with that of other integrated MEMS

variable capacitors.

To show that CMOS-MEMS variable capacitors enable the design of reconfigurable RF

circuits, a CMOS-MEMS phase shifter was designed, fabricated, and characterized. The

electrical characteristics were measured to calculate the phase shift and insertion loss. Results are

compared with that of other MEMS phase shifters.

1.4. Contributions

The first contribution of this work, the design and characterization of a CMOS-MEMS

electrothermal gap-tuning capacitor, is presented in Chapter 3. The gap-tuning capacitor uses

lateral electrothermal actuation to control the capacitive gap between interdigitated electrodes. A

mechanical latch, also controlled by electrothermal actuation, was used to maintain the capacitive

Chapter 1: Introduction

10

gap without consuming static power for heating. The gap-tuning capacitor requires 4 V and 15

mW for electrothermal actuation and can be reconfigured in 30 ms. The average measured tuning

ratio is 4.9:1, and the measured Q for the maximum capacitance state is 80 at 1 GHz. Reliability

testing demonstrated that the lifetime exceeds millions of actuation cycles.

Chapter 4 presents the second contribution of this work, the design and characterization of

CMOS-MEMS digital capacitors. The digital capacitors are composed of many independently

controlled CMOS-MEMS switched capacitors, which can be toggled on or off using a

combination of vertical electrothermal and lateral electrostatic actuation. Electrostatic force is

used to maintain the maximum capacitance state without consuming static power. The digital

capacitors can be switched in 1 ms using 4 V for electrothermal actuation and 20 V for

electrostatic actuation. The average measured tuning ratio is 61:1, and the measured Q for the

maximum capacitance state is 369 at 1 GHz. Reliability testing demonstrated millions of

actuation cycles successfully but revealed a drift in the actuation characteristics after 10 million

cycles. These digital capacitors represent the state-of-the-art for CMOS-MEMS variable

capacitors.

The design and characterization of a 4-bit CMOS-MEMS phase shifter for phased antenna

arrays is presented in Chapter 5 as the third contribution of this work. The phase shifter is

composed of a micromachined transmission line periodically loaded with CMOS-MEMS digital

capacitors. The digital capacitors are modified to achieve a Q of 18.8 at 30 GHz for the

maximum capacitance state and a tuning ratio of 7.2:1. Measured results demonstrate the

required phase shift of 337.5° at 32 GHz with an average insertion loss of 2.9 dB. This phase

shifter is the first RF MEMS phase shifter to be monolithically integrated with CMOS.

Chapter 1: Introduction

11

Chapter 2.

CMOS-MEMS Background

This chapter presents the CMOS-MEMS process that is used to fabricate the MEMS

variable capacitors presented in this work. Section 2.1 describes the process flow along with

several characteristics of CMOS-MEMS structures relevant to variable capacitors. Section 2.2

discusses how the CMOS-MEMS process is used to create both lateral and vertical

electrothermal actuators.

2.1. CMOS-MEMS Process

The CMOS-MEMS process is used to fabricate MEMS that are monolithically integrated

with standard CMOS. The process can be applied to any CMOS technology provided that the

placement of metal layers can be controlled by layout. CMOS technologies with strict metal fill

requirements cannot be used for CMOS-MEMS since the metal fill blocks the post-CMOS

etching. The CMOS-MEMS process can be applied to CMOS from different foundries and from

different technology generations, such as 0.35 µm or 0.18 µm. The CMOS-MEMS devices

fabricated for this work all use the 0.35 µm BiCMOS process from TowerJazz. This CMOS

process provides four aluminum metal layers, one thick top metal and three thin metals, one

polysilicon layer, and tungsten vias. The minimum width and spacing for the thick top metal is

2.6 µm and 1.9 µm, respectively. The minimum width and spacing for the three thin metals are

both 0.5 µm.

2.1.1. Process Flow

The CMOS-MEMS process consists of maskless, post-CMOS etching to create MEMS

structures from the metal-dielectric stack of a standard CMOS process (see Fig. 2.1) [32]. First,

Chapter 2: CMOS-MEMS

12

the exposed oxide is anisotropically etched using a CHF3/CF4/O2 reactive ion etch (RIE). During

the oxide etch, the top-most metal layer acts as a mask both to define the resulting MEMS

structure and to protect devices such as transistors which require the silicon substrate. The oxide

etch exposes the silicon surface in areas which contain no metal. Next, the exposed silicon is

anisotropically etched using an SF6/O2 RIE. This anisotropic silicon etch is necessary to create a

large vertical air gap (≈ 50 µm) between the resulting MEMS structure and the bottom of the

silicon etch pit. Finally, the silicon is etched isotropically using SF6 plasma to release the

resulting MEMS structures from the substrate. The isotropic silicon etch is timed such that

narrow structures are undercut while wide structures remain anchored to the substrate (see Fig.

2.2).

Key:

Metal 1

(a)

(b)

(c)

(d)

Metal 2

Metal 3

Metal 4

Oxide

Via

Silicon

Fig. 2.1. Cross-section of the CMOS-MEMS process flow (a) beginning with CMOS chip (b) after the vertical oxide

etch (c) after the vertical silicon etch (d) after silicon release etch.

Chapter 2: CMOS-MEMS

13

50 µm

20 µm

(a)

(b)

Fig. 2.2. SEM image of (a) 20 µm squared released from the substrate (b) 60 µm square anchored to the substrate.

These test structures were fabricated using the 0.18 µm BiCMOS process from TowerJazz.

2.1.2. CMOS-MEMS Characteristics

The CMOS-MEMS process is very flexible because a wide variety of beams can be created.

CMOS-MEMS beams can consist of a single metal layer, such as a metal-1 beam, or multiple

metal layers, such as a metal-321 beam. Beams consisting of multiple metal layers can carry

multiple independent signals or be connected in parallel to serve as low-resistance wires. Both

vias and polysilicon can be embedded within the CMOS-MEMS beams. Embedded polysilicon is

encased in oxide and thus does not etch during the isotropic silicon etch. Fig. 2.1(d) shows three

examples of released CMOS-MEMS beams. The left beam is a metal-321 beam with metal 1 and

2 offset layers. The middle beam is a metal-4321 beam with vias and polysilicon. The right beam

is a metal-1 beam.

Several characteristics of the CMOS-MEMS process are particularly beneficial for RF

MEMS. First, the large vertical air gap (≈ 50 µm) below the MEMS structure minimizes parasitic

capacitance to the silicon substrate. Since silicon is a poor conductor at RF, coupling to the

silicon must be avoided to maximize the Q of CMOS-MEMS variable capacitors. Second,

Chapter 2: CMOS-MEMS

14

CMOS processes often include a thick metal layer to minimize the series resistance of on-chip

spiral inductors. This thick metal layer is useful for minimizing the series resistance of variable

capacitors. Third, polysilicon resistors can be embedded in the CMOS-MEMS beams to enable

electrothermal actuation. These resistors allow the temperature of electrothermal actuator beams

to be controlled using an applied voltage.

During the vertical oxide etch, a passivation layer is deposited on the side-walls of the

CMOS-MEMS beams. This side-wall polymer is required for the oxide etch to be anisotropic.

The polymer layer also prevents the titanium-tungsten adhesion layers, which are deposited

above and below the aluminum metal layers as part of the CMOS process, from etching during

the silicon release etch. Without sufficient side-wall polymer, the aluminum metal layers can

delaminate and peel away from the oxide. The side-wall polymer is a dielectric material of

unknown relative permittivity. Since observations of the thickness in SEM images approximately

match the thickness calculated from capacitance measurements, the relative permittivity is

expected to be near unity. The thickness of the side-wall polymer determines the effective air gap

between CMOS-MEMS beams pushed into mechanical contact (≈ 0.2 µm). The air gap is

referred to as effective because there is no actual air gap, simply a gap containing side-wall

polymer whose permittivity is assumed to be equal to that of air. This effective air gap limits the

maximum capacitance per unit length between two CMOS-MEMS beams. Note that CMOSMEMS beams pushed into mechanical contact do not short circuit. Shorting would be

unexpected because aluminum has a native oxide that prevents electrical contact. The side-wall

polymer is believed to further help prevent electrical breakdown. Two CMOS-MEMS beams in

mechanical contact can withstand greater than 30 V before electrical breakdown occurs.

Electrical breakdown typically occurs when more than 50 V has been applied. Breakdown

Chapter 2: CMOS-MEMS

15

destroys the MEMS structures unless the current is limited by a resistor.

After the silicon release etch, all CMOS-MEMS beams curl vertically with a radius of

curvature specific to their metal-dielectric stack. Because beams composed of multiple metal and

dielectric layers are thicker, these beams curl much less than those composed of a single layer of

metal and dielectric. Metal-1 beams can be used to achieve large vertical deflections whereas

metal-4321 beams can be used when vertical curling is unwanted. Most beams curl up away from

the silicon, but the direction depends on the particular CMOS process. Because metal and

dielectric have different temperature coefficients of expansion (TCE), the stress difference

between the two materials, and hence the radius of curvature, is temperature dependent.

CMOS-MEMS beams are prone to another type of curling, referred to as unintended lateral

curling. Unintended lateral curling is fundamentally different from the vertical curling associated

with residual stress because this curling occurs even for beams with symmetric cross-sections.

For example, a metal-1 beam has an asymmetric cross-section for the purpose of vertical curling

because the beam consists of metal on top and dielectric on bottom. Thus vertical curling is

expected. The metal-1 beam has a symmetric cross-section for the purpose of lateral curling

because the beam cross-section is uniform in the lateral direction. Thus lateral curling is not

expected. Yet the fact remains that all CMOS-MEMS beams curl laterally, even when such

curling is not intended.

Unintended lateral curling has been observed in many CMOS-MEMS devices and occurs to

a greater extent for beams which are long and narrow. The cause of this curling is unknown

because the cross-sections of the affected beams are symmetrical such that there is no apparent

reason for curling in one direction or the other. Several theories exist to explain this curling.

Because beams with the same local geometry on the same die curl the same direction, the

Chapter 2: CMOS-MEMS

16

problem may be caused by the CMOS-MEMS process. Further optimization of the process, such

as a reduction in the thickness of the sidewall polymer, has been theorized to reduce the curling

but has not yet been demonstrated. Misalignment of the metal layers may contribute to

unintended lateral curling but cannot be solely responsible since beams composed of only a

single metal layer still curl.

2.2. Electrothermal Actuation

Electrothermal actuation produces mechanical displacements using the thermal expansion of

materials. The actuation is controlled by a voltage applied to a resistor, which causes electrical

power to be dissipated as heat. That heat causes a temperature change resulting in thermal

expansion. The electrothermal actuators used in this work are thermal bimorphs or, if the

actuators include more than two layers, thermal multi-morphs. Thermal bimorphs are beams that

consist of two materials with different temperature coefficients of expansion (TCE). Neglecting

the thin (< 100 nm) titanium-tungsten adhesion layers, the materials used in this work are

aluminum, which has a TCE of 23.1 µK-1, and oxide, which has a TCE of 0.5 µK-1 [33]. Because

the TCE are different, any change in temperature causes a difference in mechanical stress

between the two materials. This stress difference results in a temperature-dependent bending

moment applied along the length of a beam, which causes the beam to curl in a circular arc.

As discussed in Section 2.1.2, all CMOS-MEMS beams, thermal bimorphs included, deflect

at room temperature according to the particular metal-dielectric stack. This vertical deflection

occurs immediately after the beams are released from the substrate and is thus referred to as the

self-assembly displacement. This displacement is caused by residual stress in the CMOS

materials after fabrication, so the magnitude and direction of the displacement depends on the

Chapter 2: CMOS-MEMS

17

CMOS process. Heating the beams above room temperature typically produces displacement in

the opposite direction of self-assembly. The temperature to which the beams must be heated to

reduce the total displacement to zero is defined as the zero-stress temperature. For the 0.35 µm

BiCMOS process used in this work, the zero-stress temperature is approximately 180°C.

The analysis necessary to calculate the temperature-dependant deflection of thermal multimorphs is presented in [22]. Consider a simple thermal bimorph with length L and width w that

consists of one layer of metal with thickness hm on top one layer of oxide with thickness ho.

Assuming that the position of the neutral axis is near the metal-oxide interface, [22] calculates

the vertical displacement at the tip, z(L), according to the dimensions of the bimorph.

z L

wL2

4EI eff

o ho

2

m hm 2 ,

(2.1)

where (EI)eff is the effective flexural rigidity and σo and σm represent the mechanical stress in the

oxide and metal, respectively. The mechanical stress results from thermal expansion and thus

depends on the change in temperature, ∆T.

ET ,

(2.2)

where α is the TCE and E is the Young‘s modulus of the material. The change in temperature is

relative to the zero-stress temperature, T0.

E T0 Ta ,

(2.3)

where Ta is the temperature of the actuator beam. Substituting (2.3) into (2.1) yields the vertical

displacement as a function of the actuator beam temperature.

zL

wL2

4EI eff

o E o ho

2

m E m hm 2 T0 Ta ,

(2.4)

The dimensions and material characteristics of the actuator beam cross-section can be lumped

into a single parameter defined as the sensitivity of the actuator beam cross-section, S.

Chapter 2: CMOS-MEMS

18

S

w

4EI eff

o E o ho

2

m E m hm 2

.

(2.5)

This sensitivity simplifies the expression for the vertical displacement of the actuator beam.

zL SL2 T0 Ta ,

(2.6)

Note that once the sensitivity is determined for a particular actuator beam cross-section, the

length of the actuator beam can be scaled to provide the necessary displacement. The radius of

curvature, ρ, is calculated using the length and tip displacement of the actuator beam.

L2

2 z L

,

(2.7)

Experimental results from [22] provided both the zero-stress temperature and the actuator

cross-section sensitivity for a variety of different cross-sections. For the CMOS-MEMS variable

capacitors presented in this work, the actuator beam cross-sections with the largest sensitivity

were chosen to maximize displacement. The length of the actuator beams were determined by

(2.6) or (2.7) to achieve the required displacement or radius of curvature, respectively.

2.2.1. Vertical Electrothermal Actuators

The vertical electrothermal actuators used in this work are metal-1 beams, which closely

resemble ideal thermal bimorphs (see Fig. 2.3). The heating resistor can be distributed along the

length of the actuator beam or lumped at the anchor points. For the 0.35 µm BiCMOS process

used in this work, the direction of the self-assembly displacement is up, away from the silicon,

but this direction can vary according to the particular CMOS process. Measurements of test

structures showed that a 35 µm long actuator beam without polysilicon deflected by 1.30 µm at

room temperature (25°C). Using (2.7) the radius of curvature resulting from the self-assembly

displacement was calculated to be 471 µm. This calculated radius of curvature is used in the

Chapter 2: CMOS-MEMS

19

design of the digital capacitor presented in Section 4.4. Assuming that the zero-stress temperature

for this actuator is 180°C, the sensitivity of the actuator beam cross-section was calculated to be

6.84 m-1K-1 using (2.6).

Side View

Cross-sections

Self-assembly displacement due

to residual stress

No displacement after heating

to the zero-stress temperature

Key:

Metal 1

Actuator beam without

polysilicon resistor

Actuator beam with polysilicon

resistor

Oxide

Silicon

Fig. 2.3. Diagram of a vertical electrothermal actuator beam. The polysilicon resistor for heating can either be

lumped near the anchor point or distributed along the length of the actuator beam.

2.2.2. Lateral Electrothermal Actuators

The lateral electrothermal actuators used in this work are metal-321 beams with metal-2 and

metal-1 offset to one side of the beam (see Fig. 2.4). The lateral electrothermal actuator beams

are far from ideal thermal bimorphs since both the top metal and most of the oxide must span the

width of the actuator beam. These thermal multi-morphs operate according to the same principles

as a thermal bimorph except that only the offset metal layers contribute a temperature-dependent

stress difference that causes displacement. If the offset metal layers are confined to one side of

the actuator beams, the lateral actuator beams will curl in a circular arc similar to the vertical

electrothermal actuator beams. This type of curling is undesirable for many applications since the

non-zero angle at the tip prevents many actuator beams from being connected in parallel to drive

Chapter 2: CMOS-MEMS

20

a single structure. To achieve a zero angle at the tip, the offset metal layers are switched to the