Course Outline Basic Concepts in RF Design Low

advertisement

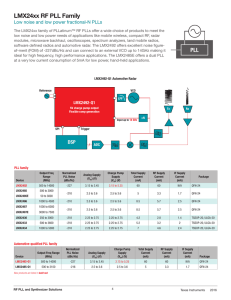

Course Outline Basic Concepts in RF Design Low-Noise Amplifiers Mixers Oscillators Phase-Locked Loops Basic Concepts Most synthesizers emply “phase locking” to achieve high frequency accuracy. In its simplest form, a Phase Locked Loop (PLL) is a negative feedback loop consisting of “phase detector” (PD) voltage controlled oscillator (VCO) Phase Detector A PD is a circuit that senses two periodic inputs and produces an output whose average value is proportional to the difference between the phases of the inputs. The input/output characteristic of the PD is ideally a straight line, with a slope called the “gain” and denoted by KPD (V/rad). In practice, the characteristic may not be linear or even monotonic. If the two inputs have the same frequency the phase difference is constant. Phase Detector An Exclusive-OR (XOR) gate can serve this purpose. It generates pulses whose width is equal to ∆ϕ. The circuit produces pulses at both the rising edge and the falling edge of the inputs. Phase Detector If the two inputs have different frequencies the phase difference changes with time The input with a higher frequency, x2(t), accumulates phase faster than x1(t), thereby changing the phase difference, ∆Φ. The output waveform displays a “beat” behavior having a frequency equal to the difference between the input frequencies. Type-I PLLs: Alignment of a VCO’s Phase Consider a VCO oscillates at the same nominal frequency of an ideal reference but with a phase difference subjected to fluctuations. It is desirable to maintain fixed the phase difference For example, to null the phase difference, we must change the frequency of the VCO (t0). allow the VCO to accumulate phase faster (or more slowly) than the reference so that the phase error vanishes. change the frequency back to its initial value (t1) Simple PLL and Loop Filter A PD comparing the VCO phase and reference phase can be used to determine the time at which the phase error reaches zero In such design the phase error cannot be arbitrarily small to avoid instability The PD produces repetitive pulses at its output, modulating the VCO frequency and generating large sidebands. Interpose a low-pass filter (called “loop filter”) between the PD and the VCO to suppress these pulses. We call this circuit a “Phase-Locked Loop” (PLL). Simple PLL: Phase Locking In a voltage-domain buffer, if the open-loop gain is sufficiently high, the output tracks the input with an offset difference. In the same way in a PLL the phase of the output tracks the phase of the input if the open-loop gain is high We say the loop is “locked” if ϕout(t)-ϕin(t) is constant with time. An important and unique consequence of phase locking is that the input and output frequencies of the PLL are exactly equal. The phase difference ϕout(t)-ϕin(t) depends on the frequency Due to the finite open-loop gain a “frequency-locked loop” cannot be implemented (fout-fin=const). Analysis of Simple PLLs If the loop is locked, the input and output frequencies are equal and the phase difference is constant (static phase error). the PD generates repetitive pulses, the loop filter extracts the average level, and the VCO senses this level so as to operate at required frequency. Analysis of Simple PLLs If the input frequency changes by ∆ω, how much is the change in the phase error? Assume the loop remains locked. Such a change requires that Vcont change by ∆ω/KVCO. This in turn necessitates a phase error change of The phase error varies with the frequency step. To minimize this variation, KPDKVCO must be maximized. Response of PLL to Input Frequency Step At t=t1, ωout=ω ωin but the phase error has not reached its final value. The loop locks only after two conditions are satisfied: (1) ωout becomes equal to ωin (2) the difference between ϕin and ϕout settles to its proper final value PLL as FM demodulator An FSK waveform is applied to a PLL the input frequency toggles between two values and so does the output frequency. the control voltage must also toggle between two values providing the original bit stream. a PLL can serve as an FSK (and, more generally, FM) demodulator if Vcont is considered the output. Loop Dynamics: the Meaning of Transfer Function in Phase Domain The transfer function of a voltage-domain circuit signifies how a sinusoidal input voltage propagates to the output. The transfer function of a PLL must reveal how a slow or a fast change in the input (excess) phase propagates to the output (low pass filtering) The PLL produces a well defined output frequency, rejecting accidental parameter variations. Loop Dynamics: Phase Domain Model The open-loop transfer function Overall closed-loop transfer function Since the open-loop transfer function contains one pole at the origin (due to the VCO), this system is called “type-I PLL”. H(s) refers to phase fluctuations not to static phase difference, i.e. for slow phase fluctuations (s≈0), H≈1, but a non-zero phase difference exists between input and output. Simple PLL Stability 1 s = −ξω n 1 ± 1 − 2 ξ Lower ωLPF (to suppress ripple) and/or higher KPDKVCO (to reduce static phase error) bring to lower ξ which a lower phase margin. ξ is typically chosen to be √2/2 or larger so as to provide a well-behaved (critical damped or overdamped) time-domain response. Example: if ξ=1 loop time constant τ = (ω n ) loop bandwidth ∝ ω n = 2ω LPF −1 = (2ω LPF ) −1 Frequency Multiplication A voltage buffer can provide amplification if its output is divided before returning to the input. In the same way the output frequency of a PLL can be divided and then fed back. The ÷M circuit is a counter that generates one output pulse for every M input pulses. The divide ratio, M, is called the “modulus”. The loop locks at ωin=ω ωF=ω ωout/M ωout=Mω ωin. The effective VCO gain is reduced to KVCO/M reducing the open-loop gain (higher static phase error). Programming the value of M, the loop can be used as a frequency synthesizer. Drawbacks of Simple PLL Tight relation between the loop stability and the corner frequency of the low-pass filter. The finite static phase error and its variation with the input frequency also prove undesirable in some applications. Limited “acquisition range”: if the VCO frequency and the input frequency are very different at the start-up, the loop may never “acquire” lock. Type-II PLL: Phase/Frequency Detectors The limited frequency range is due to the fact that PDs produce little info if they sense unequal frequencies. It is desirable a circuit that operates as a FD if its input frequencies are different, and as a PD if they are. Such circuit is called a phase/frequency detector (PFD) A rising edge on A sets QA (if QA=QB=0), while a rising edge on B resets QA (if QA=1). The circuit is symmetric with respect to A and B (and QA and QB) Phase/Frequency Detectors The average value of QA-QB represents the frequency (if ωA≠ω ωB) or phase difference (if ωA=ω ωB) PFD: Logical Implementation Glitches on QB appears due to finite logic gates delay. Use of a PFD in PLL At the beginning of a transient, the PFD acts as a frequency detector, pushing the VCO frequency toward the input frequency. After the two are sufficiently close, the PFD operates as a phase detector, bringing the loop into phase lock. Charge Pumps Useful to address the trade-off between stability and phase error/ ripple. Switches S1 and S2 are controlled by the inputs “UP” and “Down”, respectively. Nominally I1=I2=Ip. A pulse of width ∆T on Up turns S1 on for ∆T seconds, allowing I1 to charge C1. Vout goes up by ∆T · I1/C1 Similarly, a pulse on Down yields a drop in Vout. If Up and Down are asserted simultaneously, I1 simply flows through S1 and S2 to I2, creating no change in Vout (I1=I2). PFD/CP Cascade an arbitrarily small (constant) phase difference between A and B turns one switch on, thereby charging or discharging C1 and driving Vout toward +∞ or -∞, i.e. a gain= ∞ if the loop time constant >> Tin, we can approximate this waveform by a ramp, as if the charge pump continuously injected current into C1 (continuous time approximation) The circuit behaves as an integrator Charge Pump PLLs The loop forces the input phase error to zero because a finite error would lead to an unbounded value fro Vcont (like the short-circuit approx. in opamps). Called Type-II PLL because its open-loop transfer function contains two poles at the origin. The two cascading integrators produce instability. Charge-Pump PLL If one of the integrators becomes lossy, the system can be stabilized. This can be accomplished by inserting a resistor in series with C1. The resulting circuit is called a “charge pump PLL” (CP-PLL). R1 introduces a zero Stability of Charge-Pump PLL As C1 increases, so does ζ --- a trend opposite of that observed in type-I PLL: trade-off between stability and ripple amplitude thus removed. A similar trend is observed for KVCO (also in this case opposite wrt type I PLLs). The phase margin is increased by the zero Frequency-Multiplying CP PLL The division of KVCO by M makes the loop less stable, requiring that Ip and/or C1 be larger. Higher-Order Loops The loop filter consisting of R1 and C1 proves inadequate because, even in the locked condition, it does not suppress the ripple sufficiently. Suppose, in the locked condition, the up and down pulses arrive with a small skew due to a propagation mismatches within the PFD The ripple thus consists of positive ad negative pulses of amplitude IpR1 (even higher than VDD!!!) occurring every Tin seconds. Addition of Second Capacitor to Loop Filter A common approach to lowering the ripple is to tie a capacitor C2 directly from the control line to ground. C2 should be sufficiently high to reduce ripple. C2 introduce an addition pole (ττ) degrading the loop stability. The phase margin is (ξ ξ is still the damping factor of the original second-order loop) In typical design we choose ζ = 1 and C2 ≈ 0.2C1 to maximize phase margin R1 cannot be arbitrarily (to increase ζ) high otherwise the loop filter reduces to C2 Alternative Second-Order Loop Filter The ripple at node X may be large but it is suppressed as it travels through the low-pass filter consisting of R2 and C2 The additional pole is at (R2C2)-1 (R2C2)-1 must remain 5 to 10 times higher than ωz= (R1C1)-1 so as to yield a reasonable phase margin. Phase Noise in PLLs: VCO Phase Noise Two sources of noise: the input reference oscillator phase noise (φ φin) the VCO phase noise (φ φVCO) Consider the VCO noise and set φin=0 PLL suppresses slow variations in the phase of the VCO but cannot provide much correction for fast variations (the loop gain falls) VCO Phase Noise vs. Loop Bandwidth the bandwidth can be increased if ωn is increased by a factor of K (suppose ζ is maintained constant). both poles scale up by a factor of K. since Φout/ΦVCO ≈ s2/ωn2 for s ≈ 0, the plot is shifted down by a factor of K2 at low values of ω that is the response now suppresses the VCO phase noise to a greater extent. VCO Phase Noise in PLL with feedback divide ratio ÷M √M √M the feedback is now weaker by a factor of M. The transfer function still applies, but both ζ and ωn are reduced by a factor of √M . to maintain the same transient behavior, ζ and ωn must be constant; e.g., the charge pump current must be scaled up by a factor of M. Thus, the poles given by previous equation simply decrease by factor of √M . for s 0, Φout/ΦVCO ≈ s2/ωn2, which is a factor of M higher than that of the dividerless loop. The magnitude of the transfer function thus appears as depicted below on the right. VCO Phase Noise: White Noise and Flicker Noise The VCO phase noise is “shaped” by the PLL transfer function ω is the offset frequency low offset frequencies high offset frequencies (ζ =1) (ζ =1) Shaped VCO Noise Summary The overall PLL output phase noise is equal to the sum of SA and SB resulting lower wrt the VCO phase noise. The actual shape depends (1) on the intersection frequency of α/ω3 and β/ω2 (2) on the value of ωn Shaped VCO Noise Summary high thermal noise induced phase noise low thermal noise induced phase noise (left) the intersection of α/ω3 and β/ω2 lies at a low frequency (wrt ωn) (right) the intersection of α/ω3 and β/ω2 lies at a high frequency (wrt ωn) Reference Phase Noise Crystal oscillators providing the reference typically display a flat phase noise profile beyond an offset of a few kilohertz. The output phase noise is shaped by the PLL transfer function. The total phase noise at the output increases with the loop bandwidth, a trend opposite to that observed for VCO phase noise. PLLs performing frequency multiplication “amplify” the low-frequency reference phase noise by a factor M2. Overall Phase Noise the loop bandwidth entails a trade-off between the reference and the VCO phase noise. Loop Bandwidth Loop Filter Design Procedure The loop filter is designed beginning with the two governing equations The loop time-constant must be much longer than the input period to ensure a well behaved settling (loops that are not sufficiently slow exhibit an underdamped behavior or may simply not lock). In typical design We now have two equations and three unknowns (Ip, C1, R1). The charge pump current can be chosen in the range of few tens of µA to few mA. We choose C2=0.2C1 so as to maximize phase margin. Loop Filter Design Example A PFD-CP/type II-PLL (Ip = 500 µA) must generate an output frequency of 2.4 GHz from a 1-MHz reference with a symmetrical tuning range of 12.5% and VDD=1V. The input reference phase noise is -150 dBc/Hz at 100 kHz frequency offset, and the VCO phase noise is -70 dBc/Hz at 100 KHz frequency offset. Determine 1) the loop filter parameters 2) the output phase noise at 100 kHz frequency offset Solution: We select ζ=1 2.5ωn = ωin/10 ωn = 2π(40 kHz) KVCO= 2π× × 0.125*2.4Ghz/1V= 2π× × 300 MHz/V Substituting in the above equations (M=2400) C1 = 1 nF and R1 = 8 kΩ. C2 =0.2C1= 0.2 nF. PLL Phase Noise Example The output phase noise due to the VCO is (the term in parenthesis is the VCO phase noise, i.e. -70 dBc/Hz) = -71.3 dBc/Hz The output phase noise due to the input reference is (SREF is the input reference phase noise , i.e. -150 dBc/Hz) = -153 dBc/Hz The overall phase noise is due only to the VCO noise (-71.3 dBc/Hz)