16-Bit 1 MSPS PulSARTM

Unipolar ADC with Reference

AD7653

FEATURES

Throughput:

1 MSPS (Warp mode)

800 kSPS (Normal mode)

666 kSPS (Impulse mode)

16-bit resolution

Analog input voltage range: 0 V to 2.5 V

No pipeline delay

Parallel and serial 5 V/3 V interface

SPI®/QSPITM/MICROWIRETM/DSP compatible

Single 5 V supply operation

Power dissipation

92 mW typ @ 666 kSPS, 138 µW @ 1 kSPS without REF

128 mW typ @ 1 MSPS with REF

48-lead LQFP and 48-lead LFCSP packages

Pin-to-pin compatible with PulSAR ADCs

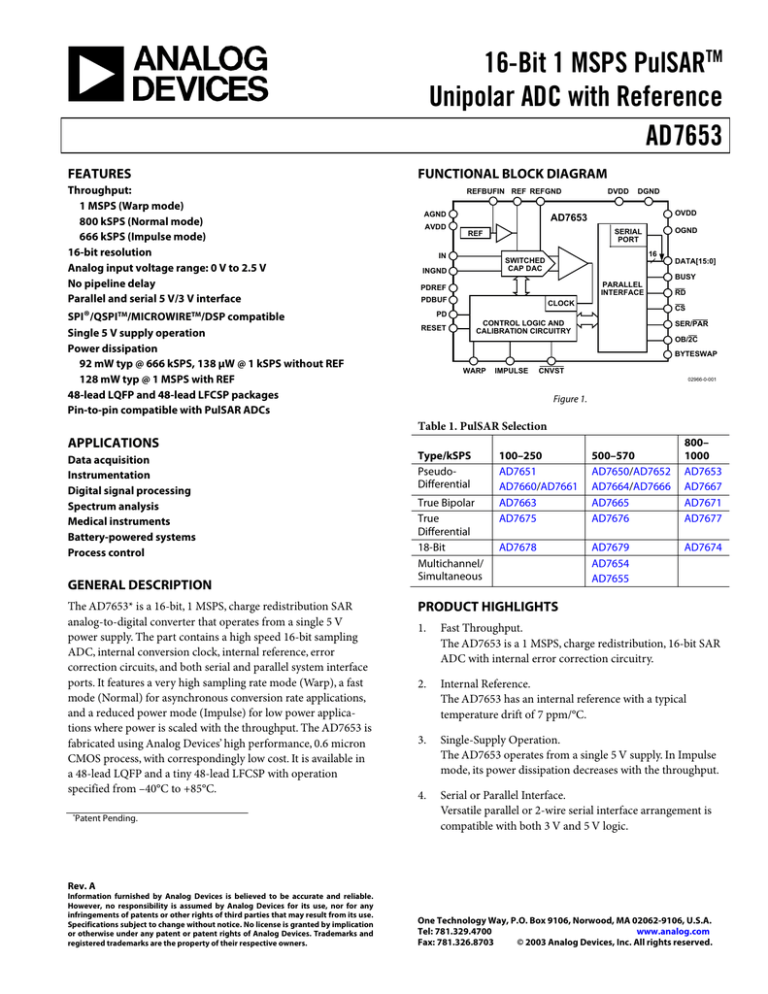

FUNCTIONAL BLOCK DIAGRAM

REFBUFIN REF REFGND

AGND

AVDD

DVDD

DGND

OVDD

AD7653

REF

IN

16

SWITCHED

CAP DAC

INGND

OGND

SERIAL

PORT

PARALLEL

INTERFACE

PDREF

PDBUF

CLOCK

BUSY

RD

CS

PD

CONTROL LOGIC AND

CALIBRATION CIRCUITRY

RESET

DATA[15:0]

SER/PAR

OB/2C

BYTESWAP

WARP

IMPULSE

CNVST

02966-0-001

Figure 1.

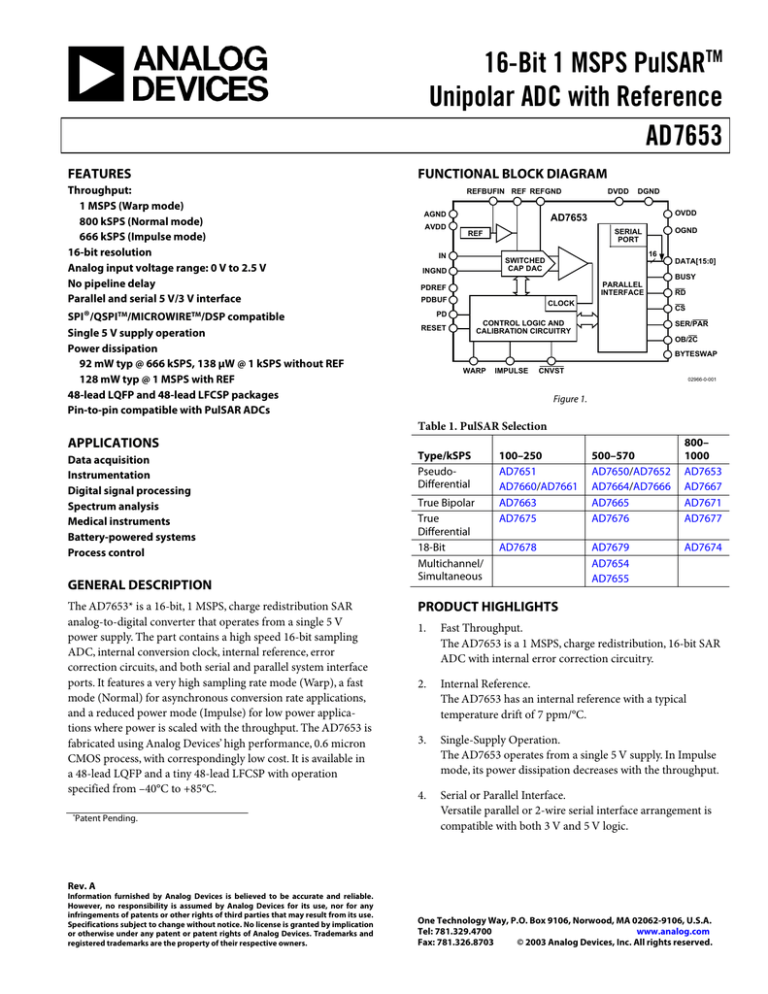

Table 1. PulSAR Selection

APPLICATIONS

Data acquisition

Instrumentation

Digital signal processing

Spectrum analysis

Medical instruments

Battery-powered systems

Process control

GENERAL DESCRIPTION

The AD7653* is a 16-bit, 1 MSPS, charge redistribution SAR

analog-to-digital converter that operates from a single 5 V

power supply. The part contains a high speed 16-bit sampling

ADC, internal conversion clock, internal reference, error

correction circuits, and both serial and parallel system interface

ports. It features a very high sampling rate mode (Warp), a fast

mode (Normal) for asynchronous conversion rate applications,

and a reduced power mode (Impulse) for low power applications where power is scaled with the throughput. The AD7653 is

fabricated using Analog Devices’ high performance, 0.6 micron

CMOS process, with correspondingly low cost. It is available in

a 48-lead LQFP and a tiny 48-lead LFCSP with operation

specified from –40°C to +85°C.

*

Patent Pending.

Type/kSPS

PseudoDifferential

True Bipolar

True

Differential

18-Bit

Multichannel/

Simultaneous

100–250

AD7651

AD7660/AD7661

AD7663

AD7675

500–570

AD7650/AD7652

AD7664/AD7666

AD7665

AD7676

AD7678

AD7679

AD7654

AD7655

800–

1000

AD7653

AD7667

AD7671

AD7677

AD7674

PRODUCT HIGHLIGHTS

1.

Fast Throughput.

The AD7653 is a 1 MSPS, charge redistribution, 16-bit SAR

ADC with internal error correction circuitry.

2.

Internal Reference.

The AD7653 has an internal reference with a typical

temperature drift of 7 ppm/°C.

3.

Single-Supply Operation.

The AD7653 operates from a single 5 V supply. In Impulse

mode, its power dissipation decreases with the throughput.

4.

Serial or Parallel Interface.

Versatile parallel or 2-wire serial interface arrangement is

compatible with both 3 V and 5 V logic.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.326.8703

© 2003 Analog Devices, Inc. All rights reserved.

AD7653

SPECIFICATIONS

Table 2. –40°C to +85°C, AVDD = DVDD = 5 V, OVDD = 2.7 V to 5.25 V, unless otherwise noted

Parameter

RESOLUTION

ANALOG INPUT

Voltage Range

Operating Input Voltage

Analog Input CMRR

Input Current

Input Impedance1

THROUGHPUT SPEED

Complete Cycle

Throughput Rate

Time between Conversions

Complete Cycle

Throughput Rate

Complete Cycle

Throughput Rate

DC ACCURACY

Integral Linearity Error

No Missing Codes

Differential Linearity Error

Transition Noise

Unipolar Zero Error, TMIN to TMAX3

Unipolar Zero Error Temperature Drift

Full-Scale Error, TMIN to TMAX3

Full-Scale Error Temperature Drift

Power Supply Sensitivity

AC ACCURACY

Signal-to-Noise

Spurious Free Dynamic Range

Total Harmonic Distortion

Signal-to-(Noise + Distortion)

–3 dB Input Bandwidth

SAMPLING DYNAMICS

Aperture Delay

Aperture Jitter

Transient Response

REFERENCE

Internal Reference Voltage

Internal Reference Temperature Drift

Line Regulation

Turn-On Settling Time

Temperature Pin

Voltage Output @ 25°C

Temperature Sensitivity

Output Resistance

External Reference Voltage Range

External Reference Current Drain

Conditions

Min

16

VIN – VINGND

VIN

0

–0.1

VINGND

fIN = 10 kHz

1 MSPS Throughput

–0.1

In Warp Mode

In Warp Mode

In Warp Mode

In Normal Mode

In Normal Mode

In Impulse Mode

In Impulse Mode

Typ

Max

Unit

Bits

VREF

+3

V

V

+0.5

V

dB

µA

1

1000

1

1.25

800

1.5

666

µs

kSPS

ms

µs

kSPS

µs

kSPS

+6

±0.4

±2

LSB2

Bits

LSB

LSB

LSB

ppm/°C

% of FSR

ppm/°C

LSB

86

98

–98

–96

86

30

12

dB4

dB

dB

dB

dB

dB

MHz

2

5

ns

ps rms

ns

65

12

1

0

0

–6

15

–2

+3

0.7

±25

±0.2

REF = 2.5 V

±0.12

AVDD = 5 V ± 5%, with REF

fIN = 100 kHz

fIN = 100 kHz

fIN = 45 kHz

fIN = 100 kHz

fIN = 100 kHz

–60 dB Input, fIN = 100 kHz

Full-Scale Step

250

VREF @ 25°C

–40°C to +85°C

AVDD = 5 V ± 5%

CREF = 10 µF

2.48

2.3

1 MSPS Throughput

Rev. A | Page 3 of 28

2.50

±7

±24

5

300

1

4.3

2.5

300

2.52

AVDD – 1.85

V

ppm/°C

ppm/V

ms

mV

mV/°C

kΩ

V

µA

AD7653

Parameter

DIGITAL INPUTS

Logic Levels

VIL

VIH

IIL

IIH

DIGITAL OUTPUTS

Data Format5

Pipeline Delay6

VOL

VOH

POWER SUPPLIES

Specified Performance

AVDD

DVDD

OVDD

Operating Current8

AVDD9

AVDD10

DVDD11

OVDD11

Power Dissipation without REF

Power Dissipation with REF

TEMPERATURE RANGE12

Specified Performance

Conditions

Min

Typ

–0.3

2.0

–1

–1

ISINK = 1.6 mA

ISOURCE = –500 µA

1 MSPS Throughput

With Reference and Buffer

Reference and Buffer Alone

5

5

18.7

3

6.7

200

92

138

128

666 kSPS Throughput11

1 kSPS Throughput11

1 MSPS Throughput8

–40

1

Unit

+0.8

DVDD + 0.3

+1

+1

V

V

µA

µA

0.4

V

V

5.25

5.25

5.257

V

V

V

OVDD – 0.6

4.75

4.75

2.7

TMIN to TMAX

Max

145

mA

mA

mA

µA

mW

µW

mW

+85

°C

115

See Analog Input section.

LSB means least significant bit. With the 0 V to 2.5 V input range, 1 LSB is 38.15 µV.

See Definitions of Specifications section. These specifications do not include the error contribution from the external reference.

4

All specifications in dB are referred to a full-scale input FS. Tested with an input signal at 0.5 dB below full-scale, unless otherwise specified.

5

Parallel or serial 16-bit.

6

Conversion results are available immediately after completed conversion.

7

The max should be the minimum of 5.25 V and DVDD + 0.3 V.

8

In Warp mode.

9

With REF, PDREF and PDBUF are LOW; without REF, PDREF and PDBUF are HIGH.

10

With PDREF, PDBUF LOW and PD HIGH.

11

Impulse Mode. Tested in Parallel Reading mode.

12

Consult factory for extended temperature range.

2

3

Rev. A | Page 4 of 28

AD7653

TIMING SPECIFICATIONS

Table 3. –40°C to +85°C, AVDD = DVDD = 5 V, OVDD = 2.7 V to 5.25 V, unless otherwise noted

Parameter

Refer to Figure 26 and Figure 27

Convert Pulse Width

Time between Conversions (Warp Mode/Normal Mode/Impulse Mode)1

CNVST LOW to BUSY HIGH Delay

BUSY HIGH All Modes Except Master Serial Read after Convert

(Warp Mode/Normal Mode/Impulse Mode)

Aperture Delay

End of Conversion to BUSY LOW Delay

Conversion Time (Warp Mode/Normal Mode/Impulse Mode)

Acquisition Time

RESET Pulse Width

Refer to Figure 28, Figure 29, and Figure 30 (Parallel Interface Modes)

CNVST LOW to DATA Valid Delay (Warp Mode/Normal Mode/Impulse Mode)

DATA Valid to BUSY LOW Delay

Bus Access Request to DATA Valid

Bus Relinquish Time

Refer to Figure 32 and Figure 33 (Master Serial Interface Modes)2

CS LOW to SYNC Valid Delay

CS LOW to Internal SCLK Valid Delay2

CS LOW to SDOUT Delay

CNVST LOW to SYNC Delay (Warp Mode/Normal Mode/Impulse Mode)

SYNC Asserted to SCLK First Edge Delay

Internal SCLK Period3

Internal SCLK HIGH3

Internal SCLK LOW3

SDOUT Valid Setup Time3

SDOUT Valid Hold Time3

SCLK Last Edge to SYNC Delay3

CS HIGH to SYNC HI-Z

CS HIGH to Internal SCLK HI-Z

CS HIGH to SDOUT HI-Z

BUSY HIGH in Master Serial Read after Convert3

(Warp Mode/Normal Mode/Impulse Mode)

CNVST LOW to SYNC Asserted Delay

(Warp Mode/Normal Mode/Impulse Mode)

SYNC Deasserted to BUSY LOW Delay

Refer to Figure 34 and Figure 35 (Slave Serial Interface Modes) 2

External SCLK Setup Time

External SCLK Active Edge to SDOUT Delay

SDIN Setup Time

SDIN Hold Time

External SCLK Period

External SCLK HIGH

External SCLK LOW

Symbol

Min

t1

t2

t3

10

1/1.25/1.5

t4

t5

t6

t7

t8

t9

t10

t11

t12

t13

t14

t15

t16

t17

t18

t19

t20

t21

t22

t23

t24

t25

t26

t27

Typ

Unit

35

ns

µs

ns

0.75/1/1.25

2

10

0.75/1/1.25

250

10

0.75/1/1.25

12

45

15

5

10

10

10

25/275/525

3

25

12

7

4

2

3

40

10

10

10

t28

See Table 4

t29

t30

0.75/1/1.25

25

t31

t32

t33

t34

t35

t36

t37

Max

5

3

5

5

25

10

10

µs

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

µs

ns

18

1In Warp mode only, the maximum time between conversions is 1 ms; otherwise, there is no required maximum time.

2

In serial interface modes, the SYNC, SCLK, and SDOUT timings are defined with a maximum load CL of 10 pF; otherwise, the load is 60 pF maximum.

3

In Serial Master Read during Convert Mode. See Table 4 for Serial Master Read after Convert mode.

Rev. A | Page 5 of 28

µs

ns

ns

µs

ns

ns

ns

ns

ns

ns

ns

ns

ns

AD7653

Table 4. Serial Clock Timings in Master Read after Convert

DIVSCLK[1]

DIVSCLK[0]

SYNC to SCLK First Edge Delay Minimum

Internal SCLK Period Minimum

Internal SCLK Period Maximum

Internal SCLK HIGH Minimum

Internal SCLK LOW Minimum

SDOUT Valid Setup Time Minimum

SDOUT Valid Hold Time Minimum

SCLK Last Edge to SYNC Delay Minimum

BUSY HIGH Width Maximum (Warp)

BUSY HIGH Width Maximum (Normal)

BUSY HIGH Width Maximum (Impulse)

Symbol

t18

t19

t19

t20

t21

t22

t23

t24

t28

t28

t28

Rev. A | Page 6 of 28

0

0

3

25

40

12

7

4

2

3

1.5

1.75

2

0

1

17

50

70

22

21

18

4

55

2

2.25

2.5

1

0

17

100

140

50

49

18

30

130

3

3.25

3.5

1

1

17

200

280

100

99

18

80

290

5.25

5.55

5.75

Unit

ns

ns

ns

ns

ns

ns

ns

ns

µs

µs

µs

AD7653

DEFINITIONS OF SPECIFICATIONS

Integral Nonlinearity Error (INL)

Signal-to-Noise Ratio (SNR)

Linearity error refers to the deviation of each individual code

from a line drawn from negative full scale through positive full

scale. The point used as negative full scale occurs ½ LSB before

the first code transition. Positive full scale is defined as a level

1½ LSB beyond the last code transition. The deviation is

measured from the middle of each code to the true straight line.

SNR is the ratio of the rms value of the actual input signal to the

rms sum of all other spectral components below the Nyquist

frequency, excluding harmonics and dc. The value for SNR is

expressed in decibels.

Differential Nonlinearity Error (DNL)

In an ideal ADC, code transitions are 1 LSB apart. Differential

nonlinearity is the maximum deviation from this ideal value. It

is often specified in terms of resolution for which no missing

codes are guaranteed.

Full-Scale Error

The last transition (from 011…10 to 011…11 in twos

complement coding) should occur for an analog voltage 1½ LSB

below the nominal full scale (2.49994278 V for the 0 V to 2.5 V

range). The full-scale error is the deviation of the actual level of

the last transition from the ideal level.

Unipolar Zero Error

The first transition should occur at a level ½ LSB above analog

ground (19.073 µV for the 0 V to 2.5 V range). Unipolar zero

error is the deviation of the actual transition from that point.

Spurious-Free Dynamic Range (SFDR)

Signal-to-(Noise + Distortion) Ratio (S/[N+D])

S/(N+D) is the ratio of the rms value of the actual input signal

to the rms sum of all other spectral components below the

Nyquist frequency, including harmonics but excluding dc. The

value for S/(N+D) is expressed in decibels.

Aperture Delay

Aperture delay is a measure of the acquisition performance and

is measured from the falling edge of the CNVST input to when

the input signal is held for a conversion.

Transient Response

Transient response is the time required for the AD7653 to

achieve its rated accuracy after a full-scale step function is

applied to its input.

Overvoltage Recovery

Overvoltage recovery is the time required for the ADC to

recover to full accuracy after an analog input signal 150% of the

full-scale value is reduced to 50% of the full-scale value.

Reference Voltage Temperature Coefficient

SFDR is the difference, in decibels (dB), between the rms

amplitude of the input signal and the peak spurious signal.

Reference voltage temperature coefficient is the change of

internal reference voltage output voltage V over the operating

temperature range and normalized by the output voltage at

25°C, expressed in ppm/°C. The equation follows:

Effective Number of Bits (ENOB)

ENOB is a measurement of the resolution with a sine wave

input. It is related to S/(N+D) by the following formula:

TCV ( ppm / °C ) =

ENOB = (S/[N+D]dB – 1.76)/6.02

and is expressed in bits.

Total Harmonic Distortion (THD)

THD is the ratio of the rms sum of the first five harmonic

components to the rms value of a full-scale input signal, and is

expressed in decibels.

V (T 2) – V (T 1)

× 106

V (25°C) × (T 2 – T 1)

where:

V(25°C) = V at +25°C

V(T2) = V at Temperature 2 (+85°C)

V(T1) = V at Temperature 1 (–40°C)

Rev. A | Page 11 of 28

AD7653

TYPICAL PERFORMANCE CHARACTERISTICS

2.0

4

3

1.5

2

1.0

DNL (LSB)

INL (LSB)

1

0

–1

0.5

0

–2

–0.5

–3

–4

–1.0

16384

0

49152

32768

CODE

65536

0

16384

65536

02966-0-026

Figure 8. Differential Nonlinearity vs. Code

Figure 5. Integral Nonlinearity vs. Code

160000

140000

114641

112516

120000

49152

32768

CODE

02966-0-023

146148

140000

120000

100000

COUNTS

60000

80000

60000

40000

15906

0

0

17001

679

20000

377

0

0

0

0

53

2856

3099

8002

9

0

8003

8004

7FFB 7FFC 7FFD 7FFE 7FFF 8000 8001 8002 8003 8004

CODE IN HEX

02966-0-027

7FFC 7FFD 7FFE 7FFF 8000 8001

CODE IN HEX

Figure 6. Histogram of 261,120 Conversions of a

DC Input at the Code Transition

Figure 9. Histogram of 261,120 Conversions of a

DC Input at the Code Center

0

02966-0-028

90

15.0

87

14.5

fS = 1000kSPS

fIN = 101kHz

–20

SNR = 86.0dB

THD = 90.3dB

SFDR = 91.5dB

S/[N+D] = 84.8dB

–40

–60

SNR, S/[N+D] (dB)

AMPLITUDE (dB of Full Scale)

54473

40000

20000

0

54482

–80

–100

–120

SNR

84

14.0

13.5

81

S/[N+D]

13.0

78

ENOB

–140

12.5

75

–160

–180

72

0

100

200

300

FREQUENCY (kHz)

400

500

02966-0-029

1

10

100

FREQUENCY (kHz)

Figure 10. SNR, S/(N+D), and ENOB vs. Frequency

Figure 7. FFT Plot

Rev. A | Page 12 of 28

12.0

1000

02966-0-030

ENOB (Bits)

COUNTS

100000

80000

AD7653

SFDR

–60

–70

80

–80

60

–90

THD

40

–100

THIRD

HARMONIC

SECOND

HARMONIC

1

THIRD

HARMONIC

–115

–125

–55

0

1000

10

100

FREQUENCY (kHz)

–35

–15

5

25

45

65

85

125

105

TEMPERATURE (°C)

02966-0-031

02966-0-034

Figure 14. THD and Harmonics vs. Temperature

Figure 11. THD, Harmonics, and SFDR vs. Frequency

92

100000

91

10000

AVDD, WARP/NORMAL

DVDD, WARP/NORMAL

90

OPERATING CURRENT (µA)

SNR, S/[N+D] REFERRED TO FULL SCALE (dB)

SECOND

HARMONIC

THD

–105

20

–110

–120

THD, HARMONICS (dB)

100

SFDR (dB)

THD, HARMONICS (dB)

–95

120

–50

89

SNR

88

87

S/[N+D]

86

85

84

1000

100

DVDD, IMPULSE

AVDD, IMPULSE

10

1

OVDD, ALL MODES

0.1

0.01

83

82

–60

–50

–40

–30

–20

–10

INPUT LEVEL (dB)

PDREF = PDBUF = HIGH

0.001

10

0

10000

100000

SAMPLE RATE (SPS)

02966-A-032

Figure 12. SNR and S/(N+D) vs. Input Level (Referred to Full Scale)

1000000

02966-0-036

Figure 15. Operating Current vs. Sample Rate

6

14.75

89

1000

100

14.50

SNR

S[N+D]

87

14.25

ENOB

ENOB (Bits)

SNR, S/[N+D] (dB)

88

14.00

86

ZERO ERROR, FULL SCALE (LSB)

5

4

3

2

FULL SCALE

1

0

–1

ZERO ERROR

–2

–3

–4

–5

85

–55

–35

–15

5

25

45

65

TEMPERATURE (°C)

85

105

13.75

125

–6

–55

–35

–15

5

25

45

65

TEMPERATURE (°C)

02966-0-033

85

105

125

02966-0-040

Figure 16. Zero Error, Full Scale with Reference vs. Temperature

Figure 13. SNR, S/(N+D), and ENOB vs. Temperature

Rev. A | Page 13 of 28

AD7653

2.5020

50

OVDD = 2.7V @ 85°C

2.5019

2.5018

40

OVDD = 2.7V @ 25°C

2.5017

t12 DELAY (ns)

VREF (V)

2.5016

2.5015

2.5014

2.5013

2.5012

30

OVDD = 5V @ 85°C

20

OVDD = 5V @ 25°C

2.5011

10

2.5010

2.5009

2.5008

–40

–20

0

20

40

80

60

TEMPERATURE (°C)

100

0

120

Figure 17. Typical Reference Output Voltage vs. Temperature

80

NUMBER OF UNITS

70

60

50

40

30

20

10

–30 –26 –22 –18 –14 –10 –6 –2

2

6

10 14 18 22 26 30

REFERENCE DRIFT (ppm/°C)

50

100

150

Figure 19. Typical Delay vs. Load Capacitance CL

90

0

0

CL (pF)

02966-0-038

02966-0-039

Figure 18. Reference Voltage Temperature Coefficient Distribution (335 Units)

Rev. A | Page 14 of 28

200

02966-0-035