LP3941A Cellular Phone Power Management Unit

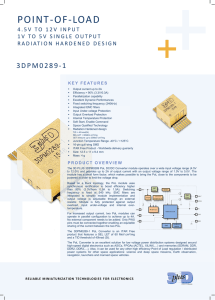

advertisement