A Low-Voltage Lateral SJ-FINFET With Deep-Trench p

advertisement

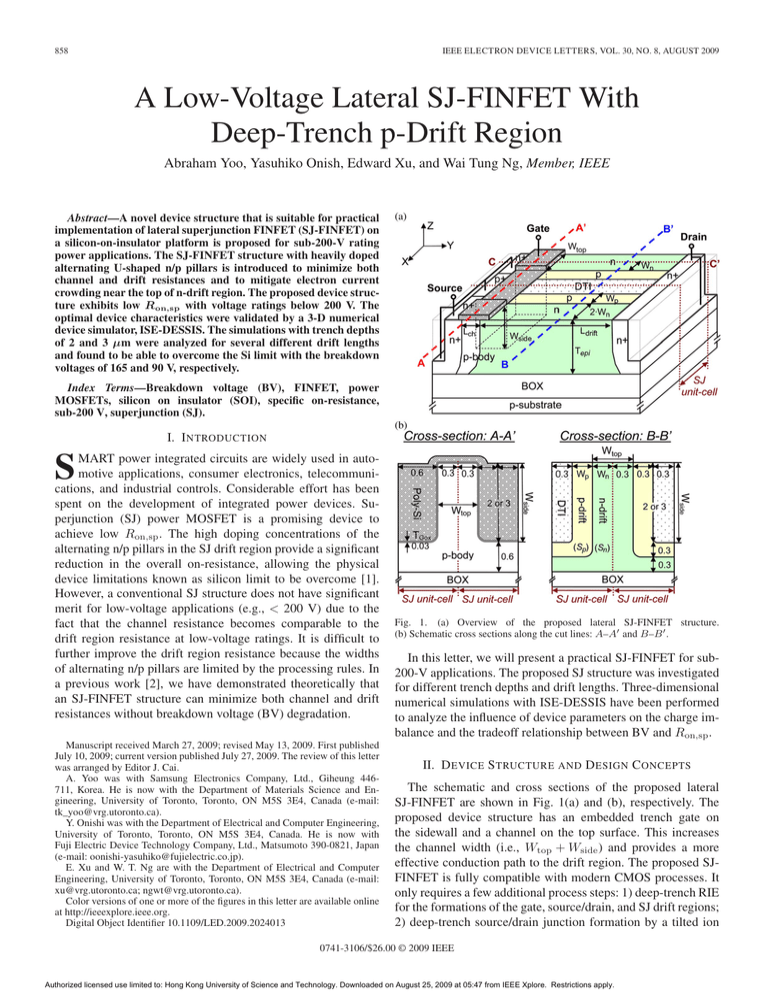

858 IEEE ELECTRON DEVICE LETTERS, VOL. 30, NO. 8, AUGUST 2009 A Low-Voltage Lateral SJ-FINFET With Deep-Trench p-Drift Region Abraham Yoo, Yasuhiko Onish, Edward Xu, and Wai Tung Ng, Member, IEEE Abstract—A novel device structure that is suitable for practical implementation of lateral superjunction FINFET (SJ-FINFET) on a silicon-on-insulator platform is proposed for sub-200-V rating power applications. The SJ-FINFET structure with heavily doped alternating U-shaped n/p pillars is introduced to minimize both channel and drift resistances and to mitigate electron current crowding near the top of n-drift region. The proposed device structure exhibits low Ron,sp with voltage ratings below 200 V. The optimal device characteristics were validated by a 3-D numerical device simulator, ISE-DESSIS. The simulations with trench depths of 2 and 3 μm were analyzed for several different drift lengths and found to be able to overcome the Si limit with the breakdown voltages of 165 and 90 V, respectively. Index Terms—Breakdown voltage (BV), FINFET, power MOSFETs, silicon on insulator (SOI), specific on-resistance, sub-200 V, superjunction (SJ). I. I NTRODUCTION S MART power integrated circuits are widely used in automotive applications, consumer electronics, telecommunications, and industrial controls. Considerable effort has been spent on the development of integrated power devices. Superjunction (SJ) power MOSFET is a promising device to achieve low Ron,sp . The high doping concentrations of the alternating n/p pillars in the SJ drift region provide a significant reduction in the overall on-resistance, allowing the physical device limitations known as silicon limit to be overcome [1]. However, a conventional SJ structure does not have significant merit for low-voltage applications (e.g., < 200 V) due to the fact that the channel resistance becomes comparable to the drift region resistance at low-voltage ratings. It is difficult to further improve the drift region resistance because the widths of alternating n/p pillars are limited by the processing rules. In a previous work [2], we have demonstrated theoretically that an SJ-FINFET structure can minimize both channel and drift resistances without breakdown voltage (BV) degradation. Manuscript received March 27, 2009; revised May 13, 2009. First published July 10, 2009; current version published July 27, 2009. The review of this letter was arranged by Editor J. Cai. A. Yoo was with Samsung Electronics Company, Ltd., Giheung 446711, Korea. He is now with the Department of Materials Science and Engineering, University of Toronto, Toronto, ON M5S 3E4, Canada (e-mail: tk_yoo@vrg.utoronto.ca). Y. Onishi was with the Department of Electrical and Computer Engineering, University of Toronto, Toronto, ON M5S 3E4, Canada. He is now with Fuji Electric Device Technology Company, Ltd., Matsumoto 390-0821, Japan (e-mail: oonishi-yasuhiko@fujielectric.co.jp). E. Xu and W. T. Ng are with the Department of Electrical and Computer Engineering, University of Toronto, Toronto, ON M5S 3E4, Canada (e-mail: xu@vrg.utoronto.ca; ngwt@vrg.utoronto.ca). Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org. Digital Object Identifier 10.1109/LED.2009.2024013 Fig. 1. (a) Overview of the proposed lateral SJ-FINFET structure. (b) Schematic cross sections along the cut lines: A–A and B–B . In this letter, we will present a practical SJ-FINFET for sub200-V applications. The proposed SJ structure was investigated for different trench depths and drift lengths. Three-dimensional numerical simulations with ISE-DESSIS have been performed to analyze the influence of device parameters on the charge imbalance and the tradeoff relationship between BV and Ron,sp . II. D EVICE S TRUCTURE AND D ESIGN C ONCEPTS The schematic and cross sections of the proposed lateral SJ-FINFET are shown in Fig. 1(a) and (b), respectively. The proposed device structure has an embedded trench gate on the sidewall and a channel on the top surface. This increases the channel width (i.e., Wtop + Wside ) and provides a more effective conduction path to the drift region. The proposed SJFINFET is fully compatible with modern CMOS processes. It only requires a few additional process steps: 1) deep-trench RIE for the formations of the gate, source/drain, and SJ drift regions; 2) deep-trench source/drain junction formation by a tilted ion 0741-3106/$26.00 © 2009 IEEE Authorized licensed use limited to: Hong Kong University of Science and Technology. Downloaded on August 25, 2009 at 05:47 from IEEE Xplore. Restrictions apply. YOO et al.: LOW-VOLTAGE LATERAL SJ-FINFET WITH DEEP-TRENCH p-DRIFT REGION Fig. 2. Relationships between BV and charge imbalance for the proposed SJ-FINFET with Ldrift of 3.0 and 6.0 μm, Wn = Wp = 0.3 μm, and trench depths (Wside ) of 2.0 and 3.0 μm. implantation; and 3) p-pillar formation by a deep-trench dopedpoly diffusion technology [3]. With accurate control of the thermal process, the width of p-pillar can be much narrower than that of our previous SJ-FINFET design [2]. The inclusion of these simple process modules will not have significant impact on the overall processing cost. As shown in Fig. 1(b), the proposed device structures with two different trench depths (Wside = 2 or 3 μm) have been studied for several different n-drift lengths ranging from 3 to 12 μm. It can be seen that the cross-sectional area of n-drift (Sn ) is larger than that of p-drift (Sp ) within the SJ unit cell. This asymmetric SJ drift structure was analyzed for different voltage rating in order to examine its effect on the on-resistance and the sensitivity of the BV due to charge imbalance. To achieve a fully depleted SJ drift region where Sn is larger than Sp , the doping concentration of the p-drift layer (NA ) should be greater than the n-drift doping concentration (ND ) [4]. For trench depths of 2 and 3 μm, NA is calculated to be about 23% and 16% greater than ND , respectively. This indicates that the increase in NA is less pronounced for a deeper trench structure since the difference between Sn and Sp becomes smaller for a deeper trench structure. III. S IMULATION R ESULTS AND D ISCUSSION The initial n-drift doping concentration for d = 0.3 μm was calculated using [4] ND = 1.41 × 1012 · α7/6 · d−7/6 (cm−3 ) α = 1/2 or 1/3 for vertical or lateral SJ device (1) where d is the width of n/p drift layer (only if d = Wn = Wp ) and α is the optimal doping coefficient (0 < α < 1). Dividing the unit cell along the center of the structure as shown in Fig. 1(a), the widths of n/p pillars are the same (i.e., 0.3 μm). Based on the calculated ND (= 7.4 × 1016 cm−3 ), the charge imbalance simulations with several NA ’s were performed for different trench depths and drift lengths. Fig. 2 859 Fig. 3. Specific on-resistance profiles along C–C cut line during on-state for conventional SJ SOI-LDMOS and the proposed SJ-FINFET. shows the relationship between BV and charge imbalance. It can be seen that the variation of Ldrift has no effect on the charge imbalance, but the increase of trench depth from 2 to 3 μm gives a 5% positive shift of the charge imbalance (%) for the optimal BV. This can be explained by the fact that Sn and Sp are always constant at a fixed trench depth whether Ldrift increases or not. However, the ratio between Sn and Sp becomes smaller for a deeper trench structure. Therefore, the difference between ND and NA would also be smaller as the trench depth is increased. Fig. 3 shows the specific on-resistance distribution along the SJ-FINFET cross section with Ldrift = 3 μm. In comparison with the conventional SJ-LDMOS data, the proposed SJ devices with the trench depths of 2 and 3 μm demonstrate 58% and 74% reductions in channel resistance and 44% and 60% reductions in drift resistance, respectively. This is due to the fact that the majority of electron current is concentrated near the top surface of n-drift layer in the conventional planar gate SJ device. However, the proposed SJ device uses a trench gate not only to reduce the channel resistance but also to relax the electron current crowding near the top of the n-drift region pillar. Finally, the simulated performance of the SJ-FINFET is compared with the ideal silicon limit and other SJ-LDMOS transistors in Fig. 4. It is noted that the simulation results are extracted for different Ldrift , while the optimum charge-balanced conditions were maintained in all cases. The specific onresistance is found to be linearly proportional to BV 1.9−2.0 , which indicates a better device performance than the theoretical silicon limit (∝ BV 2.5 ). For the 2- and 3-μm trench depth cases, a crossover between the simulation data (i.e., fitted line) and Si limit was estimated to be 165 and 90 V, respectively. In comparison with conventional SJ-LDMOS transistors with a planar gate, the proposed SJ-FINFET (i.e., Wside = 3 μm) exhibits a reduction in specific on-resistance by up to 46.5% at BV = 72 V. This result is very remarkable for the SJFINFET to be a competitive power device in the sub-200-V rating. Prototype devices are currently being fabricated, and Authorized licensed use limited to: Hong Kong University of Science and Technology. Downloaded on August 25, 2009 at 05:47 from IEEE Xplore. Restrictions apply. 860 IEEE ELECTRON DEVICE LETTERS, VOL. 30, NO. 8, AUGUST 2009 trench source/drain contacts has been proposed for the next generation of sub-200-V rating applications. Three-dimensional simulation results confirm that it is possible to get the best tradeoff between the BV and Ron,sp . The specific on-resistance strongly depends on the trench depth. With the optimized charge-balanced SJ drift region, the proposed SJ structure can break the ideal Si limit of BV and Ron,sp . R EFERENCES Fig. 4. Performance comparison between SJ simulation results with different trench gate depths and previously published data. comparison between the simulation and measurement will be reported afterward. IV. C ONCLUSION A new lateral SJ FINFET structure which employs a trench gate structure with the modified SJ drift region and deep- [1] F. Udrea, “State-of-the-art technologies and devices for high-voltage integrated circuits,” IET Circuits, Devices Syst., vol. 1, no. 5, pp. 357–365, 2007. [2] Y. Onishi, H. Wang, H. P. E. Xu, W. T. Ng, R. Wu, and J. K. O. Sin, “SJ-FINFET: A new low voltage lateral superjunction MOSFET,” in Proc. ISPSD, 2008, pp. 111–114. [3] L. Theolier, K. Isoird, F. Morancho, J. Roig, H. Mahfoz-Kotb, M. Brunet, and P. Dubreuil, “Deep trench MOSFET structures study for a 1200 volts application,” in Proc. Eur. Conf. Power Electron. Appl., 2007, pp. 1–9. [4] T. Fujihira, “Theory of semiconductor superjunction devices,” Jpn. J. Appl. Phys., vol. 36, no. 10, pp. 6254–6262, Oct. 1997. [5] S. Pendharkar, R. Pan, T. Tamura, B. Todd, and T. Efland, “7 to 30 V stateof-art power device implementation in 0.25μm LBC7 BiCMOS-DMOS process technology,” in Proc. ISPSD, 2004, pp. 419–422. [6] V. Khemka, V. Parthasarathy, R. Zhu, A. Bose, and T. Roggenbauer, “Floating RESURF (FRESURF) LDMOSFET devices with breakthrough BVdss-Rdson,” in Proc. ISPSD, 2004, pp. 415–418. [7] R. Zhu, V. Khemka, A. Bose, and T. Roggenbauer, “Stepped-drift LDMOSFET: A novel drift region engineered device for advanced smart power technology,” in Proc. ISPSD, 2006, pp. 333–336. [8] T. Nitta, S. Yanagi, T. Miyajima, K. Furuya, Y. Otsu, H. Onoda, and K. Hatasako, “Wide voltage power device implementation in 0.25μm SOI BiC-DMOS,” in Proc. ISPSD, 2006, pp. 341–344. [9] R. van Dalen and C. Rochefort, “Vertical multi-RESURF MOSFETs exhibiting record low specific resistance,” in IEDM Tech. Dig., 2003, pp. 737–740. Authorized licensed use limited to: Hong Kong University of Science and Technology. Downloaded on August 25, 2009 at 05:47 from IEEE Xplore. Restrictions apply.