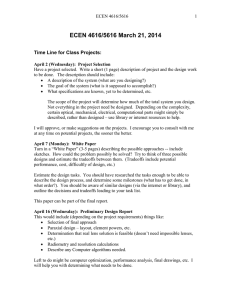

Package, Power and I/O

advertisement

ECEN454 Digital Integrated Circuit Design Package, Power and I/O ECEN 454 Outline Packaging Power Distribution I/O Synchronization ECEN 454 14.2 1 Packages Package functions Electrical connection of signals and power f from chip hi to t board b d Little delay or distortion Mechanical connection of chip to board Removes heat produced on chip Protects chip p from mechanical damage g Compatible with thermal expansion Inexpensive to manufacture and test ECEN 454 14.3 Package Types Through-hole vs. surface mount ECEN 454 14.4 2 BGA – Ball Grid Array Routable Laminate Substrate (Many Layers) High Pin Count (Over 2000 pins) ASICs, DSPs, PC Chipsets Wirebond, Flip-Chip (Build-Up) attach ECEN 454 14.5 Multichip Modules Pentium Pro MCM Fast connection of CPU to one or two external cache dices Expensive, requires known good dice (tested bare unpackaged ICs) ECEN 454 14.6 3 Chip-to-Package Bonding Traditionally, chip is surrounded by pad frame Metal pads on 100 – 200 m pitch Gold bond wires attach p pads to package p g Lead frame distributes signals in package Metal heat spreader helps with cooling ECEN 454 14.7 Advanced Packages Bond wires contribute parasitic inductance Fancy yp packages g have many y signal, g power p layers y Like tiny printed circuit boards Flip-chip places connections across surface of die rather than around periphery The bond wire is replaced with a conductive “bump” placed directly on the die surface Chip Chi flips fli upside id down d Carefully aligned to package Heated to melt balls Also called C4 (Controlled Collapse Chip Connection) ECEN 454 14.8 4 Advantages of Flip-Chip Reduced Signal Inductance Shorter Interconnect Lengths U P Use Power M More Effi Efficiently i tl Power Directly at the Core Higher Interconnect Density More Routable Area Smaller Package Size Chip Scale Packaging (CSP) I/O Not Controlling Core Size Area Array Placement Possible Die Shrink ECEN 454 14.9 Package Parasitics Use many VDD, GND in parallel Inductance, IDD Package Signal Pad ds Signal Pinss ECEN 454 Chip VDD Chip Chip GND Bond Wire Lead Frame Package Capacitor (d (decoupling) li ) Board VDD Board GND 14.10 5 Heat Dissipation 60 W light bulb has surface area of 120 cm2 Itanium 2 die dissipates p 130 W over 4 cm2 Chips have enormous power densities Cooling is a serious challenge Package spreads heat to larger surface area Heat sinks may increase surface area further Fans increase airflow rate over surface area Liquid cooling used in extreme cases ($$$) ECEN 454 14.11 Thermal Resistance T = jaP T: temperature rise on chip ja j : thermal resistance of chip junction to ambient P: power dissipation on chip Thermal resistances combine like resistors Series and parallel ja = jp + pa Series combination ECEN 454 14.12 6 Example Your chip has a heat sink with a thermal resistance to the package of 4.0° C/W. The resistance from chip to package is 1° C/W. The system box ambient temperature may reach 55° C. The chip temperature must not exceed 100° C. What is the maximum chip power dissipation? ECEN 454 14.13 Example Your chip has a heat sink with a thermal resistance to the package of 4.0° C/W. The resistance from chip to package is 1° C/W. The system box ambient temperature may reach 55° C. The ec chip p te temperature pe atu e must ust not ot exceed e ceed 100° 00 C C. What is the maximum chip power dissipation? (100-55 C) / (4 + 1 C/W) = 9 W ECEN 454 14.14 7 Power Distribution Power Distribution Network functions Carry current from pads to transistors on chip Maintain M i t i stable t bl voltage lt with ith low l noise i Provide average and peak power demands Provide current return paths for signals Avoid electromigration & self-heating wearout Consume little chip area and wire Easy to lay out ECEN 454 14.15 Power Requirements VDD = VDDnominal – Vdroop Want Vdroop < +/- 10% of VDD Sources of Vdroop d IR drops L di/dt noise IDD changes on many time scales Power Max clock gating Average Min Time ECEN 454 14.16 8 IR Drop and Electro-migration 1. IR drop: voltage at delivery point is degraded than the ideal voltage [Blaauw et al., DAC98] • performance drop • signal integrity problems 2. Electro-migration PowerPC 750 power grid PowerPC 750 IR-drop map ECEN 454 14.17 Transient Noise VDDIO VDDcore Power/Ground bouncing VSS ECEN 454 14.18 9 Power System Model Power comes from regulator on system board Board and package add parasitic R and L Bypass yp capacitors p help p stabilize supply pp y voltage g But capacitors also have parasitic R and L Simulate system for time and frequency responses Voltage Regulator VDD Printed Circuit Board Planes Bulk Capacitor Board Ceramic Capacitor Package and Pins Package Capacitor Solder Bumps On-Chip Capacitor Chip On-Chip Current Demand Package ECEN 454 14.19 On-chip Power Grid Model ECEN 454 14.20 10 Decoupling Capacitors Need low supply impedance at all frequencies Provide stable supply voltage even when current demands are high Bypass (decoupling) caps Without the impedances made out of resistors and inductances: larger for higher frequency Ideal capacitors have impedance decreasing with Real capacitors have parasitic R and L Leads to resonant frequency of capacitor 2 10 1 10 1 F 0.25 nH impedance 0 03 0.03 10 10 10 0 -1 -2 10 4 10 5 10 6 10 7 10 8 10 9 10 10 frequency (Hz) ECEN 454 14.21 Frequency Response Use multiple capacitors in parallel Large capacitor near regulator has low impedance at low frequencies But also has a low self self-resonant resonant frequency Small capacitors near chip and on chip have low impedance at high frequencies Choose caps to get low impedance at all frequencies impedance frequency (Hz) ECEN 454 14.22 11 Input / Output Input/Output System functions Communicate between chip and external world Drive D i large l capacitance it off ff chip hi Operate at compatible voltage levels Provide adequate bandwidth Limit slew rates to control di/dt noise Protect chip against electrostatic discharge Use small number of pins (low cost) ECEN 454 14.23 I/O Pad Design Pad types VDD / GND Output O t t Input Bidirectional Analog ECEN 454 14.24 12 Output Pads Drive large off-chip loads (2 – 50 pF) With suitable rise/fall times Requires chain of successively larger buffers Guard rings to protect against latchup Apply to transistors directly driving external circuitry Noise below GND injects charge into substrate Large (long) nMOS output transistor p+ inner guard ring n n+ outer guard ring In n-well ECEN 454 14.25 Input Pads Level conversion Higher or lower off-chip V May y need thick oxide g gates Noise filtering Schmitt trigger Hysteresis changes VIH, VIL VDDH A VDDL Y VDDL A Y weak A Y Y weak A Protection against electrostatic discharge ECEN 454 14.26 13 ESD Protection Static electricity builds up on your body Shock delivered to a chip can fry thin gates Must dissipate p this energy gy in protection p circuits before it reaches the gates Diode clamps ESD protection circuits Current limiting resistor Diode clamps R PAD Current limiting resistor ESD testing ~kVs Human body model Views human as charged capacitor Thin gate oxides 1500 100 pF Device Under Test ECEN 454 14.27 Bidirectional Pads Combine input and output pad Need tristate driver on output Use enable signal to set direction Optimized tristate avoids huge series transistors PAD En Din Dout NAND Dout Compacter Design Y En Dout NOR ECEN 454 14.28 14 Analog Pads Pass analog voltages directly in or out of chip No buffering Protection P t ti circuits i it mustt nott distort di t t voltages lt RF pads are extremely demanding, because any extra load can compromise performance ECEN 454 14.29 MOSIS I/O Pad 1.6 m two-metal process Protection resistors Protection diodes Guard rings Field oxide clamps PAD 600/3 264 185 Out 240 48 90 160 20 40 In En Out In_unbuffered ECEN 454 In_b 14.30 15