Electronics Circuits 1 JFET amplifier and biasing

advertisement

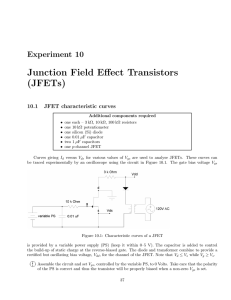

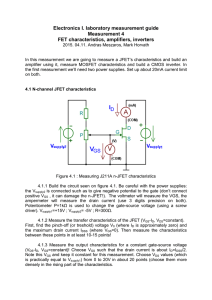

Andrzej Materka Electronics Circuits 1 JFET amplifier and biasing Telecommunications and Computer Science 90-924 Łódź, ul. Wólczańska 211/215 tel. 42 631 2626, 42 636 0065 www.eletel.p.lodz.pl n-channel, junction field-effect transistor (FET) Drain D Channel Gate p n p G S Source Physical structure Circuit symbol A. Materka, Electronics Circuits 1, JFET Amplifier and Biasing 2 n-channel, junction FET iD (mA) iD Linear region D G + vGS vDS Saturation region vGS=0 10 + vGS=-1V 5 S vGS=-2V Circuit for discussion of DC characteristics 0 0 5 10 vDS (V) Cutoff vGS<VP Drain DC characteristics of an n-channel JFET A. Materka, Electronics Circuits 1, JFET Amplifier and Biasing 3 n-channel, junction FET Cut-off region iD (mA) iD 0, vGS VP Linear region Saturation region vGS=0 10 Linear region 2 i D K 2vGS VP v DS v DS vGS VP and vGD (vGS v DS ) VP vGS=-1V 5 vGS=-2V iD 0 0 5 10 vDS (V) Cutoff vGS<VP Saturation region Spice model parameters I DSS 2 iD 2 vGS VP , VP I DSS 2 =„Beta”, Vp=„Vto” VP vGS VP vGS V P and Transfer characteristic vGD (vGS v DS ) V P in saturation Typical for low-power JFET: IDSS=5mA, VP=-3V A. Materka, Electronics Circuits 1, JFET Amplifier and Biasing 4 Simple JFET amplifier iD RD 1k D G + vin(t) iD (mA) + 20V vDS VDD Load line 20 A sin(2000t) VGG vGS vGS=0 S + Q-point 10 vGS=-1V 1V vGS (t ) vin (t ) VGG B vGS (t ) sin(2000t ) 1 VDD RDi D (t ) v DS (t ) 20 iD (t )[mA] vDS (t ) 0 0 10 VDSmin=4V vGS=-2V 20 vDS (V) VDS=11V VDSmax=16V The output waveform is not a symmetrical sinusoid like the input (nonlinear distortion). A. Materka, Electronics Circuits 1, JFET Amplifier and Biasing 5 Simple JFET amplifier , VG =-1V Model tranzystora FET .model JF NJF(Beta=1m Vto=-4V) VD VG Voltage gain is rather modest (Av ≈ -6), current gain tends to infinity. A. Materka, Electronics Circuits 1, JFET Amplifier and Biasing 6 Simple JFET amplifier, VG =-2V Model tranzystora FET .model JF NJF(Beta=1m Vto=-4V) VD VG Av ≈ -4 A. Materka, Electronics Circuits 1, JFET Amplifier and Biasing 7 Simple JFET amplifier, VG =-2V Model tranzystora FET .model JF NJF(Beta=1m Vto=-4V) VD VG Av ≈ -2 A. Materka, Electronics Circuits 1, JFET Amplifier and Biasing 8 iD RD D G + vin(t) JFET amplifier 1k vDS + 20V VDD sin(2000t) VGG vGS S + 1V Both the gain and distortion depend on bias (on selection of Q-point – quiescent point of transistor operation). A. Materka, Electronics Circuits 1, JFET Amplifier and Biasing 9 iD RD D G + vin(t) vGS + + 20V vDS sin(2000t) VGG JFET amplifier 1k S VDD Both the gain and distortion depend on bias (on selection of Q-point – quiescent point of transistor operation). 1V Analysis of amplifiers is done in two steps: - determination of the Q-point (using a nonlinear device model), - finding the input resistance, voltage gain, etc. (linear ac analysis using a small-signal equivalent circuit). A. Materka, Electronics Circuits 1, JFET Amplifier and Biasing 10 iD RD D G + vin(t) vDS sin(2000t) VGG vGS + JFET dc bias 1k S + 20V VDD Two-battery bias circuit is not practical (usually one battery is available only). iD 1V Values of JFET parameters vary considerably from device to device, e.g. IDSS may vary by a ratio of 5:1, the pinch-off voltage is different from device to device. ID ID Fixed-bias circuit (maintaining a constant VGS) is not suitable. It would lead to a considerable variation of ID. The Q-point would be located far from the middle of the load line, causing considerable output waveform distortion and a loss of gain from device to device. vGS VGS A. Materka, Electronics Circuits 1, JFET Amplifier and Biasing 11 iD JFET self-bias circuit RD D G vGS RG RS + vDS VDD iD Neglecting the gate current one has S vGS RS i D RSiD Bias line vGS=-RSiD Graphical analysis of the self-bias circuit The device-to-device variation of drain current is much less than for the fixed-bias circuit. vGS VGS VGS VDD is of such a value that VDS is large enough for operation in the saturation region. A. Materka, Electronics Circuits 1, JFET Amplifier and Biasing 12 JFET self-bias circuit iD RD D G vGS RG RS + vDS S RSiD VDD Exercise 4.1 Design a self-bias circuit for an n-channel FET having IDSS =4mA and VP =-2V. The circuit is to have RD =2.2k, VDD =20V, and ID 2mA. Use standard 10%tolerance resistor values. Answer: RS=270. Exercise 4.2 Analyse the self-bias circuit designed in Exercise 4.1. Repeat the analysis for a high-current device having IDSS=8mA and VP=-4V. Verify your results with SPICE. Answer: VGS=-0.56V, ID=2.07mA, VDS=14.9V; VGS=-1.12V, ID=4.14mA, VDS=9.77V. A. Materka, Electronics Circuits 1, JFET Amplifier and Biasing 13 iD The Fixed- Plus Self-Bias Circuit RD D R1 G VDD vDS vGS R2 + Gives better performance in maintaining a fixed ID from device to device. S RS RSiD - The Thevenin voltage: VG VDD iD - The Thevenin resistance: RG = R1 || R2 RD D RG G vGS VG RS R2 R1 R2 + vDS S RSiD VG=0 corresponds to self-bias. VDD - Voltage equation: VG vGS RS i D (VRG 0) (4.17) 2 - Assumed saturation: i D KvGS V P (4.18) - Simultaneous solution of (4.17) and (4.18) yields the operating point. - v DS VDD ( RD RS )is A. Materka, Electronics Circuits 1, JFET Amplifier and Biasing 14 The Fixed- Plus Self-Bias Circuit iD RD D RG G vGS VG RS iD + vDS VDD S RSiD Equation (4.17) vGS VG Graphical solution for the fixed- plus self-bias circuit; ID is nearly independent of the device if VG is large. In practice, VG can not be too high because this raises the voltage drop across RS, and sufficient voltage must be allocated for vDS and RD. A. Materka, Electronics Circuits 1, JFET Amplifier and Biasing 15 The Fixed- Plus Self-Bias Circuit iD RD D RG G vGS VG RS + vDS S RSiD VDD Exercise 4.3 Design for VG5V a fixed- plus self-bias circuit for the JFET of Exercise 4.1 having IDSS=4mA and VP=-2V. The circuit is to have RD=2.2k, VDD=20V, and ID2mA. Use standard 10%-tolerance resistor values. Answer: RS=2.7k. Exercise 4.4 Analyse the self-bias circuit designed in Exercise 4.3. Repeat the analysis for a high-current device having IDSS=8mA and VP=-4V. Verify your results with SPICE. Answer: VGS=-0.564V, ID=2.06mA, VDS=9.9V; VGS=-1.76V, ID=2.50mA, VDS=7.73V. A. Materka, Electronics Circuits 1, JFET Amplifier and Biasing 16