PDF - UNT Digital Library

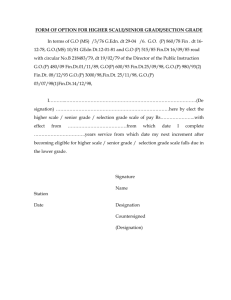

advertisement