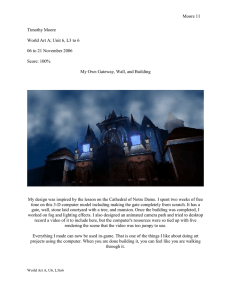

more moore - Semiconductor Industry Association

advertisement