Document

advertisement

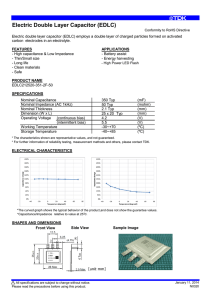

元件電路計測實驗 Device and Circuit Characterization Lab. Tuo-Hung Hou Department of Electronics Engineering & Institute of Electronics National Chiao Tung University Note 4 Fall 2011 1 Impedance Measurement 2 Impedance ¾ An important parameter to characterize electronic components and circuits ¾ Total opposition a device or circuit offers to the flow of an alternating current at a given frequency Z V = I 3 Impedance Vector Imaginary Axis Z(R, X) X IZI Z = R + jX = Z e jθ R = Z cos θ X = Z sin θ θ R Real Axis Z = R2 + X 2 ⎛X ⎞ ⎟ R ⎝ ⎠ θ = tan −1 ⎜ Z consists of a real part (R: resistance) and an imaginary part (X: reactance) 4 Reactance R jX 1 1 Capacitive : jX = =−j = − jX C jω C s ωC s Inductive : jX = jωLs = jX L wh ere ω = 2πf 5 Admittance: Reciprocal of Impedance R jX Z = R + jX (Impedance is convenient to use) R (G) jRX RX 2 R2 X = 2 +j 2 Z= 2 R + jX R + X R + X2 (Impedance makes it a bit complex) jX (B) Y = G + jB (Admittance is more convenient to use) Y consists of a real part (G: conductance) and an imaginary part (B: susceptance) 6 Susceptance G jB Capacitive : jB = jωC p = jBC 1 1 Inductive : jB = =−j = − jBL ωL p j ωL p where ω = 2πf 7 Quality Factor and Dissipation Factor ¾ Quality factor and dissipation factor are used to measure the purity of inductance and capacitance, respectively. • Inductive vector represented in impedance plane and admittance plane 1 1 X = = L D tan δ R 1 1 B Q= = = L D tan δ G Q= • Capacitive vector represented in impedance plane and admittance plane X 1 1 = = C D tan δ R B 1 1 Q= = = C D tan δ G Q= 8 Parasitic Impedance ¾ A real-world device has parasitic components. ¾ Measured value is different from real value. • Real value can be extracted from correct equivalent circuit model and suitable system setup and measurement condition. Real world component Real world capacitor Real Value Test fixture instrument Measured Value 9 Equivalent Circuit R C Rm R Cm C 1 C R = R + m 1 + ω 2 R 2C 2 ω 2 RC 2 Example : C = 1000 pF R = 100Ω Cm = 717 pF at f = 1MHz Cm = Cm = 996 pF at f = 100 KHz 1 ω 2 R 2C Example : Cm = C + Rm Rm = Cm R 1 + ω 2 R 2C 2 C = 100 pF R = 106 Ω Cm = 100 pF at f = 1MHz Cm = 100.03 pF at f = 100 KHz 10 The Role of Dissipation Factor 11 Series or Parallel Circuit Mode? ¾ Selection of circuit mode depends on which factor is the main contributor of loss. ¾ Series mode is used for low impedance samples (large capacitance or small inductance). ¾ Parallel mode is used for high impedance samples (small capacitance or large inductance). Rp Large C Rs Rp Small C Rs 12 Equivalent Circuit Selection ¾ Equivalent circuit selection criteria in auto-mode. Rule of Thumb: Above ~10k Ohm : Parallel mode Below ~10 Ohm : Series mode 13 Impact of Series Resistance (See the Schroder book, Chap 2) 14 MOS Capacitance Measurements for Leaky Dielectrics - Two-Frequency Method R Z = rs + Rp R (1 − jw C R ) 1 + w 2C 2 R 2 Z= D− j wC p (1 + D 2 ) D = 1 wR p C p 1+ w C R 2 2 = w C (1 + D ) p 2 CR 2 C= 2 2 f12C p1 (1 + D12 ) − f 22C p 2 (1 + D22 ) f12 − f 2 2 (K. Yang and C. Hu, IEEE TED, July 1999) 15 Capacitance & Impedance Measurement RF vi G jωC Z =− = 2 − 2 2 2 v0 G + (ωC ) G + (ωC ) 16 Capacitance & Admittance Measurement ii − vo RF Y= = = G + jwC vi vi 17 Four Terminal Pair Reduces effects of cable inductance Stimulus and Sense are separate 18 Correction/Calibration 19 Cable Length Effect ¾ Test cables for connecting a sample will cause a phase shift and a propagation loss of the test signal. ¾ Example • The wavelength of a 10 MHz signal is 30m. • The phase shift is about 12 degree for a 1m cable. • Additional error is proportional to the square of the frequency and is 3% for each 10cm change at 10MHz. θ 2 − θ1 = 2πl λ (radian) 20 MOS Capacitors (MOSC) E0 1.0eV E0 χox ΦM Flat-band condition (no field in silicon) according to the approximation χsi 3.0eV ΦS EC EF EM EV 9.0eV 4.9eV Φ MS 1 = (ΦM − ΦS ) = 0 q Oxide is treated as a very wide bandgap semiconductor without current flowing or charges. ΨF At thermal equilibrium, EF flat Band Flat →Charge neutrality: n- = ND+ 21 Capacitance-Voltage (C-V) Characteristics of a MOS Capacitor Vg N+ Qg Qs P dQ g dQ s C= =− dV g dV g ¾ The capacitance in the MOS theory is always the smallsignal capacitance. ¾ The capacitance is measured by superimposing a smallsignal ac voltage (with ~15 mV amplitude) on an applied dc gate bias. ¾ The capacitance is a function of the applied dc gate bias. 22 Semiconductor Capacitance: Cs Vg = VFB + ϕ s + Vox dϕ s dVox = + dQg d (− Qs ) dQg dVg 1 1 1 = + C Cs Cox dQs where Cs = − dϕ s 23 MOS CV: LFCV, HFCV and DD C/Cox LFCV vss VG Metal Oxide 1 Minority carrier can follow VG and vss Si Flat band will have a little smaller C depending on the size of vss Inv. Dep. HFCV VG (quiescent point) Cox Csi Inverted minority carrier can follow VG but not vss dQ s C si = dψ s deep depletion Minority carrier cannot follow either VG or Vss Acc. VG Vth 24 Accumulation and Depletion ρ VG>0 EC EF Accumulation EM EV electron sheet charge Cox Cox = ρ VG<0 EM EC EF EV ∇ 2ψ = − Depletion (before Ei passes the Fermi level) donor charge ε oxε 0 A tox VG Cox Csi ρ q n − p − N D+ + N A− + nT ) = ( ε ε siε 0 Surface bending (Ψs) → Charge pile up VG Csi = ε wiε 0 A 25 W MOS C-V: Inversion VG<0 EM At the surface, it is as much p as it is n in the Si bulk EC EF EV Onset of Inversion (VG=Vth) Carrier Screening!!! VG<0 EM EC EF EV ρ Strong Inversion (|VG|>|Vth|) inverted holes donor charge Wdm ρ The depletion region stops growing. Any further charge is mostly compensated by the inverted minority carriers. donor charge Wdm inverted electrons 26 Charge Response in LFCV, HFCV and DD Accumulation ρ ac charge response dc charge response Depletion C depl = ρ W = 1 1 1 + C ox C si 2ε si ε 0 ψs qN A C ox = 1+ ε ox W ε si t ox W dm = 2ε si ε 0 2ψ F qN A W LFCV ρ Deep Depletion ρ HFCV ρ Inversion Wdm Wdm The DC VG is swept very fast (<0.01s), the inverted minority carriers do not have time to be thermally generated. Wdm 27 Substrate Type invers. depl. 0 ¾ N-type substrate (PMOS): accumul. VG ¾ P-type substrate (NMOS): accumul. 0 depl. invers. VG C/Cox C/Cox p-type bulk (NMOS) n-type bulk (PMOS) VG VG VG VG 28 C-V Curves Accumulation dQs C= dVg Inversion Quasi static High frequency Sweeping Direction 29 Nsub Extraction - Cmax and Cmin Method W dm 1 1 1 1 = + = + C min C ox C dm C max εs W dm = 2ε si ε 0 2ψ F qN A kT ⎛ N A ⎞ ψ F = ln ⎜ q ⎝ ni ⎟⎠ kT ⎛ N D ⎞ = − ln ⎜ q ⎝ ni ⎟⎠ Vg Cox C Cdep p − type(NMOS) 0 n − type(PMOS) 30 Nsub Extraction – Differential Capacitance Method 1 qN A W dep 2 ϕs = 2 εs Qdep qN AWdep Qs Vox = − =− = C ox C ox C ox V g = V FB + ϕ s + Vox = V FB qN AWdep 1 qN A 2 Wdep + + 2 εs C ox (1) ⇒ Wdep (V g ) ⇒ ϕ s (V g ), Vox (V g ) 31 Nsub Extraction – Differential Capacitance Method (Cont.) W dep 1 1 1 d = + = + εs C C ox C dep ε sio2 1 1 1 ( ) ∂ ∂( 2 ) ∂( ) C = − 2 C = − 2 C dep = − 2 ∂ W dep ∂V g C ∂V g C ∂Vg C ε s ∂V g From (1) dW dep dV g = qN A (W dep 1 C = / ε s + 1 / C ox ) qN A 1 ) 2 2 ∴ C =− ∂V g qN Aε s ∂( N A (W dep ) = − 2 1 qε s [ ∂ ( 2 ) / ∂ V ] C 32 Quasi-Static CV Measurement for an MOS Capacitor Vg = A ⋅ t Ig = C dV g dt Vg = A ⋅ C (V g ) t ¾ The ramp rate A is very slow (typically in the range of 5 to 50 mV/sec) to provide sufficient time for Qinv to respond to Vg. ¾ For MOS capacitors with thin gate oxide and large gate leakage, this technique cannot be used. 33 Notes on C-V Measurement ¾ In order to let inversion charges be able to response with the gate voltage (dV dt ) dV qniWd ≤ ⇒ f = dt τ g COX eff 2V pp ¾ For a capacitor at 300K with Wd=1um, Tox=100nm, and Vpp=30mV τ g = 10μ sec τ g = 1m sec dV ≤ 0.65V / sec dt f eff = 11Hz dV ≤ 6.5mV / sec dt f eff = 0.11Hz ¾ In general case, high frequency C-V is obtained but deep depletion is usually observed. 34 Notes on C-V Measurement ¾ In general, deep depletion is often observed in HF CV measurement. ¾ If DC bias sweeps from low Vg to high Vg, sweep rate should be low enough to avoid deep depletion. ¾ If DC bias sweeps from high Vg to low Vg, device should be biased at high Vg either for a long time or been illuminated to form inversion layer. ¾ If dissipation factor is higher than 0.1, the capacitor is leaky and the equivalent circuit correction needs to be considered. 35 Vg C LF Linear ramp + ac signal I. HF t LF: n in equilibrium with ϕs (V g ) DD Vg n LF n : nbias (V gbias ) + n ac (V gac ) t II n HF: n: nbias (Vgbias) n ac =0 III Deep Depletion: n: t ϕS n nbias=0 n ac =0 ϕs≤2 ϕB HF Wdep ≤ Wdmax C ϕs>2 ϕB HF 2ϕ B t Wdep > Wdmax DD t Vg 36 Time Constant of Establishing the Inversion Layer as a Monitor of Carrier Generation Lifetime C B 37 Carrier Transport Through Insulators ¾ Thermionic emission ( ⎛ − q φ B − qF / 4πε insε 0 J = ℜ T exp⎜ ⎜ kT ⎝ * 2 )⎞⎟ ⎟ ⎠ ⎛ a V qφ B ⎞ ⎟ I ∝ T exp⎜⎜ − ⎟ T kT ⎠ ⎝ 2 • important for FB around 0.4eV-0.8eV or when the insulator field is small ¾ Frenkel-Poole emission ( ⎛ − q φB − qF / πεins ε0 J ∝ F exp⎜ ⎜ kT ⎝ )⎞⎟ ⎟ ⎠ ⎛ 2a V qφB ⎞ ⎟ I ∝ V exp⎜⎜ − kT ⎟⎠ ⎝ T • important for insulators with lots of traps such as nitride and polymer. Carriers in traps can be thermally activated or hopping (tunneling) to the next trap location ¾ Field emission (Fowler-Nordheim or F-N tunneling) ⎛ − 4 2m* (qφ )3 / 2 ⎞ B ⎟ J ∝ F exp⎜ ⎜ ⎟ 3qhF ⎝ ⎠ 2 ⎛ b⎞ I ∝ V exp⎜ − ⎟ ⎝ V⎠ 2 • important for thick oxide (tox>3nm), especially when oxide field is large tunneling through triangular barrier 38 Carrier Transport Through Insulators ¾ “Direct” tunneling ( 3/ 2 3/ 2 * ⎛ ( ) ( ) − m q φ − q φ − qFt 4 2 B B ins J ∝ F 2 exp⎜ ⎜ 3qhF ⎝ )⎞⎟ ⎟ ⎠ tunneling through trapezoidal barrier • important for thin oxide (tox <2nm), especially when oxide field is large ¾ Space-charge limited current 8ε insε 0 μV 2 J= 9tins I ∝V 2 • important for small barrier height and large charge density possible in insulator (e.x., intrinsic semiconductor) ¾ Ohmic ⎛ ΔE ⎞ J ∝ F exp⎜ − ae ⎟ ⎝ kT ⎠ ⎛ C⎞ I ∝ V exp⎜ − ⎟ ⎝ T⎠ ΔEae : activation energy of electrons • important when thermally activated electrons are responsible for conduction ¾ Ionic J ∝ F exp⎛⎜ − ΔEai ⎞⎟ T ⎝ kT ⎠ I∝ V ⎛ C⎞ exp⎜ − ⎟ T ⎝ T⎠ ΔEai : activation energy of ions • important when thermally activated ions are responsible for conduction 39 Gate SiO2 Leakage ¾ Since the thermal oxide is very pure, and the hydrogen passivated Si/SiO2 interface is one of the best surfaces available, the gate leakage is usually dominated by F-N or direct tunneling. ¾ If we use a plane-wave approximation, then the transmission probability can be calculated with the WKB (Wentzel-Kramers-Brillouin) model: h 2α 2 V ( x) − E = 2m h 2k 2 E= 2m h 2k 2 E= 2m T (E ) = x1 eikx e-ikx Transmission probability: V(x) x2 e-αx x2 ⎛ exp ⎜⎜ − 2 ∫ dx x1 ⎝ ⎛ x ⎛ ⎜ 1 + 1 exp ⎜ − 2 2 dx ∫ ⎜ ⎜ x1 4 ⎝ ⎝ ⎞ 2m (V ( x ) − E ) ⎟⎟ 2 h ⎠ ⎞⎞ 2m (V ( x ) − E ) ⎟⎟ ⎟⎟ 2 h ⎠⎠ eikx 40 2 Gate Current Sample simulation and measurement of thin oxide tunneling current with both F-N and direct tunneling (line: calculation; symbols: measurement) F-N Direct non-tunneling mechanisms F-N tunneling is more dominant in thicker oxide and has a larger dependence on the electric field. Direct tunneling current is small except in the 1.5nm case. Below 1.5nm, the oxide current will increase 3 times for every Å reduction. Measurement data from Momose et al., IEEE Trans. Electron Devices, 43 (8), 1233 (1996). 41