The Design and Optimization of Low

advertisement

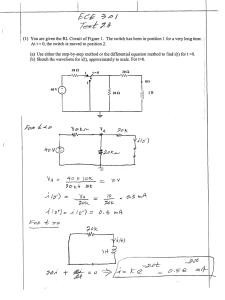

2016 UKSim-AMSS 18th International Conference on Computer Modelling and Simulation The Design and Optimization of Low-Voltage Pseudo Differential Pair Operational Transconductance Amplifier in 130 nm CMOS Technology Fadi R. Shahroury, and Ishraq Riad Princess Sumaya University for Technology Department of Electrical Engineering Amman, Jordan fadi@psut.edu.jo the transistor device size and the supply voltage. This improvement is positively reflected on the power delay product (PDP) of the digital circuit. On the other hand, the analog circuit’s performance in terms of voltage swing, gain, and power consumption are not beneficial in scaling CMOS technology. However, in designing a low cost chip, the analog circuits, RF, and digital circuits should be implemented on the same chip. Thus, many topologies have been proposed to improve analog circuit’s performance at the expense of the circuit’s complexity. Other issue to be considered for nano-scale CMOS technology, is designing an OTA with certain specifications which could be challenging especially when the designer is caught between studying the equations of simple models and applying them to accurate short channel models, where there are an enormous number of parameters that are very hard to control in the designing process. That is why the most common way to characterize the transistor is tweaking in order to arrive at the desired performance. Thus, time to market will increase and consequently the final design cost. With the noticeable improvement in computer workstations, as well as evolutionary algorithms (EC), dealing with the above issues became much easier. Where the cost function of the EC can evaluated in the form of simulation-based rather than equation-based, where a circuit simulator is employed to evaluate the cost function repeatedly. This would increase the precision of the final results, if it compare with equation-based method. In this work a low-voltage OTA, which is designed by Imperialist Competitive Algorithm (ICA) as the EC and HSPICE as the circuit simulator, is proposed. The proposed design approach provides an accurate and usefulness design methodology, because it is based on the simulation results and the model technology library. The low-voltage OTA is discussed in Section II, the introduction of ICA is addressed in Section III. The simulation results of proposed pseudo differential pair Abstract—This paper presents low-voltage pseudo differential pair operational transconductance amplifier (OTA) circuit designed and simulated in 130 nm CMOS technology. The imperialist competitive algorithm (ICA) is used to optimize the DC gain, common-mode rejection ratio (CMRR), and power dissipation of the presented OTA. The cost function of ICA is evaluated in the form of simulation-based rather than equation-based to increase the precision of the final results. The simulation results after optimization show that the proposed OTA has DC gain of 37.5 dB, CMRR of 37.5 dB, and maximum signal swing at the output of 210 mV, with power consumption of 200μW from power supply of 0.5 V. Keywords-pseudo OTA, ICA, Optimization, Evolutionary algorithms. I. I NTRODUCTION The operational transconductance amplifier (OTA) plays a key role in the design of analog circuits such as filters, automatic gain controls, analog to digital converters (ADC), and digital to analog converters (DAC). In nano-scale complementary metaloxidesemiconductor (CMOS) technology, designing high performance analog integrated circuits is a challenging issue as the supply voltage shrinks due to transistor channel length reduction. However, the nanoscale CMOS technology enhanced the performance of IC design especially for the communication system, which consists mainly of three circuits, RF circuit, analog circuit, and digital circuit. In continuing technology feature size scaling requires a proportional downscaling of the supply voltage to maintain device reliability. At the same time, a relatively large threshold voltage (VT ) needs to be maintained to limit the off current [1] in transistors. These two factors pose significant challenges for the design of analog circuits in future standard CMOS processes. The nano-scale technology improves the performance of the RF front-end circuit through increasing unit-gain frequency (fT ) of the transistor device, which has a high impact on the design of RF circuit, and the performance of digital circuit is also improved through reducing 978-1-5090-0888-9/16 $31.00 © 2016 IEEE DOI 10.1109/UKSim.2016.17 355 361 OTA is reported in Section IV, followed by a conclusion in Section V. pair as high as possible, the modified pseudo differential pair OTA shown in Fig. 2 is used. In Fig. 2 the pseudo differential pair OTA consists of four main circuits: Gm stage, active load circuit, gain-boosting circuit, common-mode forward feedback (CMFF) circuit. The Gm stage (M1 and M2) is a differential input that converts the input voltage to current flowing through the active load circuit (M3 and M4). It is noticed that differential and common gain of the OTA are highly dependent on the impedance of the active load. Thus; to improve CMRR the impedance of the active load of the OTA should be maximized as possible in the differential mode, while it should be minimized as possible in the common mode. As depicted in Fig. 2. The impedance of the active load in the differential mode is equivalent to ro1,2 ||R1||ro3,4 ||ro5,6 ||ro7,8 , since the node K behaves as virtual ground in the differential mode. Meanwhile, the impedance of the active load of the common-mode 1 , as a result of is given by ro1,2 ||ro3,4 ||ro5,6 ||ro7,8 || gm3,4 the gate and drain voltage of the active load transistors M3 and M4 being equal in common-mode. Thus, the active load transistors behave as low-impedance diode connected device. II. L OW- VOLTAGE OTA A. Pseudo Differential Pair OTA The pseudo OTA differential architecture is used intensively in literatures [2], [3], [4], to reduce the required supply voltage. As illustrated in Fig. 1 (a), The signal swing is determined by the overdrive voltage, Vov , of the input transistors M1 and M2, and the active current-source load transistors M3 and M4. The minimum and maximum acceptable single-ended input levels to the OTA are Vth N and Vth N + Vov P , respectively. Where Vth is the threshold voltage of MOS device, and the subscripts N and P denote the NMOS and PMOS, respectively. Besides, the maximum output voltage swing is [VDD − (Vov N + Vov p )]. The small-signal, low-frequency differential gain for both of pseudo OTA and conventional OTA, is illustrated in Fig. 1 (b), is the same and given by gmN (roN ||roP ), where the gm and ro are the transconductance and small-signal output of MOS device, respectively. However, the small-signal, low-frequency common-mode (CM) gain for the conventional OTA is better than pseudo OTA, where the tail current-source transistor M5 helps to minimize the CM gain by a factor of (1 + gm1 ro5 ), with compare to CM gain of pseudo OTA. Therefore, to improve the The commonmode rejection ratio (CMRR) of the pseudo OTA, the biasing voltage (Vb ) of M3 and M5, must be controlled using the CM input or output signal of the OTA. Figure 2. The proposed differential pair transconductance amplifier. To improve the differential gain a cross-coupled transistor pair (M5 and M6) are used. The cross-coupled 1 in transistor pair exhibits a negative resistance of gm5,6 the differential mode. This negative resistance placed in parallel with a active load resistance, consequently the differential gain of the circuit is enhanced. Simultaneously, the common-mode gain is enhanced, because the cross-coupled transistor behaves as a diode-connected transistor in the common mode. Further, two major issues should be considered in the design of the circuit; first, to attain a stable circuit, the positive feedback which encompasses crosscoupled transistor pair should be weak, which means 1 gm5,6 ro1,2 ||ro3,4 ||ro5,6 ||ro7,8 ||R1. Second, M5 and M6 should operate in the saturation region. Therefore; Figure 1. The differential pair transconductance amplifier a) Pseudo b) with tail current-source. B. Proposed pseudo differential pair OTA In order to improve the CMRR, which is a major drawback in the pseudo differential pair OTA, while sustaining the differential gain of the pseudo differential 362 356 a current source I1 is added at node K to increase the DC voltage at nodes Voutn, and Voutp. To strengthen CMRR of the OTA, a conventional common mode feedback (CMFB) circuit is often used [13]. The task of CMFB is divided into three operations: sensing the output common mode (CM) level, comparison with a reference voltage, and returning the error to the amplifier’s bias network. Nevertheless; CMFB suffers from a crucial drawback, which is area and power hungry [14]. For this reason CMFF is sued in this work. In Fig. 2, the CMFF circuit consists from M7, M8, M9, M10, and M11, the CM sensing through transistor M10 and M11. Where transistors M10 and M11 operate in deep triode region, introducing a total resistance between node X and ground equal to: Rtotal = Ron10 ||Ron11 = III. I NTRODUCTION OF I MPERIALIST C OMPETITIVE A LGORITHM The conventional OTA circuit shown in Fig. 1 (b) consisted from a small number of transistors (5 transistors). Therefore, it was easy to optimize it, but for the proposed low-voltage OTA, the circuit consists of a large number of transistors almost 12 transistors. Thus, it is difficult to optimize these transistors. For that reason, imperialist competitive algorithm is used as evolutionary algorithms to deal with this multidimensional case. The ICA is a kind of newly EA algorithm, first proposed in [6]. ICA has highlighted by many researchers who extended it to many field such as circuits design, machine learning, optimization ets. [7], [8], [9], [10]. The flowchart of ICA, shown in Fig. 3, introduces the idea of imperialistic competitions. The ICA starts with initial states defined as countries, the countries are produced randomly at the beginning. Then, the counties are divided into two groups imperialist country and colony based on the cost function (the power) of each country. Each empire consists of an imperialist country and a number of colonies. After dividing, each colony starts to move toward his relevant imperialist country. Through movement of the colonies toward their imperialist country, the total power of the empire changes. The total power of the empire is a function of the imperialist country and its colonies power. Under the inspiration of imperialistic competitions, the empire, which is not able to increase or maintain his power, at least, will collapse. Eventually, for conversion solution, all the countries converge to a state where there is only one empire. 1 . μn COX W L (Vinn +Vinp −2Vth ) (1) Where μn COX and are transistor aspect ratio, respectively. Eq. 1 indicates that Rtotal is a function of Vinn +Vinp but independent of Vinn −Vinp . Thus, if the output change differentially, one of the Ron increases and the other decreases, so Rtotal will not change. Whereas, if they rise together, then Rtotal drops, so does Vx , thereby ID9 increasing the drain currents of M7M9 and lowering the output common-mode level. The small-signal, low-frequency common-mode gain of the proposed OTA Fig. 2 is given as: W L ACM = gm1 . (2) gm3 + gm5 + gds1 + gds3 + gds5 + gds7 IV. S IMULATION R ESULTS For the small-signal, low-frequency differential mode gain is equal: Adif f = −gm1 gds1 + gds3 + gds5 + gds7 − gm5 + 1 R1 The pseudo differential pair OTA, shown in Fig. 2, is design and optimized using MATLAB and HSPICE with the operation supply voltage of 0.5 V. The library of the device model used for simulation is 130 nm CMOS technology library. The ICA is used for optimization, where the total population size is 100 divided into 30 imperialist countries and 70 colonies. The optimization constrains are listed in Table I, It is also worth mentioning that the optimization is run under the restriction that all transistors must operate in the saturation region, except M10 and M11 should operate in triode region. The transient time simulation for the low-frequency common-mode and differential-mode are shown in Fig. 4 and Fig. 5, respectively. The summarized simulated parameters of the proposed OTA are listed in Table I. . (3) Thus, the CMRR is given as: gm3 + gm5 + gds1 + gds3 + gds5 + gds7 1 . gds1 + gds3 + gds5 + gds7 − gm5 + R1 (4) Finally to increase the voltage signal swing under the operation of low-supply voltage the overdrive reduction technique is used [5]. This can be done through separating the body and source terminals of transistors by using deep n-well process. This technique tolerates the reduction of the overdrive without utilizing low threshold voltage MOS device which requires extra fabrication process and further extra cost. CM RR = 363 357 Table I T HE CONSTRAINTS AND SIMULATED RESULTS OF PROPOSED OTA Constraints DC gain(dB) CMRR (dB) Signal swing (mV) Power consumption (μW ) Area (μm2 ) ≥ 20 ≥ 30 ≥ 150 minimize minimize Simulated results after optimization 37.5 37.5 210 200 1500 Figure 4. The transient simulation of the low-frequency commonmode for the proposed OTA. V. C ONCLUSION In this paper we presented Pseudo differential pair OTA which is suitable for low supply voltage, where the ICA is used to optimized the propose OTA under certain constraints and restrictions. The proposed optimization methodology is useful in calculating the design parameters for a fixed analog circuit topology. R EFERENCES [1] Itrs. the international technology roadmap for semiconductors (2004 edition. [Online]. Available: http://public.itrs.net Figure 3. Flowchart of the ICA [6]. Figure 5. The transient simulation of the low-frequency differentialmode for the proposed OTA. 364 358 [2] S.-S. E. Mohieldin, A.N. and J. Silva-Martinez, “A fully balanced pseudo-differential OTA with commonmode feedforward and inherent common-mode feedback detector,” IEEE Journal of Solid-State Circuits, vol. 38, pp. 663 – 668, 2003. [3] A. Emira and E. Sanchez-Sinencio, “A pseudo differential complex filter for Bluetooth with frequency tuning,” IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, vol. 50, pp. 742 – 754, 2003. [4] A. Kavala and P. Kondekar, “A Low Voltage, Low Power Linear Pseudo Differential OTA for UHF Applications,” in Proc. IEEE 4th International Symposium on Wireless Pervasive Computing (ISWPC’2009), Melbourne, VIC, 2009, pp. 1 – 4. [5] T.-Y. Chatterjee, S. and P. Kinget, “A 0.5 V filter with PLL based tuning in 0.18 um CMOS technology,” in Proc. IEEE International Solid-State Circuits Conference (ISSCC’2005)), San Francisco, CA, 2005, pp. 506 – 613. [6] E. Atashpaz-Gargari and C. Lucas, “Imperialist competitive algorithm: An algorithm for optimization inspired by imperialistic competition,” in Proc. IEEE Congress on Evolutionary Computation(CEC’2007)), Singapore, 2007, pp. 4661 – 4667. [7] B.-N. R. M. Gazafroudi, A.S and K. Afshar, “A hybrid model for wind power prediction composed of ANN and imperialist competitive algorithm (ICA),” in Proc. IEEE 22nd Iranian Conference on Electrical Engineering (ICEE’2014)), Tehran, 2014, pp. 562 – 567. [8] A.-S. F. N. Ahmadi, S and C.-H. Yeh, “ICLA imperialist competitive learning algorithm for fuzzy cognitive map: Application to water demand forecasting,” in Proc. IEEE International Conference on Fuzzy Systems (FUZZ-IEEE’2014)), Beijing, 2014, pp. 1041 – 1048. [9] T. G. T. Jafari, Mohammad Hossein and M. Jalali, “Solving cold start problem in tag-based recommender systems using discrete imperialist competitive algorithm,” in Proc. IEEE International Congress on Communication and Knowledge (ICTCK’2014)), Mashhad, Iran, Nov. 2014, pp. 1 – 7. [10] A. Pourmoosa and M. Mirsalim, “Equivalent circuit of Linear Induction Motor based on coupled-circuit model and optimization design using Imperialist Competitive Algorithm,” in Proc. IEEE 4th Power Electronics, Drive Systems and Technologies Conference (PEDSTC’2013)), Tehran, 2013, pp. 349 – 354. 365 359