V - MIT

advertisement

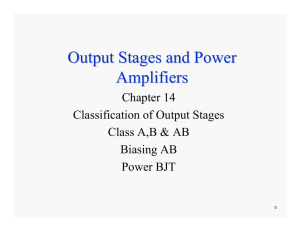

BJT Configurations Common Emitter Voltage Gain Current Gain Power Gain X X X X X Common Collector Common Base X Common emitter: hgh input impedance, for general amplification of voltage, current and power from low power, high impedance sources. • Bipolar Junction Transistor • Circuit Analysis: Amplifer & Feedback • Classic BJT Circuits Common collector: aka "emitter follower" for high input impedance and current gain without voltage gain, as in an amplifier output stage. Common base: low input impedance for low impedance sources, for high frequency response. Grounding the base short circuits the Miller capacitance from collector to base and makes possible much higher frequency response. Acnowledgements: John K Fitch, Neamen, Donald: Microelectronics Circuit Analysis and Design, 3rd Edition 6.101 Spring 2014 X Lecture 5 1 6.101 Spring 2014 Transistor Configurations Lecture 5 2 Gain vs Frequency TRANSISTOR AMPLIFIER CONFIGURATIONS +15V RL +15V R2 RL R2 + R2 +15V + + Vin R1 VOUT RE - - [a] Common Emitter Amplifier 6.101 Spring 2014 + Vin R1 RE - VOUT - - [b] Common Collector [Emitter Follower] Amplifier Lecture 5 + + + Vin + VOUT + + + + + R1 RE - [c] Common Base Amplifier 3 6.101 Spring 2014 Lecture 5 4 Expanded Hybrid π Miller Effect* – Common Emitter rx CM C [1 g m ( RC RL )] * Agarwal & Lang Foundations of Analog & Digital Electronics Circuits p 861 6.101 Spring 2014 Lecture 5 5 6.101 Spring 2014 Input Impedance and Frequency Response Lecture 3 6 Common Base Configuration log scale AV (dB) R V1 V2 C 0 -3dB slope = -6 dB / octave slope = -20 dB / decade log f 1 Av Av 1 j XC V2 j C j RC 1 V1 R j X C R 1 j C 1 sRC 1 High frequency cutoff f hi fHI or f-3dB Degrees PHASE LAG 0o 1 2RC -45o -90o log f fHI or f-3dB 6.101 Spring 2014 Lecture 2 7 6.101 Spring 2014 Lecture 5 8 Common Collector – Emitter Follower Biasing Common Collector (Emitter Follower) 0 g m r gm I CQ VTH +15V VTH 26mv • • 7.5 mA R2 R1 R1 R2 RB = R1||R2, VB = 15 A 2N3904 R1 1.0 k 7.5 mA VB = IBRB + 0.6V + 7.5V VB = [75 µA x 10k] + 0.6V + 7.5V VB = 750 mV + 0.6V + 7.5V VB = 8.9V B R’s=RB // RS Av v g m v if R's r o 1RE ; • • 6.101 Spring 2014 o 1 RE o 1ib RE vout ; vin ib R 's r o 1RE R's r o 1RE +15V 2N3904 IB RB Buffer with unity gain High input resistance driving low output resistance (current gain). Lecture 5 9 7.5 V VB [1.44R2 x R2] ÷ [1.44 R2 + R2] = 10kΩ R2 = 16.9 kΩ (use 16 kΩ) R1 = 1.44 R2 = 24.4 kΩ (use 24 kΩ) 6.101 Spring 2014 • • • • 6.101 Spring 2014 Lecture 5 Unity gain, low output resistance High input resist. Lecture 5 10 Cascode Amplifer Low Frequency Hybrid‐ Equation Chart High gain applications Moderate input resistance High output resistance [15 R1] ÷ [R1 + R2] = 8.9V 15 R1 = 8.9 x [R1 + R2] [15−8.9] R1 = 8.9 R2 R1 = 1.44 R2 [R1 x R2] ÷ [R1 + R2] = 10 kΩ 7.5 mA then Av 1 Β = 100, iB = 7.5ma/100 =‐ 75µa Using Thevenin equivalent, Two transistor amplifer: commom emitter (CE) with a common base Miller effect avoid by setting gain of CE stage low. CE stage provides high input impedance Common base (CB) provides gain without Miller effect; base is grounded. No Miller effect Miller effect High gain, better high frequency response Low input resistance 11 6.101 Spring 2014 Lecture 5 12 Objectives Three Stage – Push Pull Amplifier • Perform an analysis into the behavior of a complicated circuit using basic properties of BJT’s (npn, pnp) • Calculate gain of the system • Discuss crossover distortion issues in push‐ pull amplifiers • Understand feedback 6.101 Spring 2014 Lecture 5 13 6.101 Spring 2014 Three Stage Amplifer – Block Diagram Lecture 5 14 Q3‐Q4 Push Pull • Q3: Emitter Follower (positve cycle) • Q4: Emitter Follower (negative cycle) • Overall gain ~1 • Q3 & Q4 Vbe are always one diode drop • Crossover distortion about zero crossing Feedback 6.101 Spring 2014 Lecture 5 15 6.101 Spring 2014 Lecture 5 16 Q2 – High Gain Stage Q1 Analysis • Since last stage is an emitter follower, node n4 should be biased near zero volts. • Q2 is a common emitter configuration with a pnp transistor. • For pnp configuration, reverse the polarity of the voltages from a npn. 0 g m r gm gm I CQ 6.101 Spring 2014 I CQ VTH 38 * I CQ 1.5 3 Av 570 10 I CQ VTH 26mv VTH Av o RL o g m RL gm Lecture 5 17 6.101 Spring 2014 Key Observations Lecture 5 18 Classic BJT Circuits/components • • • • • • • • Crossover distortion caused by base emitter voltage. • Feedback results in overall gain independent of β 6.101 Spring 2014 Lecture 5 19 6.101 Spring 2014 Darlington Pair Matched transistors Short circuit protection Currrent mirror Schottky diode Baker Clamp Vbe multiplier Lecture 5 20 Matched Pair MPSA13 Darlington • Close electrical and thermal characteristics • Supermatched pairs also available • Used in differental amplifiers and measurement equipment 6.101 Spring 2014 Lecture 5 21 6.101 Spring 2014 Lecture 5 22 356 Op‐Amp Short Circuit Protection 7805 Regulator Short Circuit Protection • When voltage across R16 exceeds ~0.6 volt, Q14 diverts away base drive to Q15. • Note Darlington pair Q15, Q16 6.101 Spring 2014 Lecture 5 23 6.101 Spring 2014 Lecture 5 24 Current Mirror Schottky* Diode • Schottky diode formed with metal‐ semiconductor junction vs pn junction • Lower forward voltage drop: 0.15‐0.45 vs 0.6‐0.7 for pn junction • Almost zero reverse recovery times. • Used in 74LS series logic Low‐power Schottky * Walter Schottkly 6.101 Spring 2014 Lecture 5 25 6.101 Spring 2014 Baker* Clamps Lecture 5 26 Vbe Multipler • Reduces turn off time by limiting saturation • Baker Camp with diodes V ( R1 R2 ) VBE R2 • Baker clamp with Schottky diode *named by Richard Baker (1956); drawings from http://en.wikipedia.org/wiki/Baker_clamp 6.101 Spring 2014 Lecture 5 27 6.101 Spring 2014 Lecture 5 28