FCP190N60E MOSFET Bare Die

advertisement

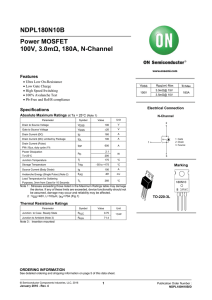

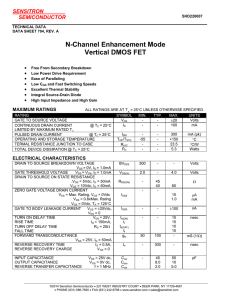

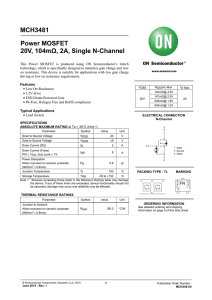

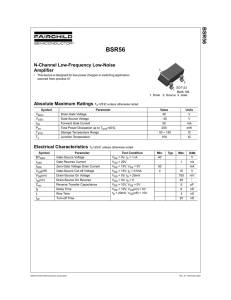

FCP190N60E N-Channel Charge Balance Mosfet Chip 600V, 20.6A, 190mΩ1 Part V(BR)DSS FCP190N60E IDn 600V RDS(on) Max 20.6A 190mΩ 1 Die Size 3.5 x 5.3 mm 2 See page 2 for ordering part numbers & supply formats Features Applications • High density AC / DC Converters • High Power & Current Handling Capability • Solar Inverters • Low RDS (on) per mm2 Maximum Ratings • Ultra low Gate Charge Symbol Parameter Ratings Units VDSS Drain to Source Voltage 600 V VGSS Gate to Source Voltage ID Drain Current 2 Drain Current3 IDM TJ, TSTG EAS ±20 -AC (f>1Hz) ±30 Continuous (TC = 25°C) 20.6 Continuous (TC = 100°C) 13.1 Pulsed 61.8 Operation Junction & Storage Temperature Single Pulsed Avalanche Energy Peak Diode Recovery dv/dt dv/dt -DC MOSFET dv/dt 4 4 V A -55 to 150 °C IAS=4A, VDD= 50V, RG=25Ω , Starting @ TJ =25°C 400 mJ ISD≤10A,di/dt≤200A/µs, VDD≤BVDSS, Start @ TJ=25°C 20 V/ns 100 V/ns 4 Symbol Parameter Test Conditions Min Typ Max Units BVDSS Drain to Source Breakdown Voltage ID = 10mA, VGS = 0V 600 - - V VGS(th) Gate threshold Voltage VGS = VDS, ID =250µA 2.5 - 3.5 V IDSS Zero Gate Voltage Drain Current VDS = 480V, VGS = 0V - - 1 µA IDSS Zero Gate Voltage Drain Current VDS = 480V, TC = 125°C - - 10 µA IGSS Gate to Body Leakage Current VGS = ±20V , VDS = 0V - - ±100 µA VGS = 10V, ID = 10A - 160 190 mΩ RDS(on) Static Drain to Source On Resistance 1. 2. 3. 1 Notes: Defined by chip design, not subject to 100% production test at wafer level Performance will vary based on assembly technique and substrate choice Repetitive Rating: Pulse width limited by maximum junction temperature Further Information - Contact your Micross sales office or email your enquiry to baredie@micross.com ©2014 Fairchild Semiconductor Corporation & Micross Components Page1 Static Characteristics, TJ = 25° unless otherwise noted Dynamic Characteristics4, TJ = 25°C unless otherwise noted Symbol Parameter Test Conditions Min Typ Max Units gFS Forward Transconductance VDS = 20V, ID = 10A - 20 - S ESR Equivalent Series Resistance (G-S) f = 1Mhz - 5 - Ω Ciss Input Capacitance - 2385 3175 pF VDS =25V, VGS = 0V f = 1MHz - 1795 2396 pF - 110 165 pF Coss Output Capacitance Crss Reverse Transfer Capacitance Coss Output Capacitance VDS =380V, VGS = 0V f = 1MHz - 42 - pF Effective Output Capacitance VDS =0V to 480V, VGS = 0V - 178 - pF - 63 82 nC - 10 - nC - 24 - nC Coss. eff. Qg(tot) Total Gate Charge at 10V Qgs Gate to Source Gate Charge Qgd Gate to Drain “Miller” Charge VDS =380V, ID = 10A 5 VGS = 10V Switching Characteristics4, TJ = 25°C unless otherwise noted Symbol Parameter td(on) Turn-On Delay Time tr Turn-On Rise Time td(off) Turn-Off Delay Time tf Turn-Off Fall Time Test Conditions VDD = 380V, ID = 10A 5 VGS = 10V RGEN = 4.7Ω Min Typ Max Units - 23 56 ns - 14 38 ns - 101 212 ns - 15 40 Ns Min Typ Max Units Drain-Source Diode Characteristics4, TJ = 25°C unless otherwise noted Symbol Parameter Test Conditions IS Maximum Continuous Drain to Source Diode Forward Current - - 20.2 A ISM Maximum Pulsed Drain to Source Diode Forward Current - - 60.6 A VSD Drain to Source Diode Forward Voltage VGS = 0V, ISD = 10A - - 1.2 V trr Reverse Recovery Time - 308 - ns Qrr Reverse Recovery Charge VGS = 0V, ISD = 10A dIF/dt = 100A/μs - 4.8 - µC 4. 5. Notes: Characterised by design & tested at component level, not subject to production test at wafer level Essentially independent of Operating Temperature Typical Characteristics Part Number Format Detail / Drawing FCP190N60EMW Un-sawn wafer, electrical rejects inked Page 3 FCP190N60EMF Sawn wafer on film-frame Page 4 FCP190N60EMD Singulated die / chips in waffle pack Page 4 Note: Singulated Die / Chips can also be supplied in Pocket Tape or SurfTape® on request Further Information - Contact your Micross sales office or email your enquiry to baredie@micross.com ©2014 Fairchild Semiconductor Corporation & Micross Components Page2 Ordering Guide Die Drawing Mechanical Data Parameter Units Chip Dimensions Un-sawn 5280 x 3530 µm Chip Thickness (Nominal) 300 µm Gate Pad Size 360 x 470 µm Wafer Diameter 150 (subject to change) mm Saw Street 80 (subject to change) µm Wafer orientation on frame Wafer notch parallel with frame flat Topside Metallisation & Thickness Al 4 µm Backside Metallisation & Thickness V/Ni/Ag 0.3 µm Silicon Nitride Recommended Die Attach Material Soft Solder or Conductive Epoxy Recommended Wire Bond - Gate Al 125µm X1 Recommended Wire Bond – Source Al 380µm X2 Page3 Topside Passivation Further Information - Contact your Micross sales office or email your enquiry to baredie@micross.com ©2014 Fairchild Semiconductor Corporation & Micross Components Sawn Wafer on Film-Frame – Dimensions (inches) Die in Waffle Pack – Dimensions (mm) A X X = 3.81mm ±0.13mm pocket size Y = 6.32mm ±0.13mm pocket size Z = 0.61mm ±0.08mm pocket depth A = 5° ±1/2° pocket draft angle No Cross Slots Array = 7 X 5 (35) Y Z X OVERALL TRAY SIZE Size = 50.67mm ±0.25mm Height = 3.94mm ±0.13mm Flatness = 0.30mm DISCLAIMER THE INFORMATION HEREIN IS GIVEN TO DESCRIBE CERTAIN COMPONENTS AND SHALL NOT BE CONSIDERED AS WARRANTED CHARACTERISTICS. NO RESPONSIBILITY IS ASSUMED FOR ITS USE; NOR FOR ANY INFRINGEMENT OF PATENTS OR OTHER RIGHTS OF THIRD PARTIES WHICH MAY RESULT FROM ITS USE. NO LICENSE IS GRANTED BY IMPLICATION OR OTHERWISE UNDER ANY PATENT OR PATENT RIGHTS OF EITHER MICROSS COMPONENTS OR FAIRCHILD SEMICONDUCTOR CORPORATION. FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS. LIFE SUPPORT POLICY FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used here in: (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labelling, can be reasonably expected to result in a significant injury of the user. 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. Further Information - Contact your Micross sales office or email your enquiry to baredie@micross.com ©2014 Fairchild Semiconductor Corporation & Micross Components Page4 1. Life support devices or systems are devices or systems which,