Supertex inc.

MD3872DB1

MD3872 Front-End Ultrasound Receiver Demoboard

Introduction

The MD3872 is a low power and low noise eight-channel

front-end receiver for medical ultrasound imaging. Its excellent low power dynamic performance is especially suitable

for portable ultrasound applications. Each channel’s circuit is

composed of a 14dB/18dB low noise pre-amplifier (LNA), a

voltage-controlled attenuator (VCA or TGC), a programmable gain amplifier (PGA), an anti-aliasing filter (AAF) and an

analog-to-digital (ADC) converter. The gain and gain range

of the VGA can be digitally configured separately. The gain

of the PGA can be set to one of four discrete values: 23.5dB,

29dB, 34.5dB or 40dB. The VCA can be continuously varied

by a control voltage from -47dB to a maximum of 0dB.

In CW mode, an integrated trans-conductance amplifier is

driven by the LNA to generate differential output current.

The resulting signal currents of each channel then connect

to an 8×8 differential cross-point switch which can be programmed through the SPI. The 12-bit ADC is based on a

pipeline structure to provide high static linearity. The data,

clock, and frame alignment signal outputs are serial LVDS in

binary format for each channel.

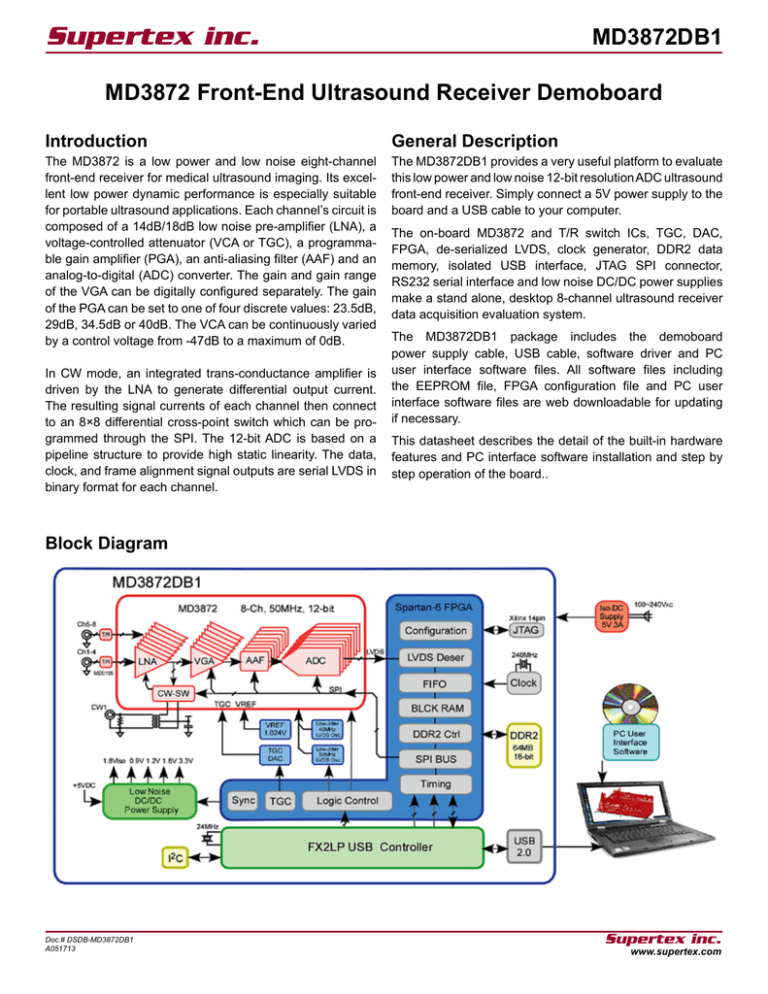

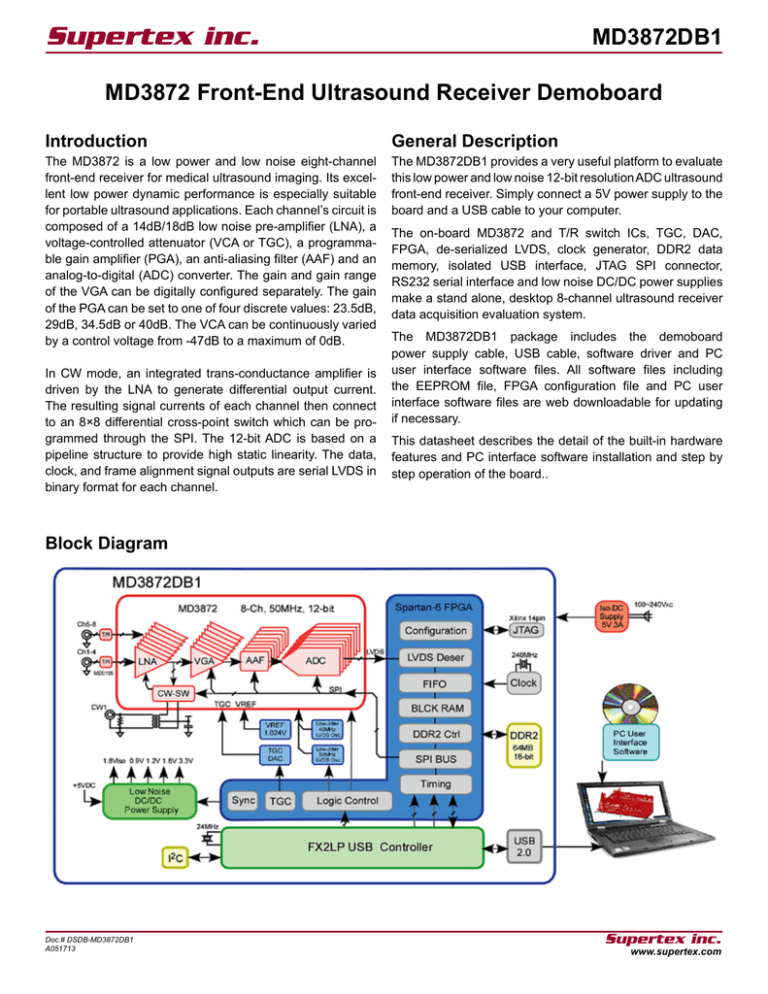

General Description

The MD3872DB1 provides a very useful platform to evaluate

this low power and low noise 12-bit resolution ADC ultrasound

front-end receiver. Simply connect a 5V power supply to the

board and a USB cable to your computer.

The on-board MD3872 and T/R switch ICs, TGC, DAC,

FPGA, de-serialized LVDS, clock generator, DDR2 data

memory, isolated USB interface, JTAG SPI connector,

RS232 serial interface and low noise DC/DC power supplies

make a stand alone, desktop 8-channel ultrasound receiver

data acquisition evaluation system.

The MD3872DB1 package includes the demoboard

power supply cable, USB cable, software driver and PC

user interface software files. All software files including

the EEPROM file, FPGA configuration file and PC user

interface software files are web downloadable for updating

if necessary.

This datasheet describes the detail of the built-in hardware

features and PC interface software installation and step by

step operation of the board..

Block Diagram

Doc.# DSDB-MD3872DB1

A051713

Supertex inc.

www.supertex.com

MD3872DB1

MD3872DB1 Hardware Design

Users should leave the EBC pin disconnected. It is for

manufacturer testing only. The AVDD pins are connected to

a low noise +1.8V isolated power supply. The AVDD supply

pins need to be thoroughly decoupled to make sure that LNA

is working a low EMI/RFI conditions.

The eight channels of MD3872 LNA inputs are connected

to eight input signal SMA connectors via a transmit/receive

switch circuit, TRSW, as shown below. The T/R switches

used here are two Supertex MD0105s, 4-channel, ±130V,

15Ω devices. They are two-terminal devices. A pair of backto-back diodes, D24, are present to protect the LNA input

circuit from high-voltage transmission pulses and voltage

spikes from the transducer and long cable lines. The T/R

switch provides a low on-resistance (normal ON state) at

receiving time and a high impedance (OFF state) when high

voltage pulses are present. These input circuits enable the

user to directly evaluate their echo signal processing using

the MD3872 front-end receiver in their ultrasound system.

All digital outputs, especially the eight channels of LVDS,

working at 480bit/s data speed consumes a large amount of

power. One can slightly increase the DVDD voltage by +1.90

to 1.95V for better LVDS output waveforms at 300MHz DCLK

when 50MSPS maximum sampling rate becomes necessary.

The DVDD power rail is supplied by a separate LDO U11.

These AVDD and DVDD regulators feedback sense pins are

directly connected to the ferrite bead down stream and the

corresponding power supply pins separately. This method

will provide accurate voltage and lower noise.

The trans impedance LNA gain setting of resistor Rf1 (R125)

is 249Ω when LNA SW is OFF. Because the Rf2 (R124)

is 590Ω, that means when LNA SW is ON, the effective

resistance is Rf1//Rf2 = 175Ω. See the MD3872 datasheet

for the LNA input impedance calculation and LNA SW SPI

control bits.

The MD3872 +3.3V CVDD it connected to a CW cross point

switch circuit. Foe those applications that do not need CW

signals, one can simply connect the CVDD to 1.8 as well.

PCB Board Design

The MD3872 sampling clock input signals are 40 or 50MHz

from two low-jitter LVDS crystal oscillators, via a shared

differential-clock bus, which is terminated with a 100Ω

differential load resistor. The bus lines must be comprised

of two closely coupled, length-matched, 50Ω impedances to

ground. The 100Ω resistor load must be placed very close to

the MD3872 CLK± pins.

In order to simplify testing of the CW cross-point switch

current source outputs, one channel CW1± pins have been

connected to a tightly coupled, center-taped, wind-band RF

transformer T2 and to an SMA connector J21.

There is an SPI serially interfaced 12-bit precision DAC on

board for quick evaluation of the TGC function of MD3872.

It can generate 0 to 1.8V with 0.44mV step resolution. R45

and R34 form a simple DAC output voltage-divider file that

scales the TGC signal. The Gain-Scaling Control pin GSC

has been pulled up to 1.8V AVDD by R30, which means that

GSC is set to 50dB/V TGC gain on this demoboard. One

can easily install a proper value on the resistor R36 (open as

default) to reset the TGC gain. Note that the VGSC minimum

voltage is 1.44V, which sets the TGC gain to about 66dB/V.

Besides the clock input pins, all the other pairs of LVDS

output pins to FPGA de-serialized input pairs also need to

be the same type of transmission lines that are designed

on the PCB. The termination resistors, however, are not

needed due to the built-in LVDS termination feature of the

Spartan-6 FPGA circuit. But length-matching of the LVDS

lines is very critical to the ADC output data pairs OUTn± vs.

DCLK± and FCLK± pairs. Precision trace line impedancecontrol by a PCB fabrication house is highly recommended,

although MD3872 has built-in programmable LVDS output

skew alignment features.

Although there is a built-in ADC reference voltage source

in MD3872, for evaluating the external referencing option,

there is an additional on-board precision 1.024V reference

device, U9, which can work with the jumper J24 to select the

internal or external reference. When selecting the external

reference, the EXT jumper should be Hi.

The most important thing about the PCB design for the

MD3872 receiver front-end IC, besides the line impedance

control, is the ground plane selection and ground integrity.

Supertex recommends that if MD3872 is on the top layer

of the PCB stack, then the ground must be the second

layer. The center-bottom of the IC’s thermal pad should be

well connected to the ground plane electrically as well as

thermally. The vias on the thermal pads should use about

a 0.3mm diameter drill for the through hole matrices with

1.0mm pitch. However, do not let the pad electrically connect to the other layers of the PCB stack, even if they are

named as GND , but thermally it can connect to as many

The MD3872 reference pins’ top and bottom voltages of

the ADC are not only for testing the voltages, but also for

bypassing capacitors differentially (C135 & C146) as well

as common-mode to ground (C153 & C154). When the IC

is working at 40 or 50MSPS speeds, all eight channels of

the ADl need a very large peak current into or out of the

reference voltage pins. It is important to keep the ADC

reference filtered as the current ripples especially in the

differential mode.

Doc.# DSDB-MD3872DB1

A051713

2

Supertex inc.

www.supertex.com

MD3872DB1

layers as possible to lower the thermal resistance of heat

sinking. The GND vias of all the decoupling capacitors of the

MD3872’s power supply pin should also connect to the second layer with traces that are as short as possible, or even

without a trace. The GND plane should not have a split, longslot or large-hole. Make sure the top signal’s return currents

to ground freely select the best path, just like the top signal

path’s shadow-image is projected on to the GND plane for

minimizing its magnetic loop and therefore minimizing ERI/

RFI. PCB layout designers must make sure that no return

current paths are close to, crossing, or overlapping each

other on the ground plane. The power traces are normally

selected on the third layer for the power trace impedance

and de-coupling.

After correct configuration of the FPGA, a user interface window comes up, as shown in Fig. 2:

USB Driver Installation

Fig. 2

The MD3872DB1 demoboard uses Spartan-6 FPGA as the

MD3782 LVDS de-serializer and data acquisition controller

interfaced to DDR memory and the USB controller. The USB

port on the CY7C68913A via is a 20Mbit/s USB isolator connected to a PC USB port. To install the USB driver, plug the

USB cable into the PC, turn on the demoboard power supply, then install the driver by clicking the new USB device

and selecting the SupertexWinUsb.inf file which is provided

in the Supertex subdirectory of the demo software. After

installing the driver, you will see a new item under Control

Panel / Device Manager called “SupertexUsb / USB SAMPLE”. Click the “Supertex.exe” file to start running the demo

software.

To acquire one of the 8-channels of MD3872 data, select

the “File/Acquire Data”. Select the desired “Sample Period”,

“Sample Point” and “Sample Channel” from the three options provided, then click the “Start button”.

Demoboard Software

Running the Supertex.exe file will automatically download the

FPGA “SuperTexFPGA.bin” file into the Spartan-6 FPGA first.

This procedure takes about 20 seconds. See figure below:

Fig. 3

A new time domain waveform window will come up, If the

input is a Sine wave, then the screen looks like this:

Fig. 1

Before running “SuperTex.exe”, some Windows XP or 7 users may need to install the “.net runtime library”. It can be

found in the “Driver” subdirectory in the “SuperTex” folder as

“dotNetfx.exe”.

Doc.# DSDB-MD3872DB1

A051713

Fig. 4

3

Supertex inc.

www.supertex.com

MD3872DB1

Controlling the TGC DAC

To zoom in/out on the time or amplitude axis, use (Ctrl + /

-) or (Ctrl ] / [). Or use the “Horizontal Zoom” and “Vertical

Zoom” pull-down menus.

To control the TGC voltage which outputs from the SPI serial

interfaced DAC, select “File / TGC DAC Write” at the top level

screen of the demo software window,then use the default

Address Input value 3 and type any number within 000 to

FFF in Hex. That corresponds to abut 0 to 1.8V in voltage

at the TGC pin of MD3872, and corresponds to -47dB to

0dB for the TGC attenuations. The TGC linear-in-Log control

curve from 0 to 1.7V is shown below.

The frequency domain and harmonic analysis are available

by clicking the “Fourier Transform” Tab above the waveform

window. If an RF frequency peak top is not located at 0 dB

or where you want it be as the reference point, you could

simply use (Ctrl > / <) to offset the FFT results.

To save a data file of an acquisition resolution use “File/

Save As (*.spd) file for later review, or “Save to CSV” file for

Excel data base or MATLAB or MathCAD evaluation.

Fig. 5

Fig. 7

Configuring the MD3872 SIP Register

Using the demoboard software, you can easily configure the

MD3872 SPI register, by selecting the “MD3872 Cfg” menu.

The configuration window looks like this:

0

TGC Attenuation (dB)

Maximum Slope

Minimum Slope

-47

0

TGC Voltage (V)

1.7

Fig. 6

Fig. 8

On the left side, a table of MD3872 SPI registers is shown in

binary. The ADDR column is in Hex 0 to F. The register data

field help table is on the right side. The help contents will progressively change as the selected ADDR row is changing.

After you enter the wanted number to the page, select the

“Save / to Hardware” or “Save / to (*.md) file for later recall.

That means setting the TGC DAC to more than 0xF1C will

make all the channels have attenuation of about 0dB.

Doc.# DSDB-MD3872DB1

A051713

4

Supertex inc.

www.supertex.com

MD3872DB1

Low Power MD3872 Runs Cool

The low power dissipation feature of the MD3872 is superior to its competition. To the right is a IR thermal image of

the chip on the demoboard. It shows about 52°C at the surface when 8-channels are running at 40MHz, with AVDD =

+1.80V, DVDD = +1.97V CVDD = +3.3V. The emissivity of

the package is about 0.95. This demoboard PCB stack is

8-layers and uses 0.5oz copper thickness

Demoboard Circuit Schematic

2

AVDD1V8

AVDD1V8

C63 C64 C65 C66

1.0 1n 1.0 1n

2

J13

COM

TRSW4

U21-1

R196

0

R197

2K

1

2

19

NCA NCB

A

B

GND

XDRC

18

17

COM

TRSW8

XDRC

MD0105K6

J15

COM

U21-2

R181

0

R182

2K

3

4

20

NCA NCB

A

B

GND

TRSW5

16

15

XDRC

COM

TRSW6

MD0105K6

J17

XDRC

COM

U21-3

R186

0

R187

2K

5

6

21

NCA NCB

A

B

GND

SMA

MD_TGC

U21-4

R191

0

R192

2K

XDRC

AVDD1V8

MD0105K6

J19

TRSW7

14

13

7

8

22

NCA NCB

A

B

GND

R34

750

12

11

R31

50

COM

50

SMA

1

2

5

3

6

6

VDD

3

61

60

MD_OUTP1

MD_OUTN1

EN

2

NC

PASW

PALNA+

LNA-

86

85

84

82

SW3

PA3IN3+

IN3-

OUT3+

OUT3-

53

52

MD_OUTP2

MD_OUTN2

OSC_FRE1

PASW

PALNA+

LNA-

93

92

91

89

SW4

PA4IN4+

IN4-

OUT4+

OUT4-

51

50

MD_OUTP3

MD_OUTN3

PASW

PALNA+

LNA-

4

5

6

8

SW5

PA5IN5+

IN5-

OUT5+

OUT5-

45

44

MD_OUTP4

MD_OUTN4

PASW

PALNA+

LNA-

11

12

13

15

SW6

PA6IN6+

IN6-

PASW

PALNA+

LNA-

18

19

20

22

PASW

PALNA+

LNA-

U7

MD3872

OUT6+

OUT6-

43

42

MD_OUTP5

MD_OUTN5

SW7

PA7IN7+

IN7-

OUT7+

OUT7-

41

40

MD_OUTP6

MD_OUTN6

25

26

27

29

SW8

PA8IN8+

IN8-

OUT8+

OUT8-

39

38

MD_OUTP7

MD_OUTN7

126

125

GSC

TGC

100

101

102

103

104

105

106

107

116

117

118

119

120

121

122

123

CW1+

CW1CW2+

CW2CW3+

CW3CW4+

CW4CW5+

CW5CW6+

CW6CW7+

CW7CW8+

CW8-

SDI

SDO

SCLK

CSB

64

34

63

65

FLEX

EXT

EBC

98

110

128

NC

NC

NC

NC

ADC CLK 40MHz

6

X2

VDD

108

115

CVDD

CVDD

55

54

1

OUT2+

OUT2-

C132

T2

MCL_T1-6T

4

PDWN

STBY

SW2

PA2IN2+

IN2-

CVDD3V3

CWD1

114

33

36

62

99

37

58

79

78

77

75

TP20

J21

AVDD3

AVDD4

AVDD5

AVDD6

AVDD7

DVDD

DVDD

PASW

PALNA+

LNA-

C131

0.01

0.01

2

9

16

23

95

88

81

74

MD_OUTP0

MD_OUTN0

INF R36

MD0105K6

AVDD2

AVDD2

AVDD2

AVDD2

AVDD2

AVDD2

AVDD2

AVDD2

57

56

R30

TP19

VDD3V3

C111

10n

FOX-LC735R-40

5

LVDS_CLKN

OUT1

4

LVDS_CLKP

3

OUT2

CVDD3V3

C157 C158

1.0

1n

R44

1K

External VREF

U9

LM4140

VIN

XDRC

LVDS_CLKP

R47

0

3

EN

5

NC

VREF

GND

GND

GND

GND

TRSW3

MD0105K6

LVDS_CLKN

4

6

VREF1V024

C161

1.0

1

4

7

8

COM

5

OUT1

66

59

35

67

MD_SDI

MD_SDO

MD_SCLK

MD_CSB

MD_EXT

R39

INF

CVDD3V3

C155 C156

1.0 1n

MD_FLEX

TGC DAC

DVDD1V8

R37

1K

4

12

11

OUT2

1

2

3

J24

HEAD3

R45

249

6

MD_TGC

DAC Output 0 to 2.5V

VOUT

U8

LTC2630-LM12-LCZB

SDI

3

TGC_SDI

SCK

2

TGC_SCK

CS-LD

1

TGC_CS_LD

5

NCA NCB

B

A

GND

MD_FCLKP

MD_FCLKN

RBIAS

R177

2K

7

8

22

MD_DCLKP

MD_DCLKN

47

46

OUT1+

OUT1-

REF+

0

FOX-LC735R-30

CW1+

C144

1.0

0.1 0.1 0.1 0.1 0.1

0.1 0.1 0.1 0.1

CW1C159

R43

INF

C139C140C141C142C143

C149C150C151C152

0.1

C135

0.1

109

XDRC

U20-4

R176

49

48

FCLK+

FCLK-

SW1

PA1IN1+

IN1-

113

TRSW2

DCLK+

DCLK-

72

71

70

68

REF-

MD0105K6

NC

PASW

PALNA+

LNA-

VREF

COM

112

XDRC

3

10

17

24

94

87

80

73

124

TRSW1

CLK+

CLK-

111

NCA NCB

A

B

GND

32

31

GND

GND

GND

GND

GND

R172

2K

14

13

1

30

129

96

97

0

5

6

21

EN

2

OSC_FRE2

AVDD1

AVDD1

AVDD1

AVDD1

AVDD1

AVDD1

AVDD1

AVDD1

LVDS_CLKP

LVDS_CLKN

1

MD_STBY

AVDD0

100 R28

MD0105K6

ADC CLK 50MHz

X1

MD_PDWN

C127 C128

1.0 1n

16

15

U20-3

R171

C124

1n

CM0

CM1

CM2

CM3

CM4

CM5

CM6

CM7

CM8

R167

2K

C123

1.0

127

69

76

83

90

7

14

21

28

0

NCA NCB

A

B

GND

+

VDD3V3

GND

MD0105K6

3

4

20

C116 C117 C118

1n

1.0

1n

C125 C126

1.0 1n

FB15

U20-2

R166

C26

10n

470uF 6.3V

C119

GND

AVDD1V8

18

17

2

NCA NCB

A

B

GND

1

R127

2K

1

2

19

C120

1.0

AVDD3

U20-1

R126

0

J11

FB12

VCC

+

1

C94

C95 C96 C97 C98 C99 C100C101C102C103C104C105C106C107C108C109C110

1.0 1n 1.0 1n 1.0 1n 1.0 1n 1.0 1n 1.0 1n 1.0 1n 1.0 1n

2

2

470uF 6.3V

J7

CVDD3V3

1

Rx Inputs

J6

C71 C72

1.0 1n

C69 C70

1.0 1n

AVDD1

FB10

GND

AVDD1V8

J5

1

1

+

C46

FB3

C28 C29

1.0 1n

C47 C48 C49 C50 C51 C52 C53 C54 C55 C56 C57 C58 C59 C60 C61 C62

1.0 1n 1.0 1n 1.0 1n 1.0 1n 1.0 1n 1.0 1n 1.0 1n 1.0 1n

DVDD1

2

1

2

FB4

470uF 6.3V

DVDD1V8

FB1

AVDD2

C145

C146

R41

4.7

49.9K

0.1 C153

C154

0.1

0.1

VREF1V024

R179

590

TRSW

PASW

R180

249

PAC364

C365

18nF

LNA+

2

1

XDRC

R183 D35

BAS40-04

2K

0.01

C367

C366

22pF

Doc.# DSDB-MD3872DB1

A051713

3

LNACOM

5

0.01

Supertex inc.

www.supertex.com

MD3872DB1

MD3872DB1 Waveforms @ 40MHz Sampling Frequency

Fig. 10 Waveform screen of Ch-1, 1.0MHz Sine wave by HP33120A & Q56T-1M filter

Fig. 11 Fourier Transform screen of the above 1.0MHz Sine wave

Fig. 12 Harmonic Analysis screen of the above 1.0MHz Sin wave

Doc.# DSDB-MD3872DB1

A051713

6

Supertex inc.

www.supertex.com

MD3872DB1

MD3872DB1 Waveforms @ 40MHz Sampling Frequency

Fig. 13 Waveform screen of Ch-1, 5.0MHz Sine wave by HP33120A & Q56T-5M filter

Fig. 14 Fourier Transform screen of the above 5.0MHz Sine wave

Fig. 15 Harmonic Analysis screen of the above 5.0MHz Sine wave

Doc.# DSDB-MD3872DB1

A051713

7

Supertex inc.

www.supertex.com

MD3872DB1

MD3872DB1 Waveforms @ 40MHz Sampling Frequency

Fig. 16 Waveform screen of Ch-1, 7.0MHz Sine wave by HP33120A & LE1182T-7M filter

Fig. 17 Fourier Transform screen of the above 7.0MHz Sine wave

Fig. 18 Harmonic Analysis screen of the above 7.0MHz Sine wave

Doc.# DSDB-MD3872DB1

A051713

8

Supertex inc.

www.supertex.com

MD3872DB1

MD3872DB1 Waveforms @ 50MHz Sampling Frequency

Fig. 20 Fourier Transform screen of the above 5.0MHz Sine wave

Fig. 19 Waveform screen of Ch-1, 5.0MHz Sine wave by HP33120A & LE1182T-7M filter

Fig. 21 Harmonic Analysis screen of the above 5.0MHz Sine wave

Doc.# DSDB-MD3872DB1

A051713

9

Supertex inc.

www.supertex.com

MD3872DB1

MD3872DB1 Waveforms @ 50MHz Sampling Frequency

Fig. 23 Fourier Transform screen of the above 7.0MHz Sine wave

Fig. 22 Waveform screen of Ch-1, 7.0MHz Sine wave by HP33120A & LE1182T-7M filter

Fig. 24 Harmonic Analysis screen of the above 7.0MHz Sine wave

Doc.# DSDB-MD3872DB1

A051713

10

Supertex inc.

www.supertex.com

MD3872DB1

PCB Layout

PCB Board

Doc.# DSDB-MD3872DB1

A051713

11

Supertex inc.

www.supertex.com

MD3872DB1

Board Connector and Test Pin Description

Power Supply Connector, Switch and Test Point Description

J22

+5V 2A

DC power supply (*see important safety notice below!)

SW2

Power SW

DC power supply On/Off switch

SW1

RESET

USB controller resetting switch

SW3

Test SW

FPGA test switch

TP48,49,50,

51,53,57,61

GND

Ground test points

D2, D4, D5

Test LEDs

USB controller test LED Indicators Red,Green,Yellow

D2

USB LED

PC USB V+ LED, Green

D16

+5V LED

+5V DC+ power supply LED, Green

D25, D26

Test LEDs

Test LED, Red Yellow indicators for pin C6 & B3 of FPGA (XC6S16-2FTG256C)

TP65

+5Vin

TP64

+5V

TP30

+3.3V

VDD for USB controller

TP39

+3.3V

VCC to FPGA bank 0,2,3

+5V DC +power supply test point after SW2

+5V DC +power supply test point before SW2

*Note:

It is important to make sure that J22 plug negative (the outer connection of the power plug) is grounded (0V)!

Power Supply Connector, Switch and Test Point Description (cont.)

TP42

+3.3V

VCCAUX and JTAG SPI J3-5

TP43

+1.2V

VCCINT +1.2V

TP24

+0.9V

VTT +0.9V

TP23

+3.3V

CVDD +3.3V for CW and DAC

TP21

>+1.8V

AVDD +1.8V LDO output before FB4 & FB10.

TP25

+1.8V

VCC +1.8V for FPGA bank 1 & DDR2

JTAG Connector Pin Number, Signal Name and Description

J3-1

TMS

TMS pin of FPGA SPI JTAG interface

J3-2

TDI

TDI pin of FPGA SPI JTAG interface

J3-3

TDO

TDO pin of FPGA SPI JTAG interface

J3-4

TCK

TCK pin of FPGA SPI JTAG interface

J3-5

+3.3V

+3.3V (output) pin of FPGA SPI JTAG interface

J3-6

GND

GND pin of FPGA SPI JTAG interface

Analog I/O Test Signal Connector Description

J5

CH1 SMA

Ultrasound Rx input connectors for MD3872 CH1, with MD0105 T/R switches.

J6

CH2 SMA

Ultrasound Rx input connectors for MD3872 CH2, with MD0105 T/R switches.

J7

CH3 SMA

Ultrasound Rx input connectors for MD3872 CH3, with MD0105 T/R switches.

J11

CH4 SMA

Ultrasound Rx input connectors for MD3872 CH4, with MD0105 T/R switches.

J13

CH5 SMA

Ultrasound Rx input connectors for MD3872 CH5, with MD0105 T/R switches.

J15

CH6 SMA

Ultrasound Rx input connectors for MD3872 CH6, with MD0105 T/R switches.

J17

CH7 SMA

Ultrasound Rx input connectors for MD3872 CH7, with MD0105 T/R switches.

J19

CH8 SMA

Ultrasound Rx input connectors for MD3872 CH8, with MD0105 T/R switches.

Doc.# DSDB-MD3872DB1

A051713

12

Supertex inc.

www.supertex.com

MD3872DB1

Analog I/O Test Signal Connector Description (cont.)

J21

SMA

MD3872 CW cross-point switches output CW1+ and CW1- via 1:1 RF transformer.

TP19

TGC

MD3872 TGC pin, 0 to+1.8V(max) controlled by 12bit SPI DAC U8 on board.

TP20

GSC

MD3872 GSC pin, 50Ω pull up to AVDD +1.8V

J24

EXT

MD3872 EXT pin connection selecting jumper, default on pin2-3 (EXT=0)

USB and RS232 Interface to PC Computer

J1

USB

J2

RS232

Electrically Isolated 20Mbit/s full speed USB interface to computer

Serial interface of USB controller for debugging only

Demoboard Key Components List

Reference

U7

Description

Manufacturers Part No.

Manufacturer

MD3872 8Ch 50MHz ultrasound receiver front-end IC MD3872HF-G

Supertex Inc.

MD0105K6 4-ch ultrasound ±130V T/R switch

MD0105K6-G

Supertex Inc.

U1

IC MCU USB periph HI SPD 128-lead LQFP

CY7C68013A-128AXC

Cypress

U2

Spartan-6 FPGA

XC6SLX16-2FTG256C

Xilinx

U3

IC filter USB ESD protect SOT363

NUF2221W1T2G

On Semi

U4

IC TXRX 3.3V EIA/TIA-562 16-SOIC

LTC1386CS#PBF

Linear

U5

8-pin low profile IC socket .300

115-93-308-41-003000

Mill-Max

U8

IC DAC 12BIT 2.5V R-R SC70-6 (Mark, LCSB)

LTC2630ISC6-LZ12#TRMPBF Linear Tech

U9

IC ref prec volt micropwr 8-Lead SOIC

LM4140ACM-1.0/NOPB

National

LT1764AEQ-1.8#PBF

Linear Tech

U20,U21

U10,U11,U14 IC LDO LO noise 3A 1.8V 5-Lead D-PAK

U12

IC REG LDO 1.5A 3.3V SOT-223

ADP3339AKCZ-3.3-RL

ADI

U15

IC DDR2 SDRAM 1GBIT 3NS 84FBGA

EDE1116ACBG_8E_E

Supertex

U16

IC push-pull cntrlr sync 16-lead TSSOP

LT3439EFE#PBF

Linear Tech

U18,U19

IC DC/DC Umodule 6A 133-Lead LGA

LTM4606EV#PBF

Linear Tech

U36

IC REG LDO adj 1.1A 5-Lead D-PAK

LT3080EQ#PBF

Linear Tech

U37

IC USB isolator Full/Low 16-Lead SOIC

ADUM4160BRWZ

ADI

IC BUS transcvr 4BIT 16-lead TSSOP

SN74AVC4T245PWR

TI

U41,U42

U5

IC EEPROM 128KBIT 400KHz 8-Lead DIP, On Socket 24LC128-I/P

Microchip

T1

RF transformer 0.015 to 3.00MHz

T1-6T-KK81

Mini-Circuits

T3

DC/DC 1:1 switching power supply transformer

WE-750341004

Wűrth Electronics

X1

OSC 50 MHz 3.3V LVDS SMD

FXO-LC735R-50

FOX Electronics

X2

OSC 40 MHz 3.3V LVDS SMD

FXO-LC735R-40

FOX Electronics

X3

OSC 240 MHz 3.3V LVDS SMD

FXO-LC735R-240

FOX Electronics

Y1

Crystal 24.00 MHz 12PF SMD

ECS-240-12-28A-TR

ECS Inc.

Supertex inc. does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives

an adequate “product liability indemnification insurance agreement.” Supertex inc. does not assume responsibility for use of devices described, and limits its liability

to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and

specifications are subject to change without notice. For the latest product specifications refer to the Supertex inc. (website: http//www.supertex.com)

Supertex inc.

©2013 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited.

Doc.# DSDB-MD3872DB1

A051713

13

1235 Bordeaux Drive, Sunnyvale, CA 94089

Tel: 408-222-8888

www.supertex.com

Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Supertex:

MD3872DB1