Experiments in Analog Electronics

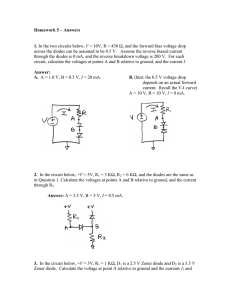

advertisement