Embedded Scan Test with Diagnostic Features for Self

advertisement

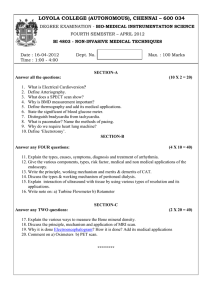

Embedded Scan Test with Diagnostic Features for Self-Testing SoCs C. Galke, R. Kothe, S. Schultke, K. Winkler, J. Honko, H. T. Vierhaus Brandenburg University of Technology Cottbus Computer Engineering Group Abstract Main stream scan test technology development has focused on a cost-efficient usage of external testers in conjunction with minimized on-chip pattern generators. Alternatively, an on-chip test processor that works with highly compacted test patterns from a ROM device allows a software-based self test procedure in the field of application, e.g. during startup tests. Furthermore, such an approach may facilitate self repair function, if the faulty logic block or gate can be identified. We present first investigations on an ”embedded” scan-based fault diagnosis, efforts and limitations. 1 The concept of embedded scan test For the conventional scheme of scan test the flip flops on the IC under test are structured into multiple parallel scan chains that are fed in parallel from a scan controller device [1]. This device produces the actual test vectors in a “test by scan” approach. Test vectors have been generated and compressed in an off-line pre-process. Also the compacted test response information is sent back to the tester. In an alternative approach, the scan controller is replaced by a BIST controller, leaving only activities such as a “start test” and “read results” for the external tester device. This goes at the expense of a higher scan controller complexity. The “embedded” scan test is an alternative that shifts the self-test control functions to software. The system is now supplemented by an additional processor device, which can do the overall test control and additional step of pattern de-compaction based on standard algorithm (e.g. Huffman, Zip). Compacted pattern information has to come from a ROM or PROM device, if the “embedded” test is performed independently from a tester device as i.e. as a field test. The test processor also has to do the final test evaluation, based on compacted test responses. The scheme can be designed to work with or without an external tester device. If, under control from an external tester during fabrication test, the test processor Proceedings of the 12th IEEE International On-Line Testing Symposium (IOLTS'06) 0-7695-2620-9/06 $20.00 © 2006 IEEE is relieved from “overall test control”, it can be used to de-compress test patterns. We investigated on methods that enhance embedded scan tests to gain diagnostic features. Recently published work [2,3] has shown significant progress in making scanbased test architectures that work on compressed test information and pattern response compaction by XOR-chains and MISRs useful for fault diagnosis. If we can thereby diagnose a failing pattern and the faulty bit position of the parallel scan paths feeding a MISR, the further diagnostic resolution needs to find out e.g. which functional block or even which gate has caused the fault. 2 Diagnostic Test We have started first in investigations on feasible extensions of existing scan test technologies towards diagnostic features. The total circuit consists of several functional blocks, such as, for example, the control logic, the data path and the input /output block in a processor design. A specific scan path cell can be fed by a cone of logic gates that belong to a specific unit. But in practice, there are logic elements in the control logic functional unit (FU) (Figure 1: FU2 ) that are observable only by logic paths running either through the data path or the I /O block. One known solution to the problem [4] is the separation of FUs under test by specific separation cells (Figure 1: left side). This test partitioning approach requires one extra separation gate per path and an additional global control signal. Furthermore, every such path now needs an extra scan cell. In total, this scheme is expensive, particularly if the FUs are strongly correlated. Therefore we developed a second scheme, which makes use of a feature implemented already. In real-life circuits, certain bit positions of the scan path will receive non-deterministic logic values. Since a MISR–based pattern compaction scheme can’t handle “uncertain” logic values, those bit positions must be replaced by “fixed” values. The architecture (Figure 1: right side) can overcome such problems. Then we tried to apply a blocking and deterministic setting of all those scan elements that receive inputs from several functional units. If we can now identify a specific faulty bit position of the scan chain, then it is also possible to associate it with a specific functional unit. MISR Sc an -o u t S ca n-ou t in set o ut & Scanout in FU 1 set & Scanout out FU 1 S e x tra sc a n c e lls FU 2 set bits FU 2 S FU 3 FU 3 S ca nin S c anin Scanin Scanin Figure 1: Test partitioning by hardware (l) or logic (r) segmentation 3 Efforts and Results For the diagnosis investigations we used a 16-bit RISC processor design as a benchmark in order to identify the overhead and the limitations of the fault diagnosis concept. The processor has a single scan path. The diagnosis aims at diagnosing a fault in the control logic, in the data path or in the I/O block. Patterns for stuck-at tests were generated using a commercial ATPG tool. Table 1. Fault Diagnosis and Overhead Scan cells Total gates # Test patterns Clock cycles Fault coverage Diagnosis Scan test bytes Standard Scan test 530 21648 632 335491 99.28% 41870 Hardware Segment. 612 22468 454 278461 99.28% 100% 34731 Logic Segment. 530 21648 632 335491 99.28% 40% 41870 The diagnosis scheme based on hardware segmentation ends up with an overhead of about 5% in the total gate count, but requires about 20% more scan cells. On the other hand, the number of test clock cycles is reduced by about 20%. The diagnostic resolution is 100%. This means, we can now associate a specific faulty bit on a scan chain with either the control logic, the data path or the I/O unit. The uncompressed scan test data then require about 40 Kbytes of memory space. The results obtained by the blocking of specific outputs (logic segmentation) has a much lower diagnostic resolution capability. However, currently this scheme works with a standard set of test patterns. It may show much Proceedings of the 12th IEEE International On-Line Testing Symposium (IOLTS'06) 0-7695-2620-9/06 $20.00 © 2006 IEEE better results for specifically tuned test patterns where propagation of fault effects to outputs that can be associated with one FU is preferred. In general, the software overhead required for the “embedded” scan test is relatively low. So far, we have not implemented the “preceding” Step of fault diagnosis that identifies a specific scan chain and a specific bit position. However, to our best knowledge such schemes are less expensive in hardware than the selective bit blanking currently introduced in the scan controller design. We performed detailed simulations with respect to the overhead required for the whole embedded scan test scheme with diagnostic feature by hardware segmentation. The benefit of the scan controller scheme can only been shown by feeding more than one of the possible 16 multiple scan chains. Therefore we split the example processor device into 9 scan chains with length from 18 to 105 bits. The diagnostic scan test is required three times (3 FUs), because we use only one MISR for the response analysis. This result in 454682 bits of scan patterns. The scan controller requires about 104 thousand instructions to generate all scan test patterns and scan test control bits. With the optional 2nd compression process using Huffman-algorithm, which is done by the test processor, the overhead is limited to about 63 Kbytes. A reduction is possible by using the facility to feed all 16 scan chains of the scan controller configuration. The complexity of an example implementation of a canonic Huffman de-compaction algorithm for the test processor device is about 50 Kbytes. 4 Acknowledgements The work was partly supported by the German Research Foundation (DFG) within the HITSOC project (grant no. VI185/5-1). 5 References [1] C. Kretzschmar, C. Galke, H.T. Vierhaus; “A Hierarchical Self Test Scheme for SoCs”, Proc. 10th IEEE Int. On-Line Testing Symposium, 2004, pp. 37-42 [2] A. Leininger, M. Goessel, P. Muhmen-thaler, „Diagnosis of Scan-Chains by Use of a Configurable Signature Register and Error-Correcting Codes“, Proc. DATE 04, pp. 1302-1307 [3] M. Gössel, K. Chakrabarty, A. Leininger et al., „Identification of Failing Vectors using Signature Analysis with Application to Scan-BIST“, Journal of Electronic Testing (JETTA), 2004 [4] K. Chakrabarty, C. Liu, “A Partition-based Approach for Identifying Failing Scan Cells in ScanBIST with Application to System-on-Chip Fault Diagnosis”, Proc. DATE 03, pp. 230-235