August 2016 - Linear Technology

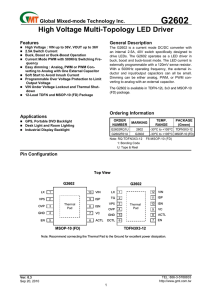

advertisement