Chapter 3 Lecture 5 The Digital Logic Level

advertisement

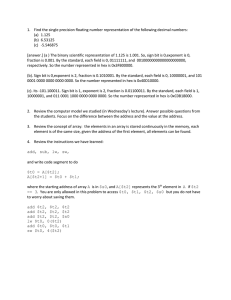

Chapter 3 Lecture 5 The Digital Logic Level Level 0: The basic building blocks and foundation of the computer: 3.1 Gates And Boolean Algebra 3.2 Basic Digital Logic Circuits 3.3 Memory 3.4 CPU Chips And Buses 3.5 Example CPU Chips 3.6 Example Buses 3.7 Interfacing Things to know Computer Design Approach Do not use glitch generators! Use super-synchronous digital design approaches. Use the Multiplexed-Register shown in class for your computer architecture designs. A Mux Din D B Q Q D-FF Sel QN QN Select Clock Please use this as “Bit Registers” in your computer designs Tri-state gates are required! Timing – work out all the details for homework problems!!!!! 1 of 14 ECE 357 Notes and figures are based on or taken from materials in the course textbook: A.S. Tanenbaum, Structured Computer Organization 4th ed., Prentice Hall, Upper Sable River, NJ, 1999. ISBN 0-13-095990-1. Communication “Bus” Architecture and Implementation Functions: Data and Addressing for memory Data and Addressing for sensors and peripheral devices Interrupt and Status Communications Special signals (command and control, reprogramming, monitoring, etc.) Implementations Parallel Asynchronous – full address, data, and control width Parallel Asynchronous – multiplexed address and/or data and control Parallel Synchronous – multi-clock cycle address, data, and control signals Serial Asynchronous - dedicated links or packet based bursts Serial Synchronous - structured packet based transfers Asynchronous parallel Bus Timing From CPU From Memory Asynchronous Read Cycle with hardware handshaking 2 of 14 ECE 357 Notes and figures are based on or taken from materials in the course textbook: A.S. Tanenbaum, Structured Computer Organization 4th ed., Prentice Hall, Upper Sable River, NJ, 1999. ISBN 0-13-095990-1. The PCI Bus The PCI bus is a synchronous bus with multiplexing of address and data on the AD lines. It includes a command and which byte boundaries to read or write on the C/BE#. FRAME defines a master commanded operation. IRDY indicates when the INITIATOR (bus master) is ready for data DEVSEL indicates when the TARGET (slave device) has decoded the address and is acknowledging it TRDY indicates when the TRAGET is ready for the commanded bus operation. See http://www.pcisig.com/home Figures from: PCI IP Core Specification, Authors: Miha Dolenc & Tadej Markovic, mihad@opencores.org, tadej@opencores.org, Rev. 0.5, October 20, 2001. 3 of 14 ECE 357 Notes and figures are based on or taken from materials in the course textbook: A.S. Tanenbaum, Structured Computer Organization 4th ed., Prentice Hall, Upper Sable River, NJ, 1999. ISBN 0-13-095990-1. The PCI Express (PCIe) Bus Parallel busses are challenged as the clock rates are pushed higher. Therefore, this interface is based on high-speed point-to-point serial communications! In PCIe, multiple “lanes” (x1, x2, x4, x8, x16 or x32) can be connected to the same board. Point-to-point connections using a switch. (Note: Ethernet switches Each lane uses low-voltage differential signaling (LVDS) and 4-wires for bidirectional communications (one pair TX, one pair RX). A reference clock is provided to synchronize bit transfers. Data is transferred in packets. a header (control info), sequence number and CRC with framing is used with each packet payload of data. Key features in PCIe as compared to PCI 1) Centralized switch for routing … see #2 2) Serial point-to-point connections 3) Packet based communications 4) Error-detection for increased reliability 5) Connection distances controlled but increased over bus-based systems 6) Expandable to multiple level of switching. 7) Hot pluggable: can be inserted or removed when the power is on. 4 of 14 ECE 357 Notes and figures are based on or taken from materials in the course textbook: A.S. Tanenbaum, Structured Computer Organization 4th ed., Prentice Hall, Upper Sable River, NJ, 1999. ISBN 0-13-095990-1. The packet structure from an OSI software layered protocol consideration is shown below. PCI Express protocol stack and packet formation A packet response is generated for each packet sent. (positive response messaging) Flow control. “Buffer size” is predetermined. Credits are computed to determine whether to continue. Additional credits are granted to continue transfers. For more information see the PCI-SIG (http://www.pcisig.com/home ) 5 of 14 ECE 357 Notes and figures are based on or taken from materials in the course textbook: A.S. Tanenbaum, Structured Computer Organization 4th ed., Prentice Hall, Upper Sable River, NJ, 1999. ISBN 0-13-095990-1. The Universal Serial Bus (USB) In 1993. seven companies got together to design a better way to connect low-speed I/O devices (mouse, keyboard, etc.) The companies were Compaq, DEC, IBM, Intel, Microsoft, NEC and Nortel. The goals: 1. Users must not have to set switches or jumpers on boards or devices. 2. Users must not have to open cases to install new I/O devices. 3. There should be only one kind of cable, good for interconnecting all devices. 4. I/O devices should get their power from the cable, 5. Up to 127 devices should be attachable to a single computer. 6. The system should support real-time devices (e.g. sound, telephone, game inputs) 7. The system should be installable while the computer is running. 8. No reboot should be needed after installing new devices 9. The new bus and its I/O should be inexpensive to manufacture. Architecture 4-wire interface: power, ground and 2 signal lines – bidirectional. Bit protocol: 0 is a voltage transition, 1 is no transition (embedded clock synchronization) Root hubs with direct-connects. A tree structure. Embodied as bit pipes from root hub to I/O devices. Data transmitted in frames, root hub broadcasts periodic synchronization. For more see: http://en.wikipedia.org/wiki/USB http://www.usb.org/home 6 of 14 ECE 357 Notes and figures are based on or taken from materials in the course textbook: A.S. Tanenbaum, Structured Computer Organization 4th ed., Prentice Hall, Upper Sable River, NJ, 1999. ISBN 0-13-095990-1. Memory Maps and Memory Planning Every computer has a defined memory map of locations. The following is from: Intel® Desktop Board DX58SO Technical Product Specification The board is designed to support the following processor: • Intel Core i7 Processor in an LGA1366 socket The board has four DIMM sockets and supports the following memory features: • 1.5 V DDR3 SDRAM DIMMs • Three independent memory channels with interleaved mode support • Unbuffered, single-sided or double-sided DIMMs with the following restriction: Doublesided DIMMs with x16 organization are not supported. • 16 GB maximum total system memory. Refer to Section 2.1.1 on page 39 for information on the total amount of addressable memory. 7 of 14 ECE 357 Notes and figures are based on or taken from materials in the course textbook: A.S. Tanenbaum, Structured Computer Organization 4th ed., Prentice Hall, Upper Sable River, NJ, 1999. ISBN 0-13-095990-1. 8 of 14 ECE 357 Notes and figures are based on or taken from materials in the course textbook: A.S. Tanenbaum, Structured Computer Organization 4th ed., Prentice Hall, Upper Sable River, NJ, 1999. ISBN 0-13-095990-1. 9 of 14 ECE 357 Notes and figures are based on or taken from materials in the course textbook: A.S. Tanenbaum, Structured Computer Organization 4th ed., Prentice Hall, Upper Sable River, NJ, 1999. ISBN 0-13-095990-1. HC12 Memory MAP Address Module Size (Bytes) $0000 - $03FF Register Space 1024 $0000 - $0FFF EEPROM (overlap) 4096 $1000 - $3FFF SRAM 12288 $4000 - $7FFF Fixed Flash 16384 $8000 - $BFFF Paged Window Flash 16384 $C000 - $FFFF Fixed Flash 16384 10 of 14 ECE 357 Notes and figures are based on or taken from materials in the course textbook: A.S. Tanenbaum, Structured Computer Organization 4th ed., Prentice Hall, Upper Sable River, NJ, 1999. ISBN 0-13-095990-1. Low Level Address Decoding Example Memory Map for a simple microcontroller A 16-bit address space (64 kBytes) EEPROM 2kBytes located at 0 hex – 2k for 11 bits Address: 0000 0000 0000 0000 to 0000 0111 1111 1111 (0000 hex to 07FF hex) RAM 2k Bytes located at 8000 hex – 2k for 11 bits Address: 1000 0000 0000 0000 to 1000 0111 1111 1111 (8000 hex to 87FF hex) Peripheral I/O 4 Bytes located at FFFC hex – 4 for 2 bits Address: 1111 1111 1111 1100 to 1111 1111 1111 1111 (FFFC hex to FFFF hex) Can you see the “logical” bits to use for unique “device select” addressing (hint: no color)? 11 of 14 ECE 357 Notes and figures are based on or taken from materials in the course textbook: A.S. Tanenbaum, Structured Computer Organization 4th ed., Prentice Hall, Upper Sable River, NJ, 1999. ISBN 0-13-095990-1. (1) Full Address Decoding to drive the “CHIP SELECTS”: Full Decoding of the Address Lines for Chip Selects EEPROM 2kBytes located at 0 hex Address: 0000 0000 0000 0000 to 0000 0111 1111 1111 (0000 hex to 07FF hex) RAM 2k Bytes located at 8000 hex Address: 1000 0000 0000 0000 to 1000 0111 1111 1111 (8000 hex to 87FF hex) Peripheral I/O 4 Bytes located at FFFC hex Address: 1111 1111 1111 1100 to 1111 1111 1111 1111 (FFFC hex to FFFF hex) 12 of 14 ECE 357 Notes and figures are based on or taken from materials in the course textbook: A.S. Tanenbaum, Structured Computer Organization 4th ed., Prentice Hall, Upper Sable River, NJ, 1999. ISBN 0-13-095990-1. (2) Partial Address Decoding to drive the “CHIP SELECTS”: Partial Decoding of the Address Lines for Chip Selects Only required to uniquely identify the memory/chip selects EEPROM 2kBytes located at 0 hex Address: 0000 0000 0000 0000 to 0000 0111 1111 1111 (0000 hex to 07FF hex) RAM 2k Bytes located at 8000 hex Address: 1000 0000 0000 0000 to 1000 0111 1111 1111 (8000 hex to 87FF hex) Peripheral I/O 4 Bytes located at FFFC hex Address: 1111 1111 1111 1100 to 1111 1111 1111 1111 (FFFC hex to FFFF hex) What would the new memory map be? Multiply defined regions available! 13 of 14 ECE 357 Notes and figures are based on or taken from materials in the course textbook: A.S. Tanenbaum, Structured Computer Organization 4th ed., Prentice Hall, Upper Sable River, NJ, 1999. ISBN 0-13-095990-1. Memory Mapping Memory Map based on full address bus decoding. Example Memory Map for a simple microcontroller Memory Map based on partial address bus decoding. EEPROM_CS = not(A(15)); The EEPROM responds for all addresses starting with (repeat on 2k blocks): 0000hex, 0800 hex, 1000 hex, 1800 hex, 2000, 2800, 3000, 3800, 4000, 4800, 500, 5800, 6000, 6800, 7000, 7800 RAM_CS = A(15) AND NOT(A(14)); The RAM responds for all addresses starting with (repeat on 2k blocks): 8000, 8800, 9000, 9800, A000, A800, B000, B800 PIO_CS = A(15) AND A(14) (repeat every 4 memory locations); The PIO responds for all address starting with: C000, C004, C008 …… lots of times!!!! EPROM 0 EPROM 32k 14 of 14 PIO 58k 64k ECE 357 Notes and figures are based on or taken from materials in the course textbook: A.S. Tanenbaum, Structured Computer Organization 4th ed., Prentice Hall, Upper Sable River, NJ, 1999. ISBN 0-13-095990-1.