Outline - Microprocessors p General Concepts

advertisement

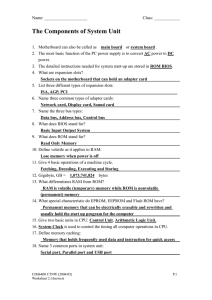

Outline - Microprocessors p General Ge e a Concepts Co cepts - Co Computer pute • Hardware • General Concepts – Microprocessor: Main information processor – Memory – Bus Structure – Central Processing Unit • Central Processing Unit (CPU) – Memory: y Place to store p programs g and data • RAM and ROM – I/O Devices: Peripheral units • • • • • • Registers • Instruction Set – Clock • Architecture • Software: program • Von Neuman vs. Harvard • CISC vs. RISC Chapter 8 ME 534 Graphics p p processor(s) ( ) Audio/sound processor(s) Keyboard / mouse interfaces Serial communication interfaces (e.g. USB controller) Bus drivers, timers, etc. – A set of instructions for the microprocessor to implement a certain task. • For instance, operating system program, application programs 2 General Ge ea O Organization ga at o Chapter 8 ME 534 3 Mini PC C Mainboard a boa d ((Mini-ITX)) Microprocessor Slots for Memory Cards “P t ” ffor I/O Devices “Ports” D i Chapter 8 ME 534 4 Chapter 8 ME 534 5 Memoryy Bus us St Structure uctu e • Two main categories: g • P Parallel ll l electrical l t i l pathways th connecting ti various computer components: – Random Access • Random Access Memory (RAM) – Address bus: specify address locations where data and instructions reside in memory y – Data bus: carries instructions and data to and from memory – Control bus: sends and receives control commands among system components – SRAM, DRAM • Read-Only Memory (ROM) – MROM, MROM PROM PROM, EPROM EPROM, EEPROM EEPROM, Flash – Sequential Access • Disk drives drives, CDROMs CDROMs, DVDs DVDs, etc etc. • Devices can be classifed also by their physical structures or operating principles: – Solid-state, Magnetic, Optical, etc. Chapter 8 ME 534 6 Chapter 8 Random a do Access ccess Device e ce • Length: number of separately addressable memory locations: 2m • Width: n bits of data lines • Size (Capacity): Length Width = 2m of n-bit numbers ME 534 7 Linear ea Memory e o y Model ode Any data residing in such devices can be addressed and accessed at will. Chapter 8 ME 534 8 $FFFF: 1 0 1 0 $FFFE: 0 1 1 0 0 0 0 0 $0005: 0 0 0 0 $0004: 0 0 0 0 $0003: 0 0 0 1 0 0 0 0 0 0 1 0 $0002: 0 0 0 0 $0001: 1 1 1 0 $ 1 0 0 1 0 0 0 0 $0000: 0 0 0 0 0 0 1 1 Chapter 8 0 0 0 1 0 1 0 0 • Computer memory is frequently visualized as large collection of mailboxes: –M Mailil Content C t t – Box location Address • Memory is divided into 8-bit (1 byte) cells with unique addresses. ME 534 9 Variants of RAM Random a do Access ccess Memory e o y ((RAM)) • C Can read d / write it any location l ti iin th the address space, • Volatile: device losses memory contents when power-off, • Faster access time, • Applications: Storage of temporary data • Static St ti RAM (SRAM) – More transistors to hold one “bit” of information. – Very y fast and reliable. – Suitable for cache memory of computers. • Dynamic RAM (DRAM) – Small “die” die area if compared to SRAM SRAM, • Suitable for microfabrication of high capacity RAM. – Need to refresh memory periodically to avoid losing contents • every a few milliseconds to over a hundred ms. – Slower and less reliable if compared to SRAM. – Variables and temporary data generated Chapter 8 ME 534 – Used as main memory of computer systems. 10 Chapter 8 ME 534 11 Variants of ROM Read-Only Read Only Memory (ROM) • MROM: Mask-programmed p g • • • • ROM Can only read the contents. Non-volatile Slower if compared to RAM devices Applications: storage of permanent data – Programmed g when being g manufactured. • PROM: Programmable g ROM – One-time programmable ROM using PROM programmers. – Programs g / firmwares – Constants – Look Look-up up tables – Vector tables etc. Chapter 8 ME 534 • EPROM: Erasable PROM – Users Use s ca can e erase ase tthe e ROM O ((in bulk) via strong ultra-violet light. 12 Chapter 8 ME 534 13 Microprocessor p Variants a a ts o of ROM O (Co (Cont’d) t d) • • EEPROM: Electrically Erasable PROM – Also called E2PROM. – Erased and reprogrammed by electrical signals. – Unlike EPROM, individual locations of the device can be erased and reprogrammed. • Flash Memory: – Classified by number of bits that a microprocessor can manipulate in one operation. • 4-bit 4 bit (i4004) (i4004), 8 8-bit, bit 16 16-bit, bit 32 32-bit, bit 64 64-bit bit (Pentium 4) 4). – Peripheral chips are needed to construct a “computer.” – A microcomputer is a computer using a microprocessor as its it CPU (such ( h as today’s t d ’ d desktop). kt ) • ME 534 14 Chapter 8 ME 534 15 Registers g Central Ce t a Processing ocess g U Unitt • A register is a special storage location i id the inside h CPU CPU: • CPU is the key component of a microprocessor, containing the digital circuitry necessary to interpret and execute program instructions. • Includes a number of units – holds data or a memory address during the execution of an instruction. – number of registers varies from one microprocessor to another. – operations on the registers are extremely fast fast. – Arithmetic Logic Unit • CPU Registers – solelyy perform g general-purpose operations • Used to p perform arithmetic and logic g operations p • arithmetic, logic, flow control – Control Unit – do not occupy (outside) memory space. • Instruction decoding and controlling relevant processor units. • Control Registers (mostly used by microcontrollers) – Register File Courtesy of Freescale Chapter 8 Limitations: – Requires q external memory y to execute p programs; g ; – Peripheral chips are needed to interface with I/O devices; – Glue logic (decoders, (decoders buffers) is needed to interconnect external memory and peripheral interface chips with the microprocessor. – Takes advantages of EPROM and EEPROM technologies, – Efficient in terms of fabrication, – Unlike EEPROM, EEPROM chunks of data can be manipulated one at a time. Chapter 8 A processor implemented on a single IC IC. ME 534 16 Chapter 8 – Configures the peripheral functions ME 534 17 Programs g and Execution Cycles y Instruction Set • Instruction set of a generic microprocessor can be divided into 6 basic categories: – Data transfer and manipulation: Load, store, transfer, exchange, mo e move. • Memory ↔ Memory • Register ↔ Memory • Register ↔ Register – – – – – – Instructions must be represented as binary numbers (called “machine code”) to be decoded by the microprocessor. • Ag generic p processor g goes through g three cycles: y – fetches instructions (one-by-one) from the memory – decodes (“interprets”) a particular instruction – executes it. If applicable, processor does Arithmetic operations: +, -, *, and /. Logic g and bit operations: p AND,, OR,, XOR,, bit shifting, g, etc. Data test and compare Branch (“Go to” or “Jump”) instructions S b Subprogram callll iinstructions t ti Chapter 8 • A program consists of a number of instructions telling the processor how to carry out a specific task task. • Program resides in memory: ME 534 • Read the relevant data from memory, • Carry out the operation on the data data, • Store the result back in the memory. 18 Chapter 8 Clock Bus System TCLK Clock – Depending on the computer architecture, architecture it may take one to several clock periods to execute a particular instruction. ME 534 19 Von Neuman Architecture • Every operation inside the computer system must be perfectly synchronized. precision oscillator ((called “clock”)) generating g g • Ap a square waveform (“clock ticks”) is utilized to time the operations p of the microprocessor p along g with its peripheral units. • The execution speed of processor is loosely related to the clock frequency: Chapter 8 ME 534 • Von Neuman architecture is used d iin mostt microprocessors i like Intel Pentium processors. • Known Kno n also as Princeton architecture. • There is a single bus system (address-, data-, and control bus)) between CPU and memory: y – RAM and program memory share the same bus – Bottleneck: Getting instructions interferes with accessing RAM 20 Chapter 8 ME 534 21 Harvard Architecture CISC versus RISC • Traditionally, most CPUs are Complex Instruction Set Computer (CISC): • Harvard architecture is employed in some CPUs such as PowerPC (PPC) processors and PIC microcontrollers: – – – – – – – – Used in: i80x86, 8051, 68HC12, etc. Many instructions (usually > 100) Many addressing modes U Usually ll ttakes k more th than 1 iinternal t l clock l k cycle l tto execute. Separate program program- and memory bus systems are utilized utilized. Attributes of these bus systems might be entirely different. Architecture enables very fast execution of a program. Bottleneck: Hardware design is quite complicated complicated. Chapter 8 ME 534 22 Chapter 8 CISC C SC versus e sus RISC SC (Co (Cont’d) t d) • A product that uses one or more microcontrollers as controller(s). Also called embedded products. products • Users (consumers) are interested in the functionality of the product product, not the microcontroller itself. • Cellular C ll l phones, h security i systems, home h appliances, and modern automobiles are examples l off embedded b dd d products. d – Used in: SPARC,, ALPHA,, Atmel AVR processors. – Few instructions ((usually y < 50)) – Limited addressing modes – Executes 1 instruction within 1 internal clock cycle. ME 534 23 Embedded bedded Syste Systems s • Most microprocessor with Harvard architecture are Reduced Instruction Set Computer (RISC): Chapter 8 ME 534 24 Chapter 8 ME 534 25