MIPS Data Path

advertisement

MIPS Data Path

CS 154 Lab 5

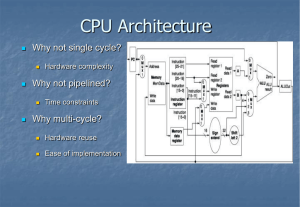

What are the components?

• Sequential Circuit = Register Update Process +

Functional Unit (Combinational) • Registers: (Update process)

– Program Counter (PC)

– Instruction Register (IR)

– Register File Interface (RegA, RegB)

– ALU Interface (ALUout)

– Mem interface (Memory Data Register)

What are the components?

• Function Units (Combinational Component)

– Multiplexer (We will use a lot of MUX’es here)

– ALU

– Sign‐extension Unit (Immediate data)

– Shift (Branch and Jump address calculation)

– PC merger (PC calculation for Jump )

• Memory

How to design a data path?

• We must be able to execute instructions within the data path.

• Instruction type and format:

Type

‐31‐

format (bits)

R

opcode (6)

rs (5)

rt (5)

I

opcode (6)

rs (5)

rt (5)

J

opcode (6)

rd (5)

‐0‐

shamt (5)

funct (6)

immediate (16)

address (26)

• Visualize how data flow in the computer

How to design a data path?

• Common data path for all instructions:

– Instruction Fetch:

– Register Access:

– PC Update

– Memory Access:

IR <‐ Mem[PC];

RegA <‐ RF[rs];

RegB <‐ RF[rt];

RF[rd] <‐ ALUout;

PC <‐ PC + 4;

RF[rt] <‐ Mem[rs+Ext(Imm)];

Mem[AlUout] <‐ RF[rt];

Detailed Analysis of Instructions

• add, sub, and, or, sll, srl:

– R type, opcode = 0, Use function field for ALU

– Syntax: add rd, rs, rt

– Meaning: rd = rs + rt;

– RTL Description:

•

•

•

•

IR <‐ Mem[PC]; PC <‐ PC + 4;

RegA <‐ RF[rs]; RegB <‐ RF[rt];

ALUout <‐ RegA op RegB;

RF[rd] <‐ ALUout;

Detailed Analysis of Instructions

• addi, andi, ori

– I type, use opcode for ALU.

– Syntax: addi rt, rs, C

– Meaning: rt = rs + C (signed);

– RTL Description:

•

•

•

•

IR <‐ Mem[PC]; PC <‐ PC + 4;

RegA <‐ RF[rs]; Imm <‐ Ext(IR[15..0]);

ALUout <‐ RegA op Imm;

RF[rt] <‐ ALUout;

Detailed Analysis of Instructions

• LW, SW

– I type, access memory (load/store), relative address

– Syntax: lw rt, C(rs);

– Meaning: rt = Memory[rs + C];

– RTL Description:

•

•

•

•

•

IR <‐ Mem[PC]; PC <‐ PC + 4;

RegA <‐ RF[rs]; Imm <‐ Ext(IR[15..0]);

ALUout <‐ RegA + Imm;

MDR <‐ Mem[ALUout]; or Mem[ALUout] <‐ RF[rt];

RF[rt] <‐ MDR Detailed Analysis of Instructions

• BEQ, BNE

– I type, branch condition from ALU, relative address

– Syntax: beq rs, rt, C

– Meaning: if (rs == rt) go to PC+4+4*C

– RTL Description:

• IR <‐ Mem[PC]; PC <‐ PC + 4;

• RegA <‐ RF[rs]; RegB <‐ RF[rt]; ALUout <‐ PC + (Ext(IR[15..0]))<<2;

• if(RegA == RegB){PC <‐ ALUout;} Detailed Analysis of Instructions

• J

– J type, absolute address

– Syntax: j C

– Meaning: PC = (PC+4)[31:28] & C*4

– RTL Description:

• IR <‐ Mem[PC]; PC <‐ PC + 4;

• Nothing useful happens here…

• PC <‐ PC[31:28] & (IR[25:0] << 2);

Detailed Analysis of Instructions

• JAL

– J type, stores return address to r31.

– Syntax: j C

– Meaning: r31 = PC + 4; PC = (PC+4)[31:28] & C*4

– RTL Description:

• IR <‐ Mem[PC]; PC <‐ PC + 4;

• Nothing useful happens here

• RF[31] <‐ PC; PC <‐ PC[31:28] & (IR[25:0] << 2);

Summary of Data Path

• PC <‐ PC[31:28] & (IR[25:0] << 2); //jump PC <‐ ALUout;

//branch

PC <‐ PC + 4;

//other instructions

– We need a mux for new PC value (3 input)

• RF[rd]<‐ALUout

//R type

RF[rt] <‐ MDR //ld

– We need a mux for wr_addr;

– We also need a mux for d_in

(rd vs. rt vs. “31”)

(MEM vs. ALU)

Summary of Data Path

• ALUout <‐ RegA + RegB; //R type

ALUout <‐ RegA + Imm; //ld, sw

ALUout <‐ PC + (Ext(IR[15..0]))<<2 //beq, bne

PC <‐ PC + 4

//all instructions

– We need a mux for operand A in ALU (PC vs RegA)

– We need a mux for operand B in ALU (4 input)

• IR <‐ Mem[PC]; RF[rt] <‐ Mem[ALUout]; – We need a mux for memory address (PC vs ALU)