Switched Boost Inverter for Standalone DC Nanogrid Applications

advertisement

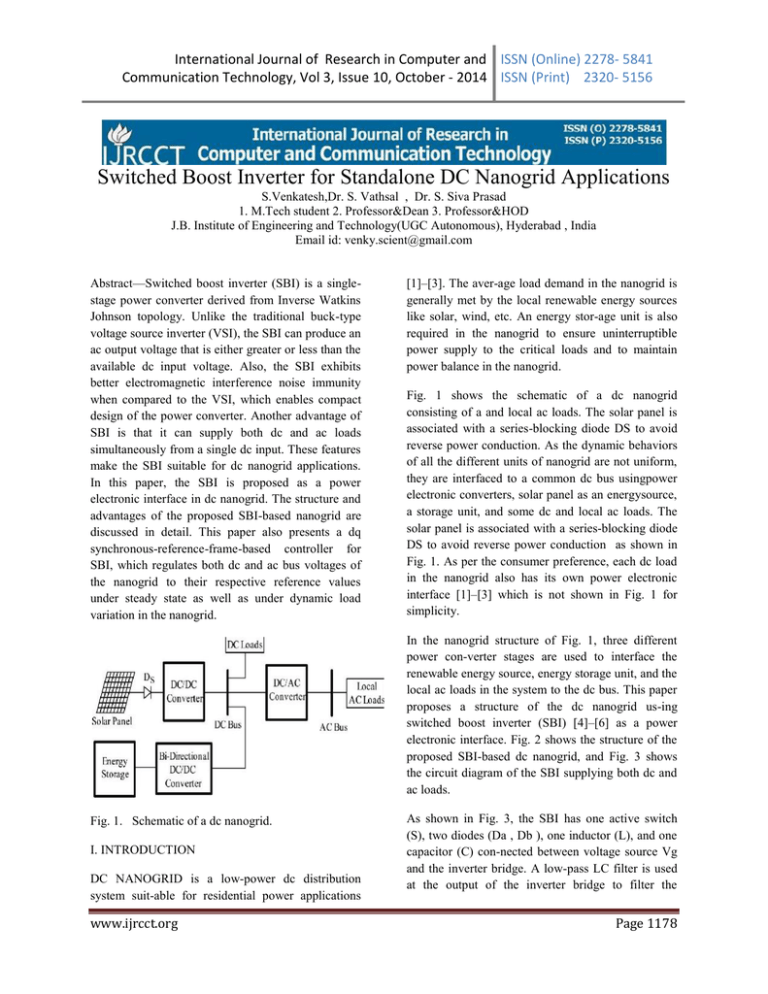

International Journal of Research in Computer and ISSN (Online) 2278- 5841 Communication Technology, Vol 3, Issue 10, October - 2014 ISSN (Print) 2320- 5156 Switched Boost Inverter for Standalone DC Nanogrid Applications S.Venkatesh,Dr. S. Vathsal , Dr. S. Siva Prasad 1. M.Tech student 2. Professor&Dean 3. Professor&HOD J.B. Institute of Engineering and Technology(UGC Autonomous), Hyderabad , India Email id: venky.scient@gmail.com Abstract—Switched boost inverter (SBI) is a singlestage power converter derived from Inverse Watkins Johnson topology. Unlike the traditional buck-type voltage source inverter (VSI), the SBI can produce an ac output voltage that is either greater or less than the available dc input voltage. Also, the SBI exhibits better electromagnetic interference noise immunity when compared to the VSI, which enables compact design of the power converter. Another advantage of SBI is that it can supply both dc and ac loads simultaneously from a single dc input. These features make the SBI suitable for dc nanogrid applications. In this paper, the SBI is proposed as a power electronic interface in dc nanogrid. The structure and advantages of the proposed SBI-based nanogrid are discussed in detail. This paper also presents a dq synchronous-reference-frame-based controller for SBI, which regulates both dc and ac bus voltages of the nanogrid to their respective reference values under steady state as well as under dynamic load variation in the nanogrid. [1]–[3]. The aver-age load demand in the nanogrid is generally met by the local renewable energy sources like solar, wind, etc. An energy stor-age unit is also required in the nanogrid to ensure uninterruptible power supply to the critical loads and to maintain power balance in the nanogrid. Fig. 1 shows the schematic of a dc nanogrid consisting of a and local ac loads. The solar panel is associated with a series-blocking diode DS to avoid reverse power conduction. As the dynamic behaviors of all the different units of nanogrid are not uniform, they are interfaced to a common dc bus usingpower electronic converters, solar panel as an energysource, a storage unit, and some dc and local ac loads. The solar panel is associated with a series-blocking diode DS to avoid reverse power conduction as shown in Fig. 1. As per the consumer preference, each dc load in the nanogrid also has its own power electronic interface [1]–[3] which is not shown in Fig. 1 for simplicity. In the nanogrid structure of Fig. 1, three different power con-verter stages are used to interface the renewable energy source, energy storage unit, and the local ac loads in the system to the dc bus. This paper proposes a structure of the dc nanogrid us-ing switched boost inverter (SBI) [4]–[6] as a power electronic interface. Fig. 2 shows the structure of the proposed SBI-based dc nanogrid, and Fig. 3 shows the circuit diagram of the SBI supplying both dc and ac loads. Fig. 1. Schematic of a dc nanogrid. I. INTRODUCTION DC NANOGRID is a low-power dc distribution system suit-able for residential power applications www.ijrcct.org As shown in Fig. 3, the SBI has one active switch (S), two diodes (Da , Db ), one inductor (L), and one capacitor (C) con-nected between voltage source Vg and the inverter bridge. A low-pass LC filter is used at the output of the inverter bridge to filter the Page 1178 International Journal of Research in Computer and ISSN (Online) 2278- 5841 Communication Technology, Vol 3, Issue 10, October - 2014 ISSN (Print) 2320- 5156 switching frequency components in the inverter output voltage vA B . As shown in Fig. 3, the capacitor C (connected between node VD C and ground) of SBI acts as a dc bus for dc loads while the capacitor Cf (connected between nodes AO and BO ) of SBI acts as an ac bus for ac loads. The operating principle and pulsewidth modulation (PWM) control of the SBI have been explained in Section III of this paper. 2) The output ac voltage of SBI can be either higher or lower than the available source voltage. So, it has wide range of obtainable output voltage for a given source voltage. 3) SBI exhibits better electromagnetic interference (EMI) noise immunity when compared to a traditional voltage source inverter (VSI), as the shoot-through (both switches in one leg of the inverter bridge are turned ON simulta-neously) due to EMI noise will not damage the inverter switches [4]. This reduces extra burden on the power con-verter protection circuit and helps in realization of com-pact design of the power converter. 4) As the SBI allows shoot-through in the inverter legs, it does not require a dead-time circuit and hence eliminates the need for complex dead-time compensation technologies [9], [10]. Fig. 2. Structure of the proposed SBI-based dc nanogrid. Fig. 2 shows structure of the proposed SBI-based dc nanogrid which has the following advantages when compared to the con-ventional structure [1]–[3]: 1) SBI is a single-stage power converter that can supply both dc (between node VD C and ground) and ac loads (between nodes AO and BO ) simultaneously from a single dc input. So, it can realize both the dc-to-dc converter for solar panel and the dc-to-ac converter in a single stage. This decreases size and cost of overall system. Fig. 3. Circuit diagram of SBI supplying both dc and ac loads. www.ijrcct.org This paper presents a structure of the SBI-based dc nanogrid and its advantages compared to the conventional structure shown in Fig. 1. This paper also describes the steady-state and small-signal analysis of SBI supplying both dc and ac loads along with its PWM control technique. Also, a closed-loop control strategy of SBI that regulates both the dc and ac bus voltages of SBI to their respective reference values has been given in this paper. The closed-loop control strategy has also been experimentally validated using a 0.5-kW laboratory prototype of SBI shown in Fig. 3. The organization of this paper is as follows. Section II presents a review of the SBI and its comparison with the traditional two-stage conversion system. Section III describes the steady-state operation of the SBI supplying both dc and ac loads, followed by its PWM control strategy. The small-signal analysis of SBI and design of a closed-loop control system using synchronous reference frame (SRF) approach has been given in Section IV. In Section V, the control strategy has been experimentally validated using a 0.5-kW laboratory prototype of SBI controlled using TMS320F28335 DSP. Section VI presents some conclud-ing remarks of this paper. Page 1179 International Journal of Research in Computer and ISSN (Online) 2278- 5841 Communication Technology, Vol 3, Issue 10, October - 2014 ISSN (Print) 2320- 5156 D)•TS intervals of a switching cycle TS are shown in Fig. 4(b) and (c), respectively. As shown in Fig. 4(b), during D•TS interval, the two switches of the converter are in position 1, and inductor L is connected between the input and the output. Similarly, during (1 – D)•TS interval, the switches are in position 0 and the inductor is con-nected between the output and the ground, as shown in Fig. 4(c). Fig. 4. (a) Schematic of IWJ topology. (b) Equivalent circuit of IWJ topology in D•TS interval. (c) Equivalent circuit of IWJ topology in (1 – D)•TS interval. Note that in this paper, GS , GS 1 , GS 2 , GS 3 , and GS 4 repre-sent the gate control signals of switches S, S1 , S2 , S3 , and S4 , respectively, fed through a noninverting gate driver. Lowercase letters are used to represent the sinusoidal signals and uppercase letters are used to represent the dc signals. Uppercase letter with a hat (ˆ) represents peak value of a signal, while lowercase let-ter with a hat (ˆ) represents small-signal variation in the signal. Also x is the phasor representation of a sinusoidal signal x. The x superscript “∗” is used to represent the reference signals to the control system of dc nanogrid. II. SWITCHED BOOST INVERTER TOPOLOGY SBI is a single-stage power converter derived from Inverse Watkins Johnson (IWJ) Topology [4]. This topology exhibits properties similar to that of a Zsource inverter (ZSI) [7] with lower number of passive components and more active compo-nents. This section presents a review of the approach used to derive the SBI from IWJ topology. A detailed comparison of SBI with a traditional two-stage dc-toac conversion system is also given in this section. A. Derivation of SBI From IWJ Topology The schematic of IWJ converter [26] is shown in Fig. 4(a) and its equivalent circuits in D•TS and (1 – www.ijrcct.org Fig. 5. (a) Realization of CIWJ topology using power semiconductor devices. (b) Connection of a VSI across the dc output node VD C of CIWJ topology. (c) Connection of a VSI across the switching terminal Vi of the CIWJ topology (switch Si can be realized by using the shoot-through state of the VSI). Interchanging the D•TS (position 1), and (1 – D)•TS (position 0) intervals of IWJ converter leads to Fig. 4(d). This configuration is named as the complementary IWJ (CIWJ) topology in [4]. Note that this interchange has no impact on the states of the converter. However, as far as implementation is concerned, this will imply that the controlled switch and diode of CIWJ and IWJ are interchanged. Fig. 5(a) shows the realization of CIWJ topology using power semiconductor devices [4], [5]. The output of this converter is a dc voltage VD C . In order to convert this dc voltage to an ac voltage, one has to use a VSI. This VSI may be directly connected at the output node VD C of CIWJ topology [shown in Fig. 5(b)], which becomes a cascaded connection of a dc–dc converter and a regular VSI. But this combination cannot overcome the general limitations Page 1180 International Journal of Research in Computer and ISSN (Online) 2278- 5841 Communication Technology, Vol 3, Issue 10, October - 2014 ISSN (Print) 2320- 5156 of a traditional VSI [7], [8], viz., 1) dead-time is necessary to prevent the damage of the switches in the event of shoot-through in inverter phase legs, 2) complex dead-time compensation technologies should be used to compensate the waveform distortion caused by dead-time. Fig. 5(c) shows another possible connection of the VSI, in which the inverter bridge is connected across the switch node Vi of the CIWJ topology. Note that this combination requires only controlled switch S apart from the inverter bridge. The switch Si of CIWJ topology can be realized by utilizing the shootthrough state of the inverter bridge. Also, similar to the cascaded connection shown in Fig. 5(b), this circuit can also supply a dc load (at the output of CIWJ) and an ac load (at the output of the inverter bridge) simultaneously from a single dc voltage source Vg . The circuit of Fig. 5(c) is named as SBI topology in [4]. Note that it is not a direct cascade connection of CIWJ topology and VSI, as the inverter bridge is connected at a switch node of CIWJ converter but not at its output terminal. When compared to the cascaded connection shown in Fig. 5(b), the SBI has following advantages: 1) In the event of shoot-through in any phase leg of the in-verter bridge, the diode Db is reversebiased and capaci-tor C is disconnected from the inverter bridge. Now, the current through the circuit is limited by the inductor L. So, similar to ZSI, shootthrough does not damage the switches of the SBI also. 2) As the SBI allows shoot-through, no deadtime is needed to protect the converter. Also this circuit exhibits better EMI noise immunity compared to a traditional VSI. This is because the impedance network of ZSI uses two inductors, two capacitors, and a diode apart from the inverter bridge, while the SBI requires only one inductor, one capacitor, a controlled switch, and two diodes. The reduction in number of passive components leads to the reduced size of the power converter stage. Also ZSI requires passive components with high consistency [7], [8] which is not the case with SBI. Another major advantage of SBI when compared to ZSI is that it can supply both dc and ac loads simultaneously from a single dc voltage source, as shown in Fig. 3. However, the limitation of SBI is that its peak inverter input voltage is only (1 – D) times that of ZSI, where D is the shoot-through duty ratio of the inverter bridge. A more detailed quantitative comparison of SBI and ZSI is given in [4]. B. Comparison of SBI With a Traditional Two-Stage DC-to-AC Conversion System In the previous section, it is shown that the SBI is a single-input, two-output (one dc output and one ac output) power con-verter derived from IWJ converter and a VSI. Similar to the tra-ditional two-stage dc-toac conversion system shown in Fig. 6, the SBI can also generate an ac output voltage that is either greater or less than the input dc voltage. However, the SBI has certain advantages and limitations when compared to the two-stage conversion system shown in Fig. 6, which are discussed below. 1) Dead-Time Requirement: A shoot-through event in the inverter bridge of the two-stage conversion system damages the power converter stage, as well as the dc loads connected to the dc bus of the nanogrid. So a dead-time circuit is necessary to minimize the occurrence of shoot-through events in this system. 3) Since dead-time is not required, there is no need of extra dead-time compensation technologies to compensate the waveform distortion caused by dead-time. Note that a ZSI [7] also exhibits similar advantages of SBI mentioned above. But the SBI achieves these properties with lower number of passive components and more active com-ponents compared to ZSI [4]. www.ijrcct.org Page 1181 International Journal of Research in Computer and ISSN (Online) 2278- 5841 Communication Technology, Vol 3, Issue 10, October - 2014 ISSN (Print) 2320- 5156 Fig. 6. Traditional two-stage dc-to-ac conversion system: Boost converter cascaded with a VSI. Moreover, to compensate the waveform distortion caused by dead-time, one has to use the complex dead-time compensation technologies [8]–[10]. This is not the case with SBI, as it allows shoot-through in the inverter phase legs. So the use of SBI elim-inates the need for a dead-time circuit as well as the requirement of dead-time compensation technologies. 2) Reliability and EMI Noise Immunity: Even with a dead-time circuit, the probability of a shootthrough event cannot be eliminated completely because an EMI noise can also cause shoot-through in the inverter phase legs [4], [7]. With the use of SBI, the shoot-through event does not damage the switches of the power converter. So, SBI exhibits better EMI noise immu-nity and hence has better reliability compared to the two-stage conversion system. 3) Extreme Duty Cycle Operation: At the extreme duty ratio operation (e.g., for D ≥ 0.75) of a conventional boost converter, the inductor L is charged over a longer time duration in the switching cycle, and very small time interval is left to discharge the inductor through the output diode Db . So this diode should sustain a short pulsewidth current with relatively high ampli-tude. Also, this causes severe diode reverse recovery current and increases the EMI noise levels in the converter [11]– [14]. This also imposes a limit on the switching frequency of the boost converter and thus increases the size of the passive components used in the twostage conversion system shown in Fig. 6. In case of SBI, the maximum shoot-through duty ratio is always limited to 0.5 for a positive dc bus voltage VD C [4]. So, even when the converter operates at the point of maximum conversion ratio, the conduction time of the diodes Da , Db of SBI is approximately equal to 50% of the switching time period, which alleviates the problems due to extreme duty ratio operation of a boost converter. So, SBI can www.ijrcct.org operate at relatively higher switching frequencies compared to the traditional two-stage conversion system. This also decreases the size of passive components used in the power converter. 4) Voltage Stress of Switching Devices: Table I compares the voltage stress of the semiconductor devices used in the SBI and the two-stage conversion system shown in Fig. 6. From this table, it can be observed that the switch “S” has less voltage TABLE I, VOLTAGE STRESS COMPARISON OF SBI AND TWO-STAGE CONVERSION SYSTEM stress (VD C – Vg ) in case of SBI. For all other devices, the voltage stress is same for both SBI and the two-stage conversion system. 5) Maximum Conversion Ratio: The maximum conversion ratio (VD C /Vg ) of a practical boost converter cannot exceed 3.0 (approximately), due to the effects of various nonidealities [26] such as DCR/ESR of the passive components, on-state voltage drops of the semiconductor devices, etc. This value may slightly vary depending on the actual values of nonideal elements present in the converter. Similarly, the rms ac output voltage (vAC (rms)) of a single-phase inverter using sinusoidal PWM cannot exceed _√ 1 2 times the dc link voltage (VD C ) [25], [27] in the linear modulation range (0 < M < 1), for a low distortion sine wave output. So the maximum overall rms ac-to-dc conversion ratio of two-stage conversion system shown in Fig. 6 is approximately 2.12. This value may still decrease if the effects of nonidealities in VSI are taken into consideration. The rms ac-to-dc conversion ratio of the two-stage conversion ratio may be increased slightly by using Page 1182 International Journal of Research in Computer and ISSN (Online) 2278- 5841 Communication Technology, Vol 3, Issue 10, October - 2014 ISSN (Print) 2320- 5156 semiconductor devices with very low forward voltage drops and passive components with very low ESR/DCR. This enhances the overall cost of the power converter stage. Another way to increase the conversion ratio of the two-stage conversion system is to use high step-up dc-to-dc converters [12]–[14] or the converters with trans-former/coupled inductor [8], [26]. These converters require ad-ditional semiconductor devices and passive components which increase the size as well as cost of the power converter stage. In this paper, it is shown experimentally in Section V that the maximum rms ac-to-dc conversion ratio of the SBI is 2, which is comparable to that of a twostage conversion system. Also, as explained above, SBI has no diode reverse recovery problems with extreme duty ratio operation. So this conversion ratio is possible even at high switching frequency and with better reliability and EMI noise immunity. Note that, in this paper, the SBI has been tested with only one PWM control technique proposed in [6], where the maximum value of modulation index (M) is limited by the shoot-through duty ratio (D). However, as the operation of SBI is similar to ZSI, it is possible to extend maximum boost control and maximum constant boost control techniques of ZSI [15]–[17] to SBI. This may help SBI to achieve higher conversion ratios compared to the two-stage conversion system, without increasing the number of devices. 6) Number of Control Variables: Similar to a two-stage con-version system, the SBI also has two control variables: Shoot- through duty ratio (D) and the modulation index (M). The dc bus voltage VD C is controlled by D, while ac output voltage of the converter is controlled by M. However, similar to ZSI [7], the value one of these two control variables decides the upper limit of the second control variable of SBI. The mathematical relation between D and M depends on the control technique used. Note that, as mentioned above, it is possible to extend most of the PWM control techniques of ZSI [15]–[17] to control the SBI also. www.ijrcct.org 7) Number of Devices: As shown in Fig. 3, the SBI requires five active switches, six diodes, two inductors, and two capacitors for its realization. The two-stage conversion system shown in Fig. 6 uses only one diode (Da ) less compared to the SBI. However, in a dc nanogrid, the input comes from a renewable en-ergy source, e.g., solar panel or fuel cell, which should always be associated with a series diode to block the reverse power flow [7], [18], [19]. So the diode Da of SBI can be a part of the renewable energy source which eliminates the need for an external diode. Thus, the number of devices in both converters is same. B. PWM Control of SBI The SBI utilizes the shoot-through interval of the Hbridge to invoke the boost operation. So, the traditional PWM tech-niques of VSI [25], [27] have to be modified to incorporate the shoot-through state, so that they are suitable for SBI. In [6], a PWM scheme for SBI is developed based on the traditional sine-triangle PWM with unipolar voltage switching [25], [27]. This technique has been illustrated in Fig. 8 during positive and negative half cycles of the sinusoidal modulation signal vm (t) [shown in Fig. 8(a)]. As shown in Fig. 8(b) and (d), during positive half cycle of vm (t) (vm (t) > 0), the gate control signals GS 1 and GS 2 are generated by comparing the sinusoidal modulation signals vm (t), and –vm (t) [shown in Fig. 8(a)] with a high-frequency triangular carrier vtri (t) of amplitude Vp . The frequency fS of the carrier signal is chosen such that fS _ fO . Therefore, vm (t) is assumed to be nearly constant in Fig. 8(d). The signals ST1 and ST2 are generated by comparing vtri (t) with two constant voltages VST and –VST , respectively. The purpose of these two signals is to insert the required shoot-through interval D•TS in the PWM signals of the inverter bridge. Now the gate control signals for switches S3 , S4 , and S can be obtained using the logical expressions given as follows: Page 1183 International Journal of Research in Computer and ISSN (Online) 2278- 5841 Communication Technology, Vol 3, Issue 10, October - 2014 ISSN (Print) 2320- 5156 GS 3 = GS 2 +ST1 ; GS 4 = GS 1 + ST2 ; GS = ST1 + ST2 . (10) Similarly, during negative half cycle of vm (t) (vm (t) < 0), the gate control signals GS 3 and GS 4 are generated by comparing the modulation signals – vm (t), and vm (t) with the triangular carrier vtri (t). The shoot-through signals ST1 and ST2 are generated in the same manner as in the positive half cycle. The gate control signals for switches S1 , S2 , and S can be obtained using the logical expressions given as follows: GS 1 = GS 4 +ST1 ; GS 2 = GS 3 + ST2 ; GS = ST1 + ST2 . (11) SWITCHED BOOST INVERTER Fig. 7. Experimental results of SBI with different values of rms ac-to-dc conversion ratios and input voltages. CONCLUSION This paper presents a novel power electronic interface called switched boost inverter (SBI) for dc nanogrid applications. It shown that the SBI is a single-stage power converter that can supply both dc and ac loads simultaneously from a single dc input. It is also proven that the SBI can generate an ac output voltage that is either higher or lower than the available source voltage. This paper also describes the advantages and limitations of SBI when compared to the ZSI and the traditional two-stage dcto-ac conversion system. The steady-state and smallsignal analysis of the SBI supplying both dc and ac loads, and a PWM control technique suitable for SBI are also described in this paper. Also, the analysis and design of a SRF-based controller that regulates both the dc and ac bus voltages of SBI to their respective reference values has been discussed in this paper. The steady state and dynamic performance as well as the low cross regulation of the closed-loop control strategy have been experimentally validated using a 0.5-kW laboratory prototype of SBI supplying both dc and ac loads. The performance of SBI has been tested experimentally with an isolation transformer and also with three different types of ac loads: R, RL, and nonlinear loads. It can be concluded from the experimental results that the control strategy of SBI shows excellent performance during steady state as well as during a step change in either dc or ac load in the system. These results confirm the suitability of SBI and its closed-loop control strategy for dc nanogrid applications. REFERENCES [1] D. Boroyevich, I. Cvetkovic, D. Dong, R. Burgos, F. Wang, and F. C. Lee, “Future electronic power distribution systems—A contemplative view,” in Proc. 12th IEEE Int. Conf. Optim. Electr. Electron. Equip., May 2010, pp. 1369–1380. Fig. 8. (a) Experimental results of SBI supplying an RL load. (b) Experi-mental results of SBI supplying a rectifier load. www.ijrcct.org [2] J. Schonberger, R. Duke, and S. D. Round, “DC-bus signalling: A dis-tributed control strategy Page 1184 International Journal of Research in Computer and ISSN (Online) 2278- 5841 Communication Technology, Vol 3, Issue 10, October - 2014 ISSN (Print) 2320- 5156 for a hybrid renewable nanogrid,” IEEE Trans. Ind. Electron., vol. 53, no. 5, pp. 1453–1460, Oct. 2006. [3] H. Kakigano, Y. Miura, and T. Ise, “Lowvoltage bipolar-type DC micro-grid for super high quality distribution,” IEEE Trans. Power Electron., vol. 25, no. 12, pp. 3066–3075, Dec. 2010. [4] S. Mishra, R. Adda, and A. Joshi, “Inverse Watkins-Johnson topology based inverter,” IEEE Trans. Power Electron., vol. 27, no. 3, pp. 1066– 1070, Mar. 2012. [5] S. Upadhyay, S. Mishra, and A. Joshi, “A wide bandwidth electronic load,” IEEE Trans. Ind. Electron., vol. 59, no. 2, pp. 733–739, Feb. 2012. [6] R. Adda, S. Mishra, and A. Joshi, “A PWM control strategy for switched boost inverter,” in Proc. 3rd IEEE Energy Convers. Congr. Expo., Phoenix, AZ, 2011, pp. 4208–4211. [7] F. Z. Peng, “Z-source inverter,” Trans. Ind. Appl., vol. 39, no. 2, pp.504–510, Mar./Apr. 2003. IEEE [8] Y. Zhou and W. Huang, “Single-stage boost inverter with coupled induc-tor,” IEEE Trans. Power Electron., vol. 27, no. 4, pp. 1066–1070, Apr. 2012. [9] L. Chen and F. Z. Peng, “Dead-time elimination for voltage source in-verters,” IEEE Trans. Power Electron., vol. 23, no. 2, pp. 574–580, Mar. 2008. [10] S. H. Hwang and J. M. Kim, “Dead-time compensation method voltage-fed PWM inverter,” IEEE Trans. Energy Convers., vol. 25, no. 1, pp. 1– 10, Mar. 2010. [11] F. Gao, P. C. Loh, R. Teodorescu, and F. Blaabjerg, “Diode-assisted buck– boost voltagesource inverters,” IEEE Trans. Power Electron., vol. 24, no. 9, pp. 2057–2064, Sep. 2009. [12] A. A. Fardoun and E. H. Ismail, “Ultra stepup DC–DC converter with reduced switch stress,” IEEE Trans. Ind. Appl., vol. 46, no. 5, pp. 2025– 2034, Sep./Oct. 2010. www.ijrcct.org [13] E. H. Ismail, M. A. Al-Saffar, and A. J. Sabzali, “High conversion ratio DC–DC converters with reduced switch stress,” IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 55, no. 7, pp. 2139–2151, Aug. 2008. [14] Q. Zhao and F. C. Lee, “High-efficiency, high step-up DC–DC converters,” IEEE Trans. Power Electron., vol. 18, no. 1, pp. 65–73, Jan. 2003. [15] P. C. Loh, D. Vilathgamuva, Y. S. Lai, G. Chua, and Y. Li, “Pulse-width modulation of Zsource inverters,” IEEE Trans. Power Electron., vol. 20, no. 6, pp. 1346–1355, Nov. 2005. [16] F. Z. Peng, M. Shen, and Z. Qian, “Maximum boost control of the Z-source inverter,” IEEE Trans. Power Electron., vol. 20, no. 4, pp. 833– 838, Jul. 2005. [17] M. Shen, J. Wang, A. Joseph, F. Z. Peng, L. M. Tolbert, and D. J. Adams, “Constant boost control of the z-source inverter to minimize current ripple and voltage stress,” IEEE Trans. Ind. Appl., vol. 42, no. 3, pp. 770–778, May/Jun. 2006. [18] Y. Huang, M. Shen, F. Z. Peng, and J. Wang, “Z-source inverter for residential photovoltaic systems,” IEEE Trans. Power Electron., vol. 21, no. 6, pp. 1776–1782, Nov. 2006. [19] R. J. Wai, C. Y. Lin, R. Y. Duan, and Y. R. Chang, “High-efficiency DC-DC converter with high voltage gain and reduced switch stress,” IEEE Trans. Ind. Electron., vol. 54, no. 1, pp. 354–364, Feb. 2007. [20] U. A. Miranda, M. Aredes, and L. G. B. Rolim, “A DQ synchronous reference frame current control for single-phase converters,” in Proc. 36th IEEE Power Electron. Specialists Conf. (PESC), Recife, Brazil, Jun. 2005, pp. 1377–1381. [21] B. Crowhurst, E. F. El-Saadany, L. El Chaar, and L. A. Lamont, “Single-phase grid-tie inverter control using DQ transform for active and reactive load power compensation,” in Proc. IEEE Page 1185 International Journal of Research in Computer and ISSN (Online) 2278- 5841 Communication Technology, Vol 3, Issue 10, October - 2014 ISSN (Print) 2320- 5156 Int. Conf. Power Energy, Kuala Lumpur, Malaysia, Nov./Dec. 2010, pp. 489–494. Data Manual [Online]. Available: http://www.ti.com/lit/ds/ symlink/tms320f28335.pdf [22] P. Rodriguez, R. Teodorescu, I. Candela, A. Timbus, M. Liserre, and F. Blaabjerg, “New positivesequence voltage detector for grid synchro-nization of power converters under faulty grid conditions,” in Proc. 37th IEEE Power Electron. Spec. Conf., Jeju, Korea, Jun. 2006, pp. 1–7. [31] Texas Instruments (2009, Jul.), TMS320×2833x, 2823x Enhanced Pulse Width Modulator (ePWM) Module Reference Guide [Online]. Available: http://www.ti.com/lit/ug/sprug04a/sprug04a.pdf [23] M. Ciobotaru, R. Teodorescu, and F. Blaabjerg, “A new single-phase PLL structure based on second order generalized integrator,” in Proc. 37th IEEE Power Electron. Spec. Conf., Jeju, Korea, Jun. 2006, pp. 1–6. [24] J. Liu, J. Hu, and L. Xu, “Dynamic modeling and analysis of Z source converterderivation of AC small signal model and designoriented anal-ysis,” IEEE Trans. Power Electron., vol. 22, no. 5, pp. 1786–1796, Sep. 2007. [25] D. G. Holmes and T. A. Lipo, Pulse Width Modulation for Power Con-verters: Principles and Practice. Piscataway, NJ: IEEE Press, 2003. [26] R. W. Erickson and D. Maksimovic, Fundamentals of Power Electronics, 2nd ed. Norwell, MA: Kluwer, Jan. 2001. [27] N. Mohan, T. Undeland, and W. Robbins, Power Electronics: Converters, Applications and Design, 2nd ed. New York: Wiley, 1995. [28] K. Selvajyothi and P. A. Janakiraman, “Reduction of voltage harmonics in single phase inverters using composite observers,” IEEE Trans. Power Del., vol. 25, no. 2, pp. 1045–1057, Apr. 2010. [29] Z. Yao and L. Xiao, “Control of singlephase grid-connected inverters with nonlinear loads,” IEEE Trans. Ind. Electron., 2012, to be published. doi:10.1109/TIE.2011.2174535. [30] Texas Instruments (2012, May), TMS320F28335 Digital Signal Con-troller (DSC): www.ijrcct.org Page 1186