Nyquist Rate Analog-to

advertisement

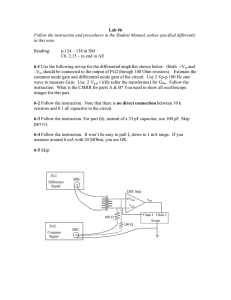

Nyquist Rate Analog-to-Digital Converters Tuesday uesday 9th 9t of o March, a c , 2009, 009, 9:15 9 5 – 11:00 00 Snorre Aunet, sa@ifi.uio.no Nanoelectronics Group, Dept. of Informatics Office 3432 Last time – and today, Tuesday 9th of March: L Last time: i 12.1 Decoder-Based Converters 12.2 Binary-Scaled Converters 12.3 Thermometer-Code Converters 12.4 Hybrid Converters Today – from the following chapters: 13.1 Integrating Converters 13.2 Successive-Approx. Converters 13 3 Algorithmic (or cyclic) A/D Converters 13.3 13.4 Flash (or parallel) converters 13.5 Two-Step A/D converters 13.6 13 6 Interpolating A/D Con Converters erters ( 16/3 16/3-10) 10) 13.7 Folding A/D Converters (16/3-10) 13.8 Pipelined A/D Converters 13 9 Time 13.9 Time-Interleaved Interleaved A/D Converters Different A/D Converter Architectures Low-to-Medium Speed High Accuracy Medium Speed Medium Med u Accuracy Accu acy High Speed Low-to-Medium Low to Med u Accuracy Integrating Successive approximation Flash Oversampling Algorithmic Two-Step Interpolating Folding Pipelined Time-interleaved Different ADCs depending p g on needs A/D-conversion – Basic Principle V ------LSB ------- = 1/4 = 1 LSB V B out Vin A/D Bout ref 11 10 Vref 01 00 –1 0 –2 1/4 1/2 3/4 1 Vi n --------V ref –N V ref b 12 + b 22 + + b N2 = Vin x 1 1 where – --- VLSB x --- VLSB 2 2 • The analog input value is mapped to discrete digital output t t value l • Quantization error is introduced Integrating Converters (13.1) S 2 S 1 S 2 C1 –V in S 1 R 1 C Comparator t V x Control V ref logic b1 b2 Counter b 3 b N (Vin is held constant during conversion.) Clock f • • • • 1 = ----------clk T clk B out Vx(t) = Vin t / RC (Vx ramp derivative depending on Vin ) High linearity and low offset/gain error Small amount of circuitry Low conversion speed • 2N+1 * 1/Tclk (Worst case) Integrating Converters V x –Vin3 Phase (I) Phase (II) (Constant slope) –Vin2 –Vin1 Time T 1 T2 (Three values for three inputs) • The digital output is given by the count at the end of T2 • The digital output value is independent of the time-constant RC Dual slope ADC Integrating Converters – careful choice of T1 can attenuate frequency components superimposed on the input signal 0 –20 dB/decade slope H (f) (dB) –10 –20 –30 10 60 100 120 180 240 300 Frequency (Hz) (Log scale) • In I the h above b case, 60 H Hz and dh harmonics i are attenuated when T1 is an integer multiple of 1/60 Hz. • Sinc-response with rejection of frequencies multiples of 1/T1 Successive approx ADC algorithm (13.2) • If we have weights of 1 kg, 2 kg, 4 kg, 8 kg, 16 kg, 32 kg and will find the weight of an unknown X assumed to be 45 kg. • 1011012 =1*32+0*16+1*8+1*4+0 *2 1*1 *2+1*1 = 4510 Successive-Approximation Converters Start Signed input Sample Vin , VD/A = 0 , i = 1 Vin VD/A No Yes bi = 1 bi = 0 V D/A VD/A + Vr ef 2 i + 1 V D/A VD/A – Vr ef 2 i + 1 ii +1 No iN Yes Stop • Uses binary-search algorithm • Accuracy of 2N requires N steps t • The digital signal accuracy is i within ithi +// 0.5 05 Vref • Medium speed • Medium resolution • Relatively moderate complexity DAC-Based Successive Approximation Vin S/H Successive-approximation register (SAR) and control logic b1 b2 bN Bout D/A converter VD/A V ref • VD/A is i adjusted dj d untilil the h value l iis within i hi 1LSB off Vin • Starts with MSB and continues until LSB is found • Requires DAC, S/H, Comparator and digital logic • The DAC is typically y y limiting g the resolution Succ. Approx ADC, example 13.2 10. mars 2010 14 Charge-Redistribution A/D-Converter (unipolar) • Instead of using a separate DAC and setting it equal to the input voltage (within 1 LSB) as for the DAC based converter from figure 13 13.5, 5 one can use the error signal equaling the difference between the input signal Vin, and the signal, DAC output, VD/A Numbers from 13.2 setting an error signal V equal to Vin – VD/A – modified succ. approx as in fig. 13.6 Unipolar Charge-Redistribution A/D-Converter Vx 0 s2 SAR 16C 8C b1 4C b2 2C b3 C b4 C b5 s3 1. Sample mode s1 Vin s2 Vx = –Vin Vref 16C 8C b1 4C b2 2C b3 C b4 C SAR b5 s3 s1 Vref Vx = – Vin + ----------2 16C 8C b1 4C b 2 2C b 3 V in s2 C b 4 SAR C b 5 s3 3. Bit cycling s1 Vin Vref V ref 2. Hold mode Charge-Redistribution A/D-Converter • Sample mode: • All capacitors charged to Vin while the comparator is reset to its threshold voltage g through g S2. The capacitor p array y is performing S/H operation. • Hold mode: • The comparator is taken out of reset by opening S2, then all capacitors are switched to ground. Vx is now equal to –Vin. Finally S1 is switched so that Vref can be b applied li d tto th the capacitors it d during i bit-cycling. • Bit-cycling: • The largest capacitor is switched to Vref. Vx goes to –Vin + Vref/2. If Vx is negative, then Vin is greater than Vref/2 and the MSB capacitor is left connected to Vref. Otherwise the MSB capacitor is disconnected and the same procedure is repeated N times until the LSB capacitor has been evaluated. 10. mars 2010 19 10. mars 2010 20 10. mars 2010 21 Succ. Approx Succ Approx. Approach flow graph Start Signed input Sample Vin , VD/A = 0 , Vi n VD/A i = 1 N No Yes bi = 1 bi = 0 V D/A VD /A + Vr ef 2 i + 1 V D/A VD /A – Vr ef 2 i + 1 ii +1 N No iN Yes 10. mars 2010 Stop 22 Signed Charge redistribution A/D (Fig. 13.8) • Resembling the unipolar version (Fig 13.7) (Fig. 13 7) • Assming Vin is between +/- Vref/2 • Disadvantage: Vin i attenuated by a factor 2, making noise more of ap problem for high g resolution ADCs y error in the MSB capacitor p • Any causes both offset and a signdependent gain error, leading to INL errors Resistor-Capacitor Hybrid (figure 13.9 in ”J & M”) • First all capacitors are charged to Vin b f before the th comparator t is i being b i reset. t • Next a succ. approx. conversion is performed to find the two adjacent resistor nodes having voltages larger and smaller than Vin • One bus will be connected to one node while the other is connected to the other node. All of the capacitors are connected to the bus having the lower voltage voltage. • Then a successive approximation using the capacitor capacitor-array array network is done, starting with the largest capacitor… Speed estimate for charge-redistribution converters • RC titime constants t t often ft limit li it speed d • Individual time constant due to the 2C cap.: cap : (Rs1+R+Rs2)2C • (R ; bit line) ( s1+R+Rs2))2NC,, for the • Taueq=(R circuit in fig. 13.12 • For better tha 0.5 LSB accuracy: eT/T T/Taueq < 1/(2N+1), T = charging time • T > Taueq (N+1) ln2 = 0.69(N+1)Taueq • 30 % higher than from Spice simulations ((”J & M”)) Algorithmic (or Cyclic) A/D Converter Start Signed input S Sample l V = Vin, i = 1 No V>0 Yes bi = 1 V 2(V – Vref /4) i i+1 No i>N Yes Stop bi = 0 V 2(V + Vref /4) (13.3) • Similar to the Successive approximation converter • Constant Vreff • Doubles the error each cycle, instead of halving the reference voltage in each cycle, y , like succ. approx. pp conv. • Requires an accurate multiply-by-2 p y y amplifier p • Accuracy can be improved by operating in four cycles (instead of two) • compact Ratio-Independent Algorithmic Converter Out Vin S/H X2 G i amp Gain S/H Cmp Shift register Vref /4 –Vref Vref /4 • Simple circuitry • Due to the cyclic operation the circuitry are reused in time • Fully differential circuits normally used Ratio-Independent Algorithmic Converter Q1 C2 C2 C1 C1 Verr Verr Cmp Cmp Q1 Q1 1. Sample remainder and cancel input-offset voltage. Q1 2. Transfer charge Q1 from C1 to C2. C2 C2 C1 C1 Verr Verr Cmp Q2 Cmp Q1+Q2 Vout = 2 Verr 3. Sample input signal with C1 again after storing charge Q1 on C2. 4. Combine Q1 and Q2 on C1, and connect C1 to output. • The basic idea is to sample the input signal twice using the same capacitor capacitor. During the 2nd sampling the charge from the 1st capacitor is stored on a 2nd capacitor whose size is unimportant. After the 2nd sampling both charges are recombined bi d iinto t th the 1st capacitor it which hi h is i then th connected t d between b t the th opamp input and output. • Does not rely on capacitor matching, is insensitive to amplifier offset. Flash (Parallel) Converters (13.4) Vref R --2 R Vin Over range Vr7 R Vr6 R Vr5 (2N –1) to N R Vr4 R Vr3 R R R 2 Vr2 Vr1 Comparators encoder N digital outputs • High speed – among the fastest • 2N comparators in parallel, each connected co ec ed to od different e e nodes odes – area consuming • High power consumption Thermometer-code code output fed • Thermometer into decoder • Nands used for simpler decoding and error detection (bubble error) • Differential comparator required to ensure sufficient PSSR • Top and bottom resistors chosen to create the 0.5 LSB offset in an A/D converter Flash converter 10. mars 2010 30 Clocked CMOS comparator • When the clock (”phi”) is high, high the inverter is set to its bistable point, Vin = Vout (= Vdd/2). The other (left) side of C is charged to Vri. • When the clock (”phi”) goes low, the inverter switches, it h d depending di on the th voltage lt diff difference between Vri and Vin. (Vri > Vin; 1 output, Vri < Vin; 0 output from inv. ) • Differential Diff ti l iinverters t h helps l poor PSRR with ith this thi simple comparator solution. Issues in Designing Flash A/D Converters • Input p Capacitive p Loading: g The large g number of comparators p connected to Vin results in a large capacitive load on at the input node which increases power and reduces speed • Comparator p Latch-to-Track Delay: y The internal delay y in the comparator p when going from latch to track mode • Signal and/or Clock Delay: Differences in signal/clock delay between the comparators p may y cause errors. Example: p A250-MHz,, 1-V p peak inputp sinusoid converted with 8-bit resolution requires a precision of 5ps. Can be reduced by matching the delays and capacitive loads on the signal/clock. • Substrate and Power-Supply pp y Noise: For a 8-bit converter with Vref=2V only 7.8mV of noise injection is required to introduce an error of 1LSB. The problem can be reduced by proper layout (Shielding, Differential clocks, p p power supplies, pp and symmetrical y layout) y ) Separate • Bubble Error Removal: Comparator metastability may introduce wrong thermometer code ( a single 1 or 0 in between opposite values) • Flashback: Caused by y latched comparators. p When the comparator p is switched from track to latch mode a charge glitch is introduced at the input. The problem is reduced by using a preamplifier and input impedance g matching Two-Step (Subranging) A/D Converters (13.5) V Vin 4-bit MSB A/D 4-bit 4 bit D/A V 1 in V q 16 Gain amp First 4 bits b1, b 2, b3, b4 4-bit LSB A/D Lower 4 bits b5, b6, b7 , b8 • Popular choice for high-speed medium accuracy converters (8-10 b) • Less L area and d power consumption i than h a Fl Flash h ADC • The MSB’s are converted during the first step. In the next step the remaining error is converted into the LSB’s • Speed is limited by the Gain Amplifier • Requires N-bit accuracy for all components (May be relaxed by using Digital Error Correction) Digital Error Correction for two-step A/D S/H2 (8-bit accurate) Vin S/H1 4-bit MSB A/D V in 4-bit D/A (8-bit accurate) V 1 V q Gain amp 8 (8-bit accurate) S/H3 (5-bit accurate) (4-bit accurate) 5 bits Digital delay D Error correction 4 bits 5-bit LSB A/D (5-bit accurate) 8 bits • The Th accuracy requirements i on the h iinput ADC iis relaxed due to the error corr.. 4-bit for MSb converter ( t 8-bit). (not 8 bit) Pipelined ADCs (13.5) Once the first stage has completed it’s work it immediately starts working on the next sample • Small area N – 1-bit shift register b1 V in QN DN b2 Q N- 1 D N -2 Q N -1 D N -2 b N– Q1 D1 Q1 D1 Q1 D1 1-b it D APR X 1 -b it DA P R X 1-b it D A P RX 1 bN 1 -b it DA P R X (D A P RX - d ig ita l ap p rox im a to r) A n a lo g p ip e lin e bi V i– 1 S /H Cm p – V re f/4 V re f/4 2 Vi Pipelined ADC -example Time-Interleaved A/D-converter (13.9) f1 S/H N-bit A/D f2 f0 V in S/H S/H N-bit A/D f3 S/H Dig. mux Digital g output N-bit A/D f4 S/H • • • • N-bit A/D Very high speed (figure to the right from “Allen & Holberg”) f0 is four timer higher than f1 – f4, which in addition is slightly delayed Only the S/H and the MUX must run on the highest frequency Tones are introduced at multiples of f0/N Time-Interleaved – best compromise between complexity and sampling rate – may be used for different architectures [Elbjornsson ’05] Dynamic range • Dynamic range is defined as the power of the maximum i iinputt signal i l range di divided id d b by th the ttotal t l power of the quantization noise and distortion • Often referred to as Signal-to-Noise-andDistortion range • S/(N+D) • SINAD Analog and digital supply voltages are reduced as technology scales Some ADC trends: • Li Limited it d d dynamic i range att low supply voltages remains the utmost challenge for highresolution Nyquist converters. • Oversampling converters will dominate this arena in the future • Linearity correction with digital correction is b becoming i prevalent l t 10. mars 2010 40 Nyquist ADCs at ISSCC; FOM, Effective Number of Bits 10. mars 2010 • FOM: Figure of Merit • High-resolution conv.: FOM minimum at about 10-17J/step • 6-bit ADCs : FOM about 4 orders d off magnitude i d worse than 14 bit converters, suggesting that there is much to be gained by designing more effecient 6-bit ADCs • Better ENOB reported for 350 nm than 250 nm, 180 nm and 130 nm • Data from ISSCC up to 41 2005. Nyquist ADCs at ISSCC; FOM, Sampling rate 10. mars 2010 • Maximum Sampling frequency (Usually faster is better) and FOM. • ISSCC 2000-2007 2000 2007 (90 nm, 130 nm, 180 nm technologies) • Small improvement in sampling frequency in going to finer technologies, g mainly y due to reduced 42 capacitance. Publication year SFDR @Nyquist [dB] ENOB @ Nyquist Nyquist update rate, [Ms/s] Power consumpt. [mW] Area [mm2] Supply voltage [V] Technology [nm] other Reference 2006 55 8.5 1000 250 3.5 1.2 130 Time interleaved Gupta et al IEEE JSSC ’06 2007 4 2500 24 0.057 1.2 130 ”Pipelined flash” Wang et al, IEEE Trans. I t M Instr. Meas. 2007 5 500 6 0.9 1.2 65 Time interleaved succ. approx Ginsburg et al IEEE JSSC ’07 2007 8 100 30 2.04 1.0 180 Switched opamp p p pipelined Wu et al, IEEE JSSC ’07 2008 10 30 22 0.7 1.8 180 pipelined Li et al, IEEE JSSC ’08 0.7 180 Delta‐sigma Chae, JSSCC Feb.09 2009 81 13 2009 27.5 4.3 2009 10 10. mars 2010 0.073 1750 2.2 0.02 1.0 90 ”folding flash” Verbruggen, JSSCC, Mar. ’09 1.2 12.2 0.354 3.3 350 Continous time sigma delta TCAS‐II, Jan. ’09 43 Sampling-time uncertainty •Variation in output voltage caused by variations in the time of sampling Consider the following input signal: Vref Vin = ---------- sin 2 f int 2 If the variation in sampling time is t , following equation must be satisfied to keep V less than 1LSB V LSB 1 --------------------------------t f V = N in ref 2 f in Additional litterature • Phillip E. Allen, Douglas Holberg: CMOS Analog Circuit Design, Holt Rinehart Winston, 1987. • Jonas Elbornsson: White paper on parallel successive approximation ADC, Mathcore Engineering AB, 2005. 2005 • R. Gregorian, G. Temes: Analog MOS Integrated Circuits for Signal Processing, Wiley, 1986 • D. M.Gingrich Lecture Notes, University of Alberta, Canada http://www.piclist.com/images/ca/ualberta/phys/www/http/~gingrich/phys395/notes/phys395.html • Walt Kester: Which ADC is right for your application? • Y. Chiu, B. Nicolic, P. R. Gray: Scaling of Analog-to-Digital Converters into Ultra-Deep-Submicron CMOS, Proceedings of Custom Integrated Circuits Conference, 2005. • Lecture Notes, Notes University of California California, Berkeley Berkeley, EE247 Analog Digital Interface Integrated Circuits, Fall 07;http://inst.eecs.berkeley.edu/~ee247/fa07/ • Lanny L. Lewyn, Trond Ytterdal, Carsten Wulff, Kenneth Martin: ”Analog Circuit Design in Nanoscale CMOS Technologies”, Proceedings of the IEEE, October 2009. • James L. McCreary, Paul R. Gray: ”All-MOS Charge Redistribution Analog-to-Digital Conversion Techniques – part 1”, IEEE Journal of Solid-State circuits, December 1975. Next Tuesdayy ((10/3-08): ) Rest of chapter 13. • Chapter 14 Oversampling Converters Analog Layout - mismatch • ”…The …The ratio between two similar components on the same integrated circuit can be controlled to better than +/- 1 %, and in many cases, to better than +/- 0.1 %. Devices specifically constructed to obtain a known constant ratio are called matched devices known, devices.” • ”Matching – the Achilles Heel of Analog” (Chris Diorio) 10. mars 2010 47 Some companies located in Norway, doing (or that have done)) full custom data converter designs: g • • • • • • • • • • Analog Concepts (Trondheim) Arctic Silicon Devices (Trondheim) Atmel Norway (Trondheim) gy Micro ((Oslo)) Energy GE Vingmed Ultrasound (Horten) Nordic Semiconductors (Trondheim, Oslo) Novelda (Oslo) Micrel (Oslo) Sintef (Trondheim, Oslo) T Texas Instruments I t t (Oslo) (O l ) 10. mars 2010 48 Metastability in FFs ( http://www.asic-world.com/tidbits/metastablity.html ) To avoid M. in comparators: Make gain high, increase current levels. 10. mars 2010 49