High-Frequency Low-Power Local Oscillator Generation

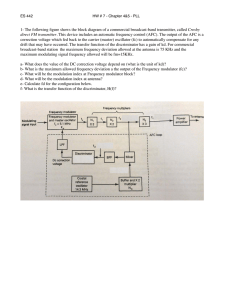

advertisement