Boston University ... SC571: VLSI Design Principles ...

advertisement

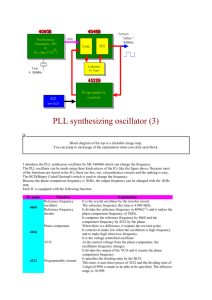

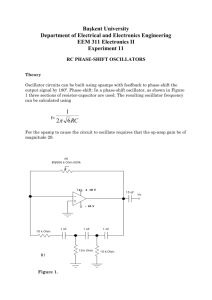

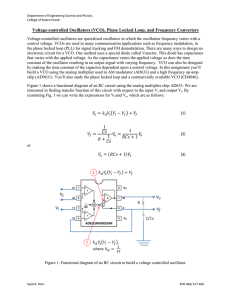

Boston University SC571: VLSI Design Principles Electrical and Computer Engineering Lab #4: Voltage Controlled Oscillator Due: 4/5/02 Lab #4 will be done using the Cadence CAD tool set installed on the machines in the VLSI Lab. You are to design, layout, and simulate an 11-stage VCO clock generator circuit. The circuit is actually a ring oscillator with additional devices on each stage for controlling the current per stage, as described in class and in Weste & Eshraghian, Chapter 5, p. 336 (see figure below). The objective will be to obtain a plot of frequency versus control voltage for the VCO. Also, obtain a plot of power versus delay for a single stage of the oscillator. Design the VCO ring oscillator in such a way as to include a transmission gate with an Enable control input that can be used to break the feedback link, say at stage 11 output, and therefore stop the oscillation when Enable is down. Also, include a second transmission gate (at the first stage) in order to reset the oscillator to a known state (call it the “0” state) with the same control signal when the oscillation is stopped. You should also design a buffer stage in order to provide an output without loading down the oscillator. Assume that the buffer stage is driving a load capacitance of 0.5 pF. Utilize TSMC’s 0.25 um CMOS process technology and models (as you did on previous labs) to build and simulate your VCO. Your lab will consist of the following tasks using various of the Cadence tools: 1. Use Composer for schematic capture. 2. Use Analog Environment to simulate the schematic. 3. Use Virtuoso to layout the VCO circuit. 4. Use DRC for design rule checking. 5. Use Extractor for SPICE model extraction based on the layout. 6. Use LVS for Logical-to-Physical checking. 7. Use Analog Environment for simulation and performance determination based on the extracted models of the actual layout. After completing the construction and simulation of the VCO and obtaining a plot of frequency versus control voltage, report the following results: 1. a plot of the oscillator frequency versus voltage, 2. maximum and minimum frequency of operation, 3. a plot of stage delay versus power (per stage) for the circuit, 4. a write-up giving a description of the circuit, its operation, and the above data. R. W. Knepper, March 20, 2002