Superlattices and Microstructures 78 (2015) 156–162

Contents lists available at ScienceDirect

Superlattices and Microstructures

journal homepage: www.elsevier.com/locate/superlattices

Performance of AlGaInP/InGaAs

enhancement/depletion-mode pseudomorphic

doping-channel field-effect transistors

Jung-Hui Tsai

Department of Electronic Engineering, National Kaohsiung Normal University, 116 Ho-ping 1st Road, Kaohsiung 802, Taiwan

a r t i c l e

i n f o

Article history:

Received 30 October 2014

Received in revised form 30 November 2014

Accepted 8 December 2014

Available online 13 December 2014

Keywords:

AlGaInP/InGaAs

Enhancement/depletion-mode

Doping-channel field-effect transistor

Logic

Noise margin

a b s t r a c t

Direct current and direct-coupled FET logic (DCFL) characteristics

of AlGaInP/InGaAs enhancement/depletion-mode pseudomorphic

doping-channel field-effect transistors (DCFETs) are demonstrated

by experimental results. After wet selectively etching process, the

enhancement-mode pseudomorphic DCFET with single doping

channel is formed. A large forward gate voltage up to +3 (2.6) V

is observed for the depletion-mode (enhancement-mode) device

for the presence of a relatively large conduction band discontinuity

at Al0.15Ga0.35In0.5P/In0.1Ga0.9As heterojunction. In the depletionmode device with double doping channels, the drain-to-source saturation voltage is only 0.5 V as the VGS is fixed at 0 V. A maximum

extrinsic transconductance of 235 (274) mS/mm and a threshold

voltage of 1.3 (+0.36) V are observed in the depletion-mode

(enhancement-mode) device. Furthermore, the noise margins

NMH and NML are of 0.108 V (0.534 V), and 0.390 V (0.417 V) at a

supply voltage of 1.5 V (2.0 V) in the DCFL application.

Ó 2014 Elsevier Ltd. All rights reserved.

1. Introduction

GaAs-based heterostructure field-effect transistors (HFETs), such as electron mobility transistors

(HEMTs) and doped-channel field effect transistors (DCFETs), have been considered to be the promising

devices in signal amplifier, microwave, gas detector, and digital integrated circuits [1–6]. As to the

E-mail address: jhtsai@nknucc.nknu.edu.tw

http://dx.doi.org/10.1016/j.spmi.2014.12.006

0749-6036/Ó 2014 Elsevier Ltd. All rights reserved.

157

J.-H. Tsai / Superlattices and Microstructures 78 (2015) 156–162

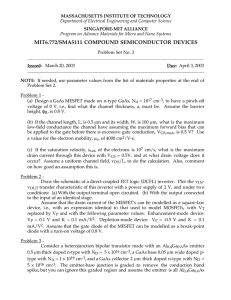

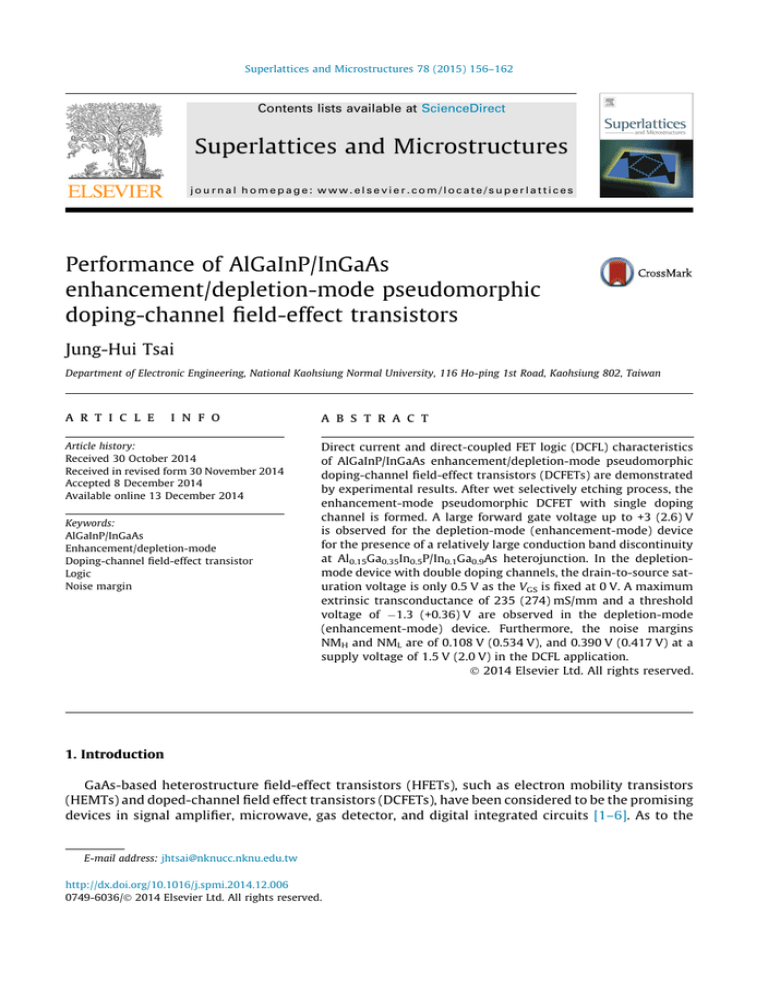

S

Depletion Mode

D

300Å n+-GaAs

Enhancement Mode

S

D

G

200 Å i-Al0.15Ga0.35In0.5P

100Å n+-In0.1Ga0.9As

G

100 Å i-Al0.15Ga0.35In0.5P

100 Å i-Al0.15Ga0.35In0.5P

+

100Å n+-In0.1Ga0.9As

100Å n -In0.1Ga0.9As

300 Å i-Al0.15Ga0.35In0.5P

300 Å i- Al0.15Ga0.35In0.5P

5000 Å i-GaAs Buffer

S.I. GaAs Substrate

Fig. 1. Schematic cross section of the AlGaInP/InGaAs pseudomorphic integrated enhancement/depletion-mode dopingchannel field-effect transistors.

HEMTs, though the maximum transconductance value may be relatively high due to the high carrier

mobility, the average transconductance was low and they suffered from small gate voltage swing

[3]. These devices were not suitable for large signal and linear circuit applications. On the other hand,

DCFETs employing an undoped (or low-doped) large energy-gap material as a Schottky barrier layer

could increase broad gate voltage swing for improving the device linearity and reducing the higher

order harmonic terms in linear amplifier applications [4,5]. As considering the carrier conduction of

GaAs-based HFETs, it is proper to replace GaAs layer with an InGaAs strain layer as an active channel

because of the lower effective electron mass, higher electron mobility, and higher peak electron velocity [3,7]. However, the In mole fraction and the thickness of InGaAs pseudomorphic layer are limited

due to the lattice mismatch with GaAs material [8].

Previously, M.O. Watanabe suggested that the conduction band discontinuity (DEc) value at

In0.5(Ga1xAlx)0.5P/GaAs heterojunction increased as the x is increased from 0 to 0.7, and its maximum

DEc value reached 0.38 eV [9]. Thus, the material system could provide good confinement effect for

electrons in channel and it will be appropriate for the fabrication of HFETs. Several HFETs based on

In0.5(Ga1xAlx)0.5P/InGaAs material system for enhancing drain current had been reported [10,11]. Furthermore, the co-integrated HFETs can provide merits in logic circuit applications. The monolithic

integration of enhancement-mode and depletion-mode FETs in the same chip can reduce the fabrication complexity by the implement of inverters [12,13]. In this article, the characteristics of

AlGaInP/InGaAs depletion/enhancement-mode pseudomorphic DCFETs are demonstrated. Attributed

to the presence of a relatively large DEc value at Al0.15Ga0.35In0.5P/In0.1Ga0.9As heterojunction, it provides a large potential barrier preventing the electron injection from channel into gate electrode.

The studied devices exhibit broad gate voltage swing in transistor characteristics, and a direct-coupled

FET logic (DCFL) characteristic at a low supply voltage is achieved.

2. Experiments

The device structure was grown on an (1 0 0) oriented semi-insulating GaAs substrate by a

low-pressure metal–organic chemical-vapor deposition system (LP-MOCVD). The epitaxial structures

consisted of a 0.5 lm undoped GaAs buffer layer, a 300 Å undoped Al0.15Ga0.35In0.5P layer, a 100 Å n+

= 2 1018 cm3 In0.1Ga0.9As lower doped-channel layer, a 100 Å undoped Al0.15Ga0.35In0.5P layer, a

158

J.-H. Tsai / Superlattices and Microstructures 78 (2015) 156–162

1.5

i- Al0.15Ga0.35In0.5P

1.0

Energy Band (eV)

0.5

Ec

0.0

G

n+-In0.1Ga0.9As

-0.5

i-GaAs

-1.0

Ev

-1.5

-2.0

0.0

0.1

0.2

0.3

0.4

Coordinate Position (μm)

(a)

1.5

i- Al0.15Ga0.35In0.5P

1.0

Energy Band (eV)

Ec

0.5

Gate

0.0

n+-In0.1Ga0.9As

i-GaAs

-0.5

Ev

-1.0

-1.5

0.0

0.1

0.2

0.3

0.4

Coordinate Position (μm)

(b)

Fig. 2. Energy-band diagrams at equilibrium for (a) depletion-mode device and (b) enhancement-mode device.

100 Å n+ = 2 1018 cm3 In0.1Ga0.9As upper doped-channel layer, a 200 Å undoped Al0.15Ga0.35In0.5P

gate layer. Finally, a 300 Å n+ = 1 1019 cm3 GaAs cap layer was deposited on the gate layer. Trimethylindium (TMI), trimethylgallium (TEG), trimethylaluminium (TMAl), phosphine (PH3), and arsine

(AsH3) were used as the In, Ga, Al, P, and As sources, respectively. The dopants used for n layers were

silane (SiH4). After the epitaxial growth, the mesa structure was used to provide the required isolation.

NH4OH:H2O2:H2O = 1:1:50 was used to selectively etch the InGaAs and GaAs layers, and Al0.15Ga0.35