Ethernet Datasheet

10/100/1000M Ethernet MAC/PCS IP

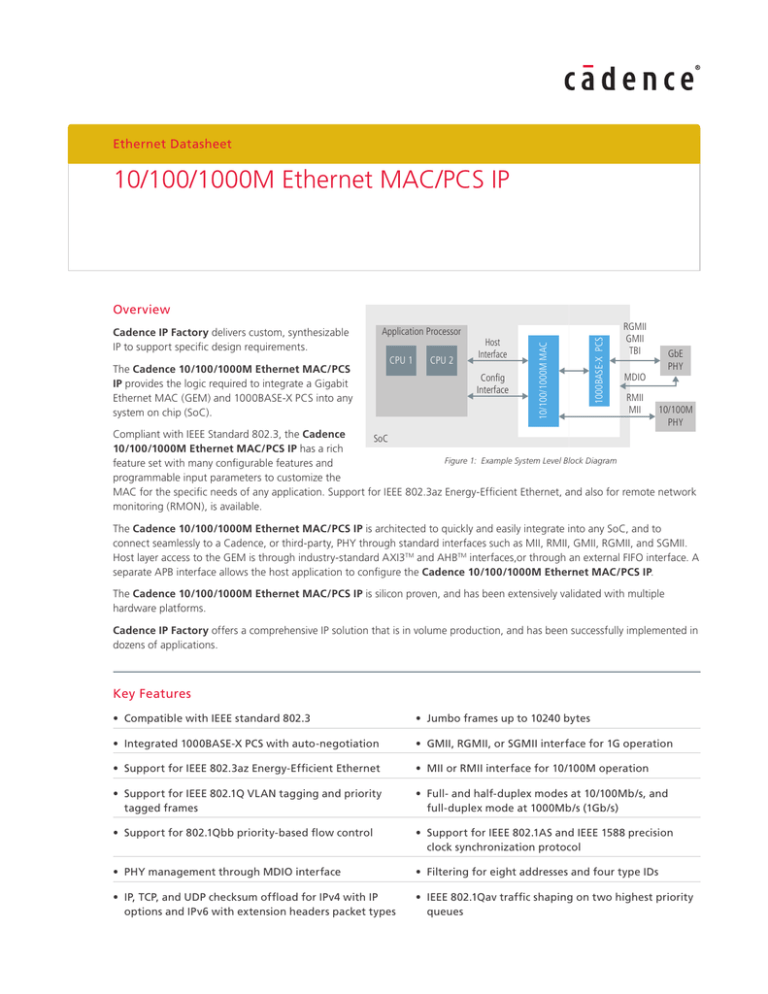

The Cadence 10/100/1000M Ethernet MAC/PCS

IP provides the logic required to integrate a Gigabit

Ethernet MAC (GEM) and 1000BASE-X PCS into any

system on chip (SoC).

Application Processor

CPU 1

CPU 2

Host

Interface

Config

Interface

1000BASE-X PCS

Cadence IP Factory delivers custom, synthesizable

IP to support specific design requirements.

10/100/1000M MAC

Overview

RGMII

GMII

TBI

GbE

PHY

MDIO

RMII

MII

10/100M

PHY

Compliant with IEEE Standard 802.3, the Cadence

SoC

10/100/1000M Ethernet MAC/PCS IP has a rich

Figure 1: Example System Level Block Diagram

feature set with many configurable features and

programmable input parameters to customize the

MAC for the specific needs of any application. Support for IEEE 802.3az Energy-Efficient Ethernet, and also for remote network

monitoring (RMON), is available.

The Cadence 10/100/1000M Ethernet MAC/PCS IP is architected to quickly and easily integrate into any SoC, and to

connect seamlessly to a Cadence, or third-party, PHY through standard interfaces such as MII, RMII, GMII, RGMII, and SGMII.

Host layer access to the GEM is through industry-standard AXI3TM and AHBTM interfaces,or through an external FIFO interface. A

separate APB interface allows the host application to configure the Cadence 10/100/1000M Ethernet MAC/PCS IP.

The Cadence 10/100/1000M Ethernet MAC/PCS IP is silicon proven, and has been extensively validated with multiple

hardware platforms.

Cadence IP Factory offers a comprehensive IP solution that is in volume production, and has been successfully implemented in

dozens of applications.

Key Features

• Compatible with IEEE standard 802.3

• Jumbo frames up to 10240 bytes

• Integrated 1000BASE-X PCS with auto-negotiation

• GMII, RGMII, or SGMII interface for 1G operation

• Support for IEEE 802.3az Energy-Efficient Ethernet

• MII or RMII interface for 10/100M operation

• Support for IEEE 802.1Q VLAN tagging and priority

tagged frames

• Full- and half-duplex modes at 10/100Mb/s, and

full-duplex mode at 1000Mb/s (1Gb/s)

• Support for 802.1Qbb priority-based flow control

• Support for IEEE 802.1AS and IEEE 1588 precision

clock synchronization protocol

• PHY management through MDIO interface

• Filtering for eight addresses and four type IDs

• IP, TCP, and UDP checksum offload for IPv4 with IP

options and IPv6 with extension headers packet types

• IEEE 802.1Qav traffic shaping on two highest priority

queues

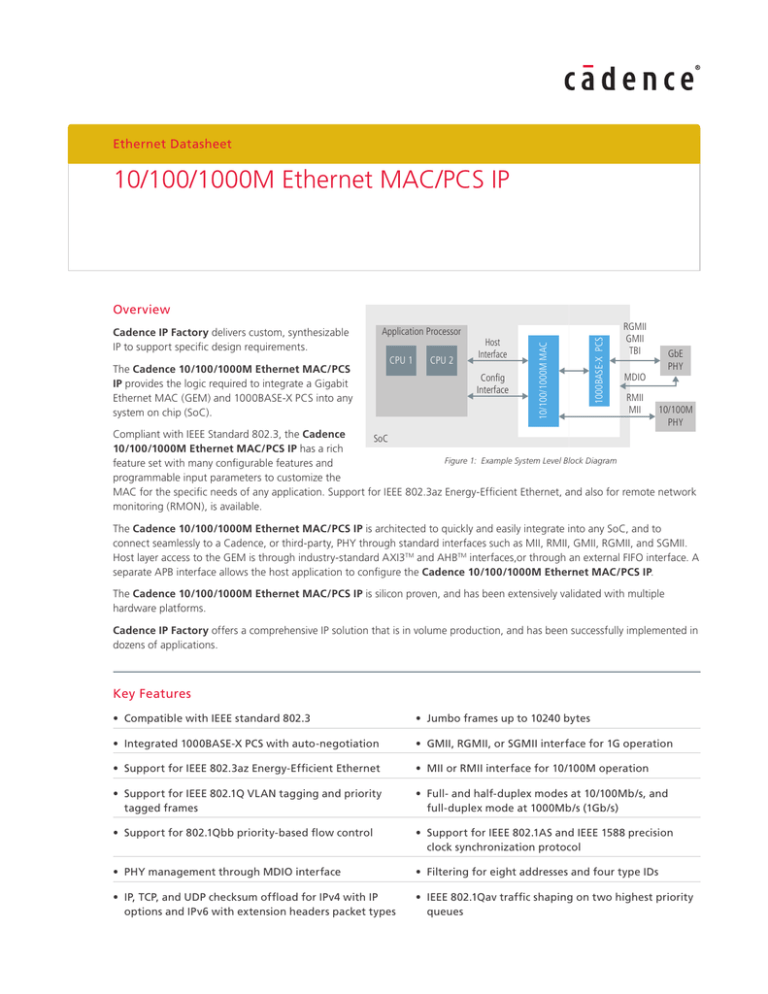

Product Details

PHY Interface

Host Interface

The Cadence 10/100/1000M Ethernet MAC/PCS IP supports

IPv4 and IPv6 protocols (with support for IP options and extension

headers)

TX

DMA Block

Gigabit Ethernet MAC (GEM)

The Cadence 10/100/1000M Ethernet MAC/PCS IP is

configurable with up to eight priority queues in both transmit and

receive paths. Flow control in full-duplex mode supports pause

frames in the receive path and hardware generated pause frames

in the transmit path.

The Cadence 10/100/1000M Ethernet MAC/PCS IP recognizes

IEEE 1588 and 802.1AS PTP frames, and has support for an

optional IEEE 1588 time stamp unit.

Integrated 1000BASE-X PCS

The Integrated 1000BASE-X PCS provides 8b10b encoding/

decoding and auto-negotiation with the link partner for

exchanging information.

RX

Config

Registers

DMA Block

TX Controller

RX Controller

GEM

TX Engine

IEEE 1588

TSU

RX Engine

MDIO

1000BASE-X PCS

The Cadence 10/100/1000M Ethernet MAC/PCS IP supports

virtual LANs by IEEE 802.1Q VLAN tagging with recognition of

incoming VLAN and priority-tagged frames. Support for IEEE

802.1Qbb priority-based flow control is also available.

The Cadence 10/100/1000M Ethernet MAC/PCS IP provides

address checking logic for 4 or 32 specific Ethernet (MAC)

addresses, four type IDs, promiscuous mode, external address

checking, hash matching of unicast and multi-cast destination

addresses and wake-on-LAN. The GEM handles IP, TCP and

UDP checksum offload on receive and transmit frames, and

padding and CRC generation for transmit frames. The Cadence

10/100/1000M Ethernet MAC/PCS IP is configurable for jumbo

frames up to 10240 bytes.

Configuration

Interface

8b/10b

Encoding

TX

Auto

Negotiation

PHY

Management

10b/8b

Decoding

RX

GMII or RGMII

MDIO

TX

PHY

Management

RX

Ten Bit Interface (TBI)

Figure 2: IP Level Block Diagram

The Cadence 10/100/1000M Ethernet MAC/PCS IP supports

all popular media independent interface (MII) options including

MII, GMII, RMMI and RGMII. PHY Interface options can be used

in any combination. An optional, integrated 1.25Gb/s SerDes can

be used to create a Serial GMII (SGMII) that works with both serial

PHYs and 1000BASE-X optical PHYs. A Quad SGMII (QSGMII)

IP is available. An MDIO interface for PHY management is also

included.

Cadence IP Factory

Cadence IP Factory can deliver various configurations of Ethernet

MACs to meet your design requirements.

For more information, visit www.cadence.com/ip

Benefits

Deliverables

• Low Risk solutions – Silicon proven design

• Verilog HDL

• Ease of Use – Customizable with easy integration

• Cadence® Encounter® RTL Compiler synthesis scripts

• Designed by an industry leader – Cadence is an active

contributor to the 802.3 standards working groups

• User guide with full programming interface, parameterization

instructions, and synthesis instructions

• Compliance tested – UNH tested

• Verilog testbench

Related Products

Available Products

• Cadence Verification IP for Ethernet

• 10/100/1000M Ethernet MAC/PCS IP

• 1000BASE-X PCS for Ethernet

• 10/100/1000M Ethernet MAC/PCS IP with DMA

®

• 10/100/1000M Ethernet MAC/PCS IP with DMA, IEEE 1588,

and AVB

Cadence Design Systems enables global electronic design innovation and plays an essential role in the

creation of today’s electronics. Customers use Cadence software, hardware, IP, and expertise to design

and verify today’s mobile, cloud, and connectivity applications. www.cadence.com

© 2013 Cadence Design Systems, Inc. All rights reserved. Cadence and the Cadence logo are registered trademarks of Cadence Design Systems,

Inc. AHB, AMBA, ARM, and AXI are trademarks and registered trademarks of ARM Ltd. All others are the properties of their respective holders.

V2.0 07/13