GPCE040A1 - Generalplus

advertisement

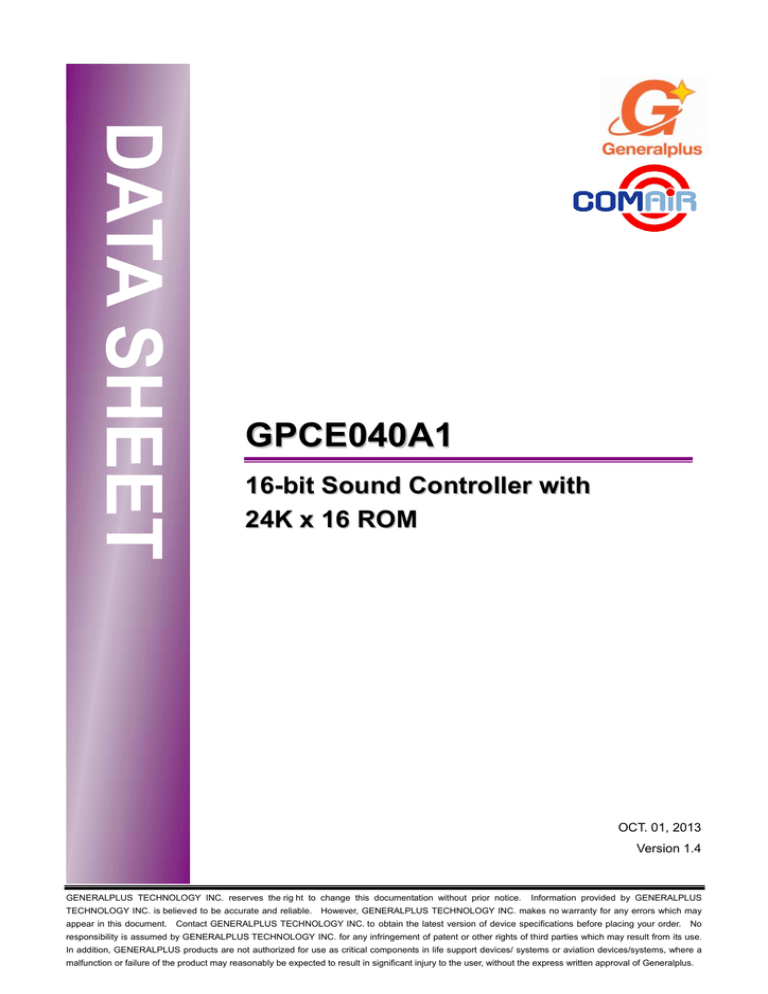

GPCE040A1 16-bit Sound Controller with 24K x 16 ROM OCT. 01, 2013 Version 1.4 GENERALPLUS TECHNOLOGY INC. reserves the rig ht to change this documentation without prior notice. TECHNOLOGY INC. is believed to be accurate and reliable. Information provided by GENERALPLUS However, GENERALPLUS TECHNOLOGY INC. makes no warranty for any errors which may appear in this document. Contact GENERALPLUS TECHNOLOGY INC. to obtain the latest version of device specifications before placing your order. No responsibility is assumed by GENERALPLUS TECHNOLOGY INC. for any infringement of patent or other rights of third parties which may result from its use. In addition, GENERALPLUS products are not authorized for use as critical components in life support devices/ systems or aviation devices/systems, where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user, without the express written approval of Generalplus. GPCE040A1 Table of Contents PAGE 1. GENERAL DESCRIPTION .......................................................................................................................................................................... 4 2. BLOCK DIAGRAM ...................................................................................................................................................................................... 4 3. FEATURES.................................................................................................................................................................................................. 4 4. APPLICATION FIELD.................................................................................................................................................................................. 4 5. SIGNAL DESCRIPTIONS............................................................................................................................................................................ 5 5.1. PAD ASSIGNMENT ................................................................................................................................................................................. 6 6. FUNCTIONAL DESCRIPTIONS.................................................................................................................................................................. 7 6.1. CPU ..................................................................................................................................................................................................... 7 6.2. MEMORY ............................................................................................................................................................................................... 7 6.2.1. SRAM........................................................................................................................................................................................ 7 6.2.2. ROM.......................................................................................................................................................................................... 7 6.3. PLL, CLOCK, POWER MODE................................................................................................................................................................... 7 6.3.1. PLL (Phase Lock Loop)............................................................................................................................................................. 7 6.4. STANDBY MODE ..................................................................................................................................................................................... 7 6.5. LOW VOLTAGE DETECTION AND LOW VOLTAGE RESET............................................................................................................................. 8 6.5.1. Low voltage detection (LVD) ..................................................................................................................................................... 8 6.5.2. Low voltage reset ...................................................................................................................................................................... 8 6.6. INTERRUPT ............................................................................................................................................................................................ 8 6.7. I/O ........................................................................................................................................................................................................ 8 6.8. TIMER/COUNTER ................................................................................................................................................................................... 9 6.8.1. Timebase ................................................................................................................................................................................ 10 6.9. SLEEP, WAKEUP AND WATCHDOG ......................................................................................................................................................... 10 6.9.1. Wakeup and sleep .................................................................................................................................................................. 10 6.9.2. Watchdog ................................................................................................................................................................................ 10 6.10. ADC (ANALOG TO DIGITAL CONVERTER) / DAC .................................................................................................................................... 10 6.11. SERIAL INTERFACE I/O (SIO).................................................................................................................................................................11 6.12. UART ..................................................................................................................................................................................................11 6.13. AUDIO ALGORITHM ................................................................................................................................................................................11 6.14. BONDING OPTION SUMMARY .................................................................................................................................................................11 6.14.1. Watchdog function...............................................................................................................................................................11 7. ELECTRICAL SPECIFICATIONS ............................................................................................................................................................. 12 7.1. ABSOLUTE MAXIMUM RATINGS ............................................................................................................................................................. 12 7.2. DC CHARACTERISTICS (VDD = 3.3V, VDDIO = 5.5V (PORTA & B), TA = 25℃) ....................................................................................... 12 7.3. DC CHARACTERISTICS (VDD = 3.3V, VDDIO = 3.3V (PORTA & B), TA = 25℃) ....................................................................................... 12 7.4. DC CHARACTERISTICS (VDD = 2.7V, VDDIO = 2.7V (PORTA & B) , TA = 25℃) ...................................................................................... 13 7.5. DC CHARACTERISTICS (VDD = 2.4V, VDDIO = 2.4V (PORTA & B) ,TA = 25℃) ....................................................................................... 13 7.6. ADC CHARACTERISTICS (VDD = 3.3V, TA = 25℃) ................................................................................................................................ 14 7.7. DAC CHARACTERISTICS (TA = 25℃) .................................................................................................................................................... 14 7.8. PULL HIGH RESISTER AND VDDIO ......................................................................................................................................................... 15 7.9. I/O OUTPUT HIGH CURRENT IOH AND VOH .............................................................................................................................................. 15 7.10. PULL LOW RESISTER AND VDDIO .......................................................................................................................................................... 15 7.11. I/O OUTPUT LOW CURRENT IOL AND VOL ............................................................................................................................................... 15 © Generalplus Technology Inc. Proprietary & Confidential 2 Oct 01, 2013 Version: 1.4 GPCE040A1 8. APPLICATION CIRCUITS ......................................................................................................................................................................... 16 8.1. APPLICATION CIRCUIT - (1) ................................................................................................................................................................... 16 8.2. APPLICATION CIRCUIT - (2) ................................................................................................................................................................... 17 8.3. APPLICATION CIRCUIT - (3) ................................................................................................................................................................... 18 8.4. APPLICATION CIRCUIT - (4) ................................................................................................................................................................... 19 8.5. APPLICATION CIRCUIT - (5) ................................................................................................................................................................... 20 8.6. APPLICATION CIRCUIT - (6) ................................................................................................................................................................... 21 9. PACKAGE/PAD LOCATIONS ................................................................................................................................................................... 22 9.1. ORDERING INFORMATION ..................................................................................................................................................................... 22 9.2. PACKAGE INFORMATION ....................................................................................................................................................................... 22 9.2.1. LQFP 80.................................................................................................................................................................................. 22 9.3. STORAGE CONDITION AND PERIOD FOR PACKAGE ................................................................................................................................. 24 9.4. RECOMMENDED SMT TEMPERATURE PROFILE...................................................................................................................................... 24 10. DISCLAIMER............................................................................................................................................................................................. 26 11. REVISION HISTORY ................................................................................................................................................................................. 27 © Generalplus Technology Inc. Proprietary & Confidential 3 Oct 01, 2013 Version: 1.4 GPCE040A1 16-BIT SOUND CONTROLLER WITH 24K X 16 ROM 1.GENERAL DESCRIPTION 3.FEATURES The GPCE040A1, a 16-bit architecture product, carries the newest 16-bit μ’nSP™ microprocessor 16-bit microprocessor, μ’nSP™ (pronounced as micro-n-SP), CPU clock: 0.32MHz - 49.152MHz developed by Sunplus Technology. Operating voltage: 3.0V - 3.6V @CPU clock = 49.152Mhz This high p rocessing speed assures the μ’nSP™ is capable of handling complex digit al signal processes easily and rapidly. applicable to the areas Operating voltage: 2.4V - 3.6V @CPU clock <=40.96Mhz IO PortA & B operating voltage: 2.4V - 5.5V Therefore, the GPCE040A1 is 24K-word fast-speed ROM of digital sound pr ocess and voice recognition. The operating volt age of 2.4V thr ough 3.6V and 2K-word working SRAM speed of 0.32MHz through 49.1 52MHz yield the GPCE040A1 to Software-based audio processing be easily used in varieties of applications. Crystal Resonator The memory capacity Standby mode (Clock Stop mode) for power savings, includes 24K-word fast-spee d ROM plus a 2 K-word working Other features include 32 prog rammable multi-functional Max. 2.0μA @ VDD = 3.6V I/Os, two 16-bit timers/counters, 32768Hz Real Time Clock, Lo w Two 16-bit timers/counters Voltage Reset/Detection, eight channels 10-bit ADC (one channel Two 10-bit DAC outputs built-in MIC amplifier w ith auto gain controller), 10-bit DAC output 32 general I/Os (bit programmable) and many others. 14 INT sources with two priority levels SRAM. Key wakeup function (IOA0 - 7) PLL feature for system clock 2.BLOCK DIAGRAM 32768Hz Real Time Clock (RTC) Eight channels 10-bit AD converter Fast-speed 16-bit SLEEP ROM u'nSP controller RESET VCOIN X32I PLL X32O RAM CPU Clock 10-bit A/D & AGC RTC LVD/LVR WATCHDOG 10-bit DAC1 Output 10-bit DAC2 Output UART IOB7 (Rx) ADC external top reference voltage 16-bit Timer/Counter x2 TimerBase INT control 2.0V voltage regulator output, 5mA of driving capability VMIC VEXTREF VADREF AGC MICOUT MICP MICN OPI Serial interface I/O (SIO) AUD1 Watchdog enable (bonding option) Built-in microphone amplifier and AGC function UART receiver and transmitter (full duplex) Low voltage reset and low voltage detection AUD2 SIO IOB10 (Tx) IOB1 (SDA) IOB0 (SCK) 32 PIN GENERAL I/O PORT IOA15 - 0 4.APPLICATION FIELD Voice recognition products IOB15 - 0 Intelligent interactive talking toys Advanced educational toys Kids learning products Kids storybook General speech synthesizer Long duration audio products Recording / playback products © Generalplus Technology Inc. Proprietary & Confidential 4 Oct 01, 2013 Version: 1.4 GPCE040A1 5.SIGNAL DESCRIPTIONS Mnemonic PIN No. Type Description IOA [15:8] 46 - 39 I/O IOA [15:8]: bi-directional I/O ports. IOA [7:0] 34 - 27 I/O IOA [7:0] can be software programmed to wakeup I/O pins. IOA [6:0] can be optioned as ADC Line-in input. IOB [15:11] 50 - 54 I/O IOB [15:11]: bi-directional I/O ports. IOB 10 57 I/O IOB10 can also be selected as UART Transmitter (Tx). IOB 9 58 I/O IOB9 can also be Multi-duty cycle output of TimerB (BPWMO). IOB 8 59 I/O IOB8 can also be Multi-duty cycle output of TimerA (APWMO). IOB 7 60 I/O IOB7 can also be selected as UART receiver (Rx). IOB 6 61 I/O IOB6 is a bi-directional I/O ports. IOB 5 62 I/O IOB5 can also be selected as feedback signal with EXT2. IOB 4 63 I/O IOB4 can also be selected as feedback signal with EXT1. IOB 3 64 I/O IOB3 can also be selected as an external interrupt input pin (EXT2)(Negative-edge Triggered). IOB 2 65 I/O IOB2 can also be selected as an external interrupt input pin (EXT1)(Negative-edge Triggered). IOB 1 66 I/O IOB1 can also be selected as a serial interface data (SDA). IOB 0 67 I/O IOB0 can also be selected as a serial interface clock (SCK). DAC1 12 O Audio DAC1 output. DAC2 13 O Audio DAC2 output. X32I 2 I Oscillator Crystal input. X32O 1 O Oscillator Crystal output. VCOIN 70 I RC filter connection for PLL. AGC 16 I AGC control pin. MICN 19 I Microphone differential input (negative). MICP 21 I Microphone differential input (positive). V2VREF 14 O 2.0V output volt age, 5.0mA of driving capability (can be used as ex ternal ADC Line_IN top reference voltage). st MICOUT 18 O Microphone 1 amplifier output. OPI 17 I Microphone 2 amplifier input. VEXTREF 23 I ADC Line_IN top external reference voltage input pin. VMIC 25 O Microphone power supply. VADREF 22 O AD reference voltage (generated by internal AD converter). VDD 5, 69 I Positive supply for logic. VSS nd 8, 10, 26, 71 I Ground reference for logic and I/O pins. VDDIO 37, 38, 56 I Positive supply for I/O pins. VSSIO 35, 36, 48 I Ground reference for I/O pins. AVDD 24 I Positive supply for analog circuit including ADC, DAC and 2.0V regulator. AVSS 15 I Ground reference for analog circuit including ADC, DAC and 2.0V regulator. RESET 68 I An active low reset to the chip. SLEEP 49 O Sleep mode (active high). TEST 3 I Connected to high for test mode, normally connected to GND (test mode disabled) or unconnected. 7, 9, 11, 20, I Not used. N/C 47, 55 N/C 4 I Do NOT bonding and connect this pin, if user binding this pin, IC will not work. WDGOPT* 6 I Bonded for watchdog disabled, unbonded for watchdog enabled. Note*: WDGOPT is the watchdog option pin, selected by bonding option. Remain WDGOPT unbonded to enable the watchdog. In VDD contrast, bonding to pad will disable watchdog. The reason of placing WDTOPT adjacent to VDD is to facilitate connection between VDD and WDGOPT when disabling watchdog is necessary. The layout of WDOGPT option pin is drawn in the right. © Generalplus Technology Inc. Proprietary & Confidential WDGOPT 5 Oct 01, 2013 Version: 1.4 GPCE040A1 VSS VCOIN VDD RESET IOB0 IOB1 IOB2 IOB3 IOB4 IOB5 IOB6 IOB7 IOB8 IOB9 IOB10 VDDIO N/C 5.1. PAD Assignment 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 X32O 1 X32I 2 54 IOB11 TEST 3 53 IOB12 N/C 4 52 IOB13 VDD 5 WDGOPT 6 51 IOB14 N/C 7 50 IOB15 VSS 8 49 SLEEP N/C 9 48 VSSIO VSS 10 N/C 47 N/C 11 DAC1 12 46 IOA15 DAC2 13 45 IOA14 V2VREF 14 44 IOA13 AVSS 15 AGC 43 IOA12 16 OPI 17 42 IOA11 MICOUT 18 41 IOA10 MICN 19 40 IOA9 N/C 20 31 32 33 34 35 36 37 38 39 VSSIO VSSIO VDDIO VDDIO IOA8 30 IOA7 VMIC 29 IOA6 AVDD 28 IOA5 VEXTREF 27 IOA4 VADREF 26 IOA3 25 IOA2 24 IOA1 23 IOA0 22 VSS 21 MICP (0,0) This IC substrate should be connected to VSS Note1: To ensure the IC functions properly, please bond all of VDD and VSS pins. Note2: The 0.1μF capacitor between VDD and VSS should be placed to IC as closed as possible. © Generalplus Technology Inc. Proprietary & Confidential 6 Oct 01, 2013 Version: 1.4 GPCE040A1 6.FUNCTIONAL DESCRIPTIONS 6.1. CPU The GPCE040A1 is equipped w ith a 16-bit μ’nSP™, the new est Moreover, a hi gh performance hardware multiplier with the 16-bit capability of FI R filter is also microprocessor by SUNPLUS and p ronounced as micro-n-SP. Eight registers ar e involved in μ’nSP™: R1 - R 4 built in to reduce the sof tware multiplication loading. (General-purpose registers), PC (Program Counter), SP (Stack Pointer), Base Pointer (BP) an d SR (Segment Register). The 6.2. Memory interrupts include three FIQs (Fast Interrupt Request) and eight 6.2.1. SRAM IRQs (Interrupt Request), plus one software-interrupt, BREAK. The amount of SRAM is 2K- word (including Stack), ranged from $0000 through $07FF with access speed of two CPU clock cycles. Phase Lock Loop 32768Hz X'tal PLL OUT 24.576MHz(default) 20.48MHz 32.768MHz 40.96MHz 49.152MHz System Clock generator b7 b6 Fosc/n FOSC (PLL) CPU Clock n:1,2,4,8,16,32,64 (Default : Fosc/8) b2 b1 b0 b5 b7,b6,b5 of P_SystemClock(W)($7013H) of P_SystemClock(W)($7013H) System clock frequency selection CPU clock frequency selection 6.2.2. ROM The GPCE040A1 provides a 24K- word fast-speed ROM with generated in ever y 0.5 second s, time can be access speed of two CPU clock cycles. numbers of RTC occurrence. traced b y the In addition, GPCE040A1 supports 32768Hz oscillator in normal mode and auto-po wer-saving mode. 6.3. PLL, Clock, Power Mode In normal mode, 32768Hz OSC always runs at the highest power 6.3.1. PLL (Phase Lock Loop) consumption. In auto-po wer-saving mode, ho wever, it runs in normal mode fo r the first 7.5 The purpose of PLL is to provide a base frequency (32768Hz) and to pump the fre quency from 2 0.48MHz to 49.152 MHz for s ystem clock (Fosc). The default PLL frequency is 24.576MHz. 6.4. Standby Mode The GPCE040A also of fers a standby mode for lo w power 6.3.1.1. System clock application needs. T o enter st andby mode, th e desired key Basically, the system clock is provided b y PLL and programmed wakeup port (IOA [7:0]) must be configured to i nput first. by the Port_SystemClock (W) to determine the frequency of clock the standby mode. CPU clock is F osc/8 if not specified. The initial CPU clock is (W)) to e nter standby mode. I n such mode, SRAM and I/Os remain in the 6.3.1.2. 32768Hz RTC previous states till CPU being aw oken. The wakeup sources in GPCE040A1 include Port IOA7 - 0 and IRQ1 - The Real Time Clock (R TC) is normall y used in watch, clock or IRQ6. Af ter GPCE040A1 is a woken, the CP U will continue to A 2Hz-RTC (1/2 second) function is execute the pro gram. Progra mmer can also enable or disable The RTC counts the timing as well as to © Generalplus Technology Inc. Proprietary & Confidential After that, stop t he CPU clock by writing the ST OP CLOCK Register (b0~b2 of Port_S ystemClock clock by programming the Port_SystemClock (W). wake CPU up whenever R TC occurs. Since the R Also remember to e nable the corresponding interrupt source(s) for wakeup. Fosc/8 after system wakes up and to be adjusted to desired CPU loaded in GPCE040A1. And read the Port_IOA_Latch(R) to latch the IOA state before entering for system. The default sy stem clock Fosc = 24.576MHz and other time related products. seconds and changes back to power-saving mode automatically to save powers. the 32768Hz OSC when CPU is in standby mode. TC is 7 Oct 01, 2013 Version: 1.4 GPCE040A1 6.5. Low Voltage Detection and Low Voltage Reset Interrupt Source Interrupt Name Priority 6.5.1. Low voltage detection (LVD) EXT2 IRQ3_EXT2 Low The Low Voltage Detection (L VD) reports the circumstance of EXT1 IRQ3_EXT1 Low Key change wakeup IRQ3_KEY Low 4096Hz IRQ4_4KHz Low 2048Hz IRQ4_2KHZ Low 1024Hz IRQ4_1KHz Low 4Hz IRQ5_4Hz Low 2Hz IRQ5_2Hz Low Time-base 1 IRQ6_TMB1 Low Time-base 2 IRQ6_TMB2 Low UART (TxRDY or RxRDY) UART IRQ Low present voltage. There are three LVD levels to be selected: 2.5V, 2.9V, and 3.3 V. These levels can be Port_LVD_Ctrl (W). 2.9V. programmed via As an exa mple, suppose L VD is given to When the volt age drops below 2.9V, the b15 of Port_LVD_Ctrl is read as HIGH. In such st ate, program can be designed to react to this condition. 6.5.2. Low voltage reset In addition to the LVD, the GPCE040A1 has a nother important function, Low Voltage Reset (LVR). With t he LVR function, a reset signal is generated to reset system when the operating 6.7. I/O voltage drops below 2.3V for 1 0 consecutive CPU clock cy cles. Two I/O ports are built in GP CE040A1, PortA and PortB. Without LVR, the CPU becomes unstable and malfunctions w hen the operating voltage drops below 2.3V. The LVR will reset all In addition to the regular IO functi on, the PortB can also perform functions to the initial operational (stable) states when the voltage drops below 2.3V. The PortA is an ordinary I/O with programmable wakeup capability. some special functions in cert A LVR timing diagram is given as follows: ain pins. Sup pose operating voltage is running at 3. 6V (VDD) and VDDIO (power for I/O) operates from 3.6V (VDD) to 5.5V. In such condition, the I/O pad is capable of operating from 0V through VDDI O. FCPU The following diagram is an I/O schematic. VDD 2.3V Tw Buffer(R) Tvdd Port_Data(W) RESET Register Port_Buffer(W) Treset Tw=FCPU x 10 cycle Tvdd > Tw Treset = FCPU x512 cycle pull high Pin pad Control logic Port_DIR(R/W) pull low Port_ATTR(R/W) 6.6. Interrupt Data(R) The GPCE040A1 has 14 interrupt sources, grouped into two types, FIQ (Fast Interrupt Request) an d IRQ (Inte rrupt request). The priority of FIQ is higher than IRQ. FIQ is the high-priority interrupt while IRQ is the low-priority one. An IRQ can be interrupted by a FIQ, but not by another IRQ. Although data can be written into the same r egister through Port_Data and Port_Buffer, they can be read from different places, A FIQ cannot be interrupted by any Buffer (R) and Data (R). other interrupt sources. The IOA [7:0] is the key wakeup port. To activate key wakeup function, latch data on PORT_IOA_Latch and enable the ke y wakeup function. Wakeup is triggered when Interrupt Source Interrupt Name Priority Fosc/1024 FIQ_PWM/IRQ0_PWM High(FIQ) an ordinary I/O port, PortB car ries some special functions. summary of PortB special functions is listed as follows: Timer A FIQ_TMA/ IRQ1_TMA High(FIQ) Timer B FIQ_TMB/ IRQ2_TMB High(FIQ) © Generalplus Technology Inc. Proprietary & Confidential the PortA state is different from at the time latched. 8 In addition to A Oct 01, 2013 Version: 1.4 GPCE040A1 Special function in PortB PortB Special Function IOB0 SCK Serial interface clock Refer to see SIO section IOB1 SDA Serial interface data Refer to see SIO section IOB2 EXT1 External interrupt source 1(Negative-edge Triggered) IOB2 set as input mode Works with IOB4 by adding a RC circuit bet ween IOB2 set as inverted output Feedback Output1 Function Description Note them to get an OSC to EXT1 interrupt IOB3 EXT2 Feedback Output2 External interrupt source 2(Negative-edge Triggered) IOB3 set as input mode Works with IOB5 by adding a RC circuit bet ween IOB3 set as inverted output them to get an OSC to EXT2 interrupt IOB4 Feedback Input1 - - IOB5 Feedback Input2 - - IOB7 Rx UART Receiver Refer to see UART section IOB8 APWMO TimerA PWM output Refer to Timer/Counter section IOB9 BPWMO TimerB PWM output Refer to Timer/Counter section IOB10 Tx UART Transmitter Refer to UART section Default state: Pull Low PWM: Pulse Width Modulation Refer to the abo ve table, the co nfiguration of IOB2, IOB3, IOB4, Initially, write a value of N into a timer and select a desired clock and IOB5 involves feedback fun ction in which an OSC frequency source, timer will start counting from N, N+1, N+2... through FFFF. can be obtained from EXT1 (EXT2) by simply adding a RC circuit An INT (TimerA/TimerB) signal is generated at the next clock after between IOB2 (IOB3) and IOB4 (IOB5). reaching “FFFF” and the INT signal is transmitted to INT controller for further processing. At the same time, N will be reloaded into 6.8. Timer/Counter timer and st art all over again. The GPCE040A1 provides two 16-bit timers/counters, TimerA and frequency source and clock sour ce B is a lo w frequency source. TimerB. The combination of clock source The TimerA is called a universal counter. general-purpose counter. TimerB is a speeds to TimerA. The clock source of TimerA comes from the combination of clock s ource A and clock source B. The clock source A is a high A and B provid es a variety of A “1” represent s pass signal and not gating. In contrast, “0” indicates deactivating timer. In The EXT1 and EXT2 When timer are the e xternal clock sources. Moreover, counter can generat e overflows, an INT signal is sent to CPU to gen erate a time-out time-out signal f or input clock sour ce to a four bits (16 levels) signal. PWM pulse w idth counter. A variety of clock duration can be TimerB, the clock source is give n from source C. generated and exported from IOB8 (APW MO) and IOB9 Clock of Source A Clock of Source B Clock of Source C Fosc/2 2048Hz Fosc/2 Fosc/256 1024Hz Fosc/256 32768Hz 256Hz 32768Hz 8192Hz TMB1 8192Hz 4096Hz 4Hz 4096Hz 1 2Hz 1 0 1 0 EXT1 EXT2 EXT1 © Generalplus Technology Inc. Proprietary & Confidential (BPWMO). The following example is a 3/1 6-duration cycle. The APWM O waveform is made by selecting Port_TimerA_Ctrl (W) [9:6]. As a pulse width through a r esult, each 16 cy cles will generate a pulse width defined in control port. These PWM signals can be a pplied for controlling the speed of motor or other devices. 9 Oct 01, 2013 Version: 1.4 GPCE040A1 TimerA_Timeout Tapwmo Tduty APWMO Generally speaking, the clock source A sources and source B comes from R and C are fast cloc 6.9.2. Watchdog k TC system (32768Hz). The purpose of watchdog is to monitor if the sy Therefore, clock source B can be utilized as a precise counter for normally. time counting, e.g., the 2Hz cl watchdog is not cleared, CPU ock can be use d for real time counting. stem operates Within a certain period, watchdog must be cleared. If assumes the program has been running in an abnormal condition. As a result, the CPU will reset the system to th e initial st ate and start running t he program all 6.8.1. Timebase over again. The watchdog func tion can be rem oved by bonding Timebase, generated by 32768Hz, is a combination of frequenc y option. In GPCE040A1, the clear pe riod is 0.7 5 seconds. If selections. The outputs of timebase block are named to TMB1 watchdog is cleared within each 0.75 seconds, the system will not and TMB2. be reset. TMB1 is frequen cy for TimerA (Clock source B) . To clear watchdog, simply write “xxxx xxxx xxxx xx01B” The TMB1 and TMB2 are th e sources for I nterrupt (IRQ6). to Furthermore, timebases generates additional 2Hz to 40 96Hz Port_Watchdog_Clear (W) fo r watchdog clearance must be interrupt sources (IRQ4 and IRQ5) for Real-Time-Clock (RTC). exactly the same as the one illustr ated above (xxxx xxxx xxxx Port_Watchdog_Clear(W). The content written to xx01B). Othe r values given to the Port_Watchdog_Clear (W) for watchdog clearance ma y end up w ith system reset. The TMB2 TMB1 128Hz 8Hz watchdog function remains ena bled during st andby mode if the 256Hz 16Hz 32768Hz is turned on. 512Hz 32Hz 1024Hz 64Hz Default: 128Hz Default: 8Hz 6.10. ADC (Analog to Digital Converter) / DAC The GPCE040A1 has eight channels 10-bit ADC (Analog to Digital Converter). digital signal, e.g. a volt age level into a digit al word. 6.9. Sleep, Wakeup and Watchdog The eight channels of ADC can be se ven channels of line-in from IOA [6:0] 6.9.1. Wakeup and sleep or one channel microphone (MIC) input through amplifier and AGC 1) Sleep: After power-on reset, IC starts running until a sleep command occurs. When a sleep comma controller. nd is The MIC amplifier circuit is cap able of red ucing common mode noise by transmitting signals through differential accepted, IC will turn the system clock (PLL) off. After MIC Inputs (MICN, MICP). all, it enters sleep mode. Moreover, an external resistor can be applied to adjus t microphone gain and time of AGC operating. The AD needs to select source of line-in before conversion. 2) Wakeup: CPU waking up from sleep mode r equires a w akeup signal to turn the sy stem clock (PLL) on. ADC is able to choose the exte The IRQ rnal or intern al (= AVDD) top GPCE040A1 offers a const ant voltage 2.0V with 5.0mA driving wakeup and interrupt sources (IRQ1 - IRQ6) can be used for w The reference voltage. If const ant voltage source is unavailab le, signal makes C PU to complete the wakeup proc ess and initialization. The key The function of an ADC is to convert analog signal to ability with a capacitor connected. akeup sources. The GPCE040A1 has two 10-bit D/A with 2.0mA or 3.0mA driving current for audio outputs, DAC1 and DAC2. © Generalplus Technology Inc. Proprietary & Confidential 10 Oct 01, 2013 Version: 1.4 GPCE040A1 6.11. Serial interface I/O (SIO) Serial interface I/O of fers a one-bit serial interface f or receiving data via two I/O pins, IOB0 (SCK) and IOB1 (SDA). communication. This serial interface is capable of transmitting or WRITE MODE write control bit=0 SCK SDA Ax+1 SDA Ax Ax-1 A0 Dx+1 Dx D0 Dx+1 Dx D0 STOP 1st write P_SIO_Data (W), $701AH 2nd write P_SIO_Data (W), $701AH READ MODE read control bit = 1 SCK SDA Ax+1 SDA Ax Ax-1 A0 Dx+1 Dx D0 Dx+1 Dx D0 STOP 1st Read P_SIO_Data (R), $701AH 2nd Read P_SIO_DAta (R), $701AH 6.12. UART UART block pr ovides a full-duplex st andard interface t hat facilitates the c ommunication with other devi ces. interface, GPCE can transmit and receive simult aneously. maximum baud-rate can be up to 1 15200bps. D0 D1 D2 1-bit Start When GPCE040A1 receives and/or tra nsmits a frame of data, the b 7 The (RxRDY) and/or b6 (TxRDY) in Port_UART_Command2(R) will be This function can be accomplished by using PortB and Interrupt (UART IRQ). start bit Rx and Tx of UART are shared with IOB7 and IOB10. With this set to “1” and the UART IRQ is activated at the same time. The D3 D4 8-bit data D5 D6 D7 parity bit stop bit can be enabled/disable; also even/odd check 6.13. Audio Algorithm 1-bit Stop 6.14.1. Watchdog function The following speech types can be used in GPCE040A: PCM, WDGOPT is th e optional pin f or watchdog b y bonding option. SACM_S200, The shape looks as the figure given below . SACM_S480, SACM_S530, SACM_S720, When watchdog is SACM_A1600, SACM_A1601, SACM_A3600, SACM_DVR520, selected, WDGOPT is unbonde d. If w atchdog is not sele cted, SACM_DVR1600, SACM_DVR3200, and SACM _DVR4800. WDGOPT is bonded. For The reason for WDGOPT adjacent to VDD melody synthesis, the GPCE040 A1 supports SACM_MS01 (FM ) is that w hen watchdog is not selected, it is easy and SACM_MS02 (wave-table) synthesizers. connection between VDD and WDGOPT. 6.14. Bonding Option Summary to make the VDD The GPCE040A has the following bonding option: WDGOPT © Generalplus Technology Inc. Proprietary & Confidential 11 Oct 01, 2013 Version: 1.4 GPCE040A1 7.ELECTRICAL SPECIFICATIONS 7.1. Absolute Maximum Ratings Characteristics Symbol Ratings DC Supply Voltage V+ < 4.0V PortA/B Pad Supply Voltage VIO < 7.0V Input Voltage Range VIN -0.5V to V+ + 0.5V Operating Temperature TA 0℃ to +60℃ TSTO -50℃ to +150℃ Storage Temperature Note: Stresses beyond those given in the Absolute Maximum Rating table may cause operational errors or damage to the device. For normal operational conditions see DC Electrical Characteristics. 7.2. DC Characteristics (VDD = 3.3V, VDDIO = 5.5V (PortA & B), TA = 25℃) Characteristics Symbol Limit Min. Typ. Max. Unit Test Condition Operating Voltage VDD 2.4 3.3 3.6 V Operating Current IOP - 26 - mA Standby Current ISTB - - 2.0 μA Disable 32KHz crystal Input High Level VIH 0.7VDDIO - - V - Input Low Level VIL - - 0.3VDDIO V Output High Current IOH - -5.0 - mA VOH = 4.0V Output Low Current IOL - 12 - mA VOL = 1.0V RPL - 80 - KΩ VIN = VDDIO RPH - 125 - KΩ VIN = VSS Input Pull-Low Resister (PA15:0, PB15:0) Input Pull-High Resister (PA15:0, PB15:0) FOSC = 49.152MHz, AD, DAC disable, no loading - 7.3. DC Characteristics (VDD = 3.3V, VDDIO = 3.3V (PortA & B), TA = 25℃) Characteristics Symbol Limit Min. Typ. Max. Unit Test Condition Operating Voltage VDD 2.4 3.3 3.6 V Operating Current IOP - 26 - mA Standby Current ISTB - - 2.0 μA Disable 32KHz crystal Input High Level VIH 0.7VDDIO - - V - Input Low Level VIL - - 0.3VDDIO V - Output High Current IOH - -2.9 - mA VOH = 2.6V Output Low Current IOL - 6.7 - mA VOL = 0.7V RPL - 143 - KΩ VIN = VDDIO RPH - 199 - KΩ VIN = VSS Input Pull-Low Resister (PA15:0, PB15:0) Input Pull-High Resister (PA15:0, PB15:0) © Generalplus Technology Inc. Proprietary & Confidential 12 FOSC = 49.152MHz, AD, DAC disable, no loading Oct 01, 2013 Version: 1.4 GPCE040A1 7.4. DC Characteristics (VDD = 2.7V, VDDIO = 2.7V (PortA & B) , TA = 25℃) Characteristics Symbol Limit Min. Typ. Max. Unit Test Condition Operating Voltage VDD 2.4 2.7 3.6 V Operating Current IOP - 19 - mA Standby Current ISTB - - 2.0 μA Disable 32KHz crystal Input High Level VIH 0.7VDDIO - - V - Input Low Level VIL - - 0.3VDDIO V Output High Current IOH - -1.9 - mA VOH = 2.1V Output Low Current IOL - 4.4 - mA VOL = 0.5V RPL - 188 - KΩ VIN = VDDIO RPH - 263 - KΩ VIN = VSS Input Pull-Low Resister (PA15:0, PB15:0) Input Pull-High Resister (PA15:0, PB15:0) FOSC = 49.152MHz, AD, DAC disable, no loading - 7.5. DC Characteristics (VDD = 2.4V, VDDIO = 2.4V (PortA & B) ,TA = 25℃) Characteristics Symbol Limit Min. Typ. Max. Unit Test Condition Operating Voltage VDD 2.4 2.4 3.6 V Operating Current IOP - 16 - mA Standby Current ISTB - - 2.0 μA Input High Level VIH 0.7VDDIO - - V - Input Low Level VIL - - 0.3VDDIO V - Output High Current IOH - -1.5 - mA VOH = 1.92V Output Low Current IOL - 3.5 - mA VOL = 0.48V RPL - 227 - KΩ VIN = VDDIO RPH - 322 - KΩ VIN = VSS Input Pull-Low Resister (PA15:0, PB15:0) Input Pull-High Resister (PA15:0, PB15:0) © Generalplus Technology Inc. Proprietary & Confidential 13 FOSC = 49.152MHz, AD, DAC disable, no loading Disable 32KHz crystal Oct 01, 2013 Version: 1.4 GPCE040A1 7.6. ADC Characteristics (VDD = 3.3V, TA = 25℃) Characteristics Unit Symbol Min. Typ. Max. Unit ADC Power Dissipation for LINE_IN IADC - 1.0 - mA ADC Power Dissipation For MIC_IN - - 1.9 - mA VINL (Note 1) VSS-0.3 - VDD+0.3 V ADC LINE_IN Input Voltage Range from IOA[6:0] ADC Microphone Input Voltage Range External ADC Top Voltage VINM VSS-0.3 - VDD+0.3 V VEXTREF (Note 2) 2.0 - VDD+0.3 V RESO - - 10 bits SINAD (Note 4) - 56 - dB ENOB (Note 5) 8.0 9.0 - bits Resolution of ADC Signal-to-Noise Plus Distortion of ADC from Line In Effective Number of Bit INL - ±4.0 - LSB (Note 3) DNL (Note 6) - ±0.5 - LSB AD Conversion Rate FCONV - - Fcpu/512 Hz Microphone Amplifier Gain (Note 7) A MIC - - 42 dB Integral Non-Linearity of ADC Differential Non-Linearity of ADC Note1: Internal protection diodes clamp the analog input to VDD and VSS. These diodes allow the analog input to swing from (VSS-0.3V) to (VDD+0.3V) without causing damages to the devices. Note2: The ADC performance is limited by the system noise level and therefore, the GPCE040A1 only guarantees to the 8-bi t accuracy when VEXTREF is 2.0V. Note3: The LSB means Least Significant Bit. VINL = 2.0V, 1LSB = 2.0V/2^10 = 1.953mV. Note4: The SINAD testing condition at VINLp-p = 0.8*VDD, FCONV = Fcpu/512 = 49MHz/512 = 95KHz, Fin=1.0KHz Sine waves at VDD = 3.0V from the IOA [6:0] input. Note5: ENOB = (SINAD-1.76)/6.02. Note6: The ADC of GPCE040A1 guarantees no data missed during conversion. Note7: The microphone amplifier maximum gain = 15 * (60K/(1.5K+REXT) V/V. The REXT is external resistor between OPI and MICOUT. The gain is 132V/V (=42dB) when REXT is 5.1K. 7.7. DAC Characteristics (TA = 25℃) Characteristics Test condition Symbol Unit Min. Typ. Max. Unit DAC resolution VDD = 3.3V RESO - - 10 bit Signal to Noise Ratio of DAC VDD = 3.3V SNR - 54 - dB Sample Rate VDD = 3.3V FS - - 100K Hz - 2.0 - - 3.0 - Output DAC current VDD = 3.3V (2.0mA mode) (AUD1, AUD2) VDD = 3.3V (3.0mA mode) © Generalplus Technology Inc. Proprietary & Confidential IAUD 14 mA Oct 01, 2013 Version: 1.4 GPCE040A1 7.8. Pull High Resister and VDDIO 7.10. Pull Low Resister and VDDIO 300 RPL(Kohms) RPH(Kohms) 500 400 300 200 200 100 100 0 2.4 3.4 0 4.4 2.4 3.4 VDDIO(V) 4.4 VDDIO(V) 7.9. I/O Output High Current IOH and VOH 7.11. I/O Output Low Current IOL and VOL IOL(mA) IOH (mA) 15 10 5 0 20 10 0 0.5 1.5 2.5 3.5 4.5 VOH (V) © Generalplus Technology Inc. Proprietary & Confidential 0.5 1.5 2.5 3.5 4.5 V OL(V) 15 Oct 01, 2013 Version: 1.4 GPCE040A1 8.APPLICATION CIRCUITS 8.1. Application Circuit - (1) VDDH(5V) 100 μ Speaker1 VDDH(5V) 100 μ Speaker2 VDDH(5V) 2 0.1μ 1 2 3 8 7 6 6 8 7 0.22 μ 5 4 4 5 0.1 μ 1K 1K 100μ VDDH(5V) IOB[15:0] IOA[15:7] 0.22μ 0.1μ GPY0030A 0.1μ 1 2 3 3 100μ AVDD (3.3V) 0.1 μ GPY0030A GPY0029A 1 VDD (3.3V) 100μ VDD 1K 1K RESET 4.7K 0.1μ 0.1μ 0.1μ 0.1μ 0.1μ 20-50pF* RESET DAC1 DAC2 IOA[15:7] IOB[15:0] VDDIO VSSIO AVDD AVSS VDD VSS X32I 32768Hz X32O GPCE040A1 20-50pF* VCOIN VMIC MICP MICN MICOUT OPI AGC VADREF VEXTREF V2VREF IOA[6:0] 3300p 3.3K 1K 0.22 μ 0.22 μ 0.22 μ 5.1K 0.1 μ 3K MIC 470K 3K 4.7 μ 47 μ 5000p 0.1 μ IOA[6:0] GPCE040A1 Application Circuit (MIC_IN and with GPY0030A audio amplifier, for 3-battery use only) 220 μ Oct 01, 2013 Version: 1.4 16 © Generalplus Technology Inc. Proprietary & Confidential Different capacitor values may be required for different crystal/resonator used. Note*: These capacitor values are for design guidance only. GPCE040A1 8.2. Application Circuit - (2) VDDH(3.3V) 100µ Speaker1 VDDH(3.3V) 100µ Speaker2 0.1µ 1 2 3 8 7 6 6 8 7 0.22 µ 5 4 4 0.1µ 1K 1K VDD 1K 1K RESET 4.7K 0.1µ 0.1µ 20-50pF* 32768Hz X32I 20-50pF* VCOIN X32O RESET IOA[6:0] V2VREF VEXTREF VADREF AGC OPI MICOUT MICN MICP VMIC GPCE040A1 DAC1 DAC2 IOA[15:7] 0.22 µ 5 0.1µ GPY0030A 0.1 µ 1 2 3 0.1 µ GPY0030A IOA[15:7] VSS VDD AVSS AVDD VSSIO VDDIO IOB[15:0] 0.1 µ 0.1 µ 0.1 µ IOB[15:0] VDDH(3.3V) 100µ AVDD (3.3V) 100 µ VDD (3.3V) 100 µ 3300p 3.3K 1K 0.22 µ 0.22 µ 0.22 µ 5.1K 0.1µ 3K MIC 470K 3K 4.7µ 47 µ 5000p 0.1µ IOA[6:0] 220 GPCE040A1 Application Circuit (MIC_IN and with GPY0030A audio amplifier, for 2-battery use only) Oct 01, 2013 Version: 1.4 17 © Generalplus Technology Inc. Proprietary & Confidential Different capacitor values may be required for different crystal/resonator used. Note*: These capacitor values are for design guidance only. GPCE040A1 8.3. Application Circuit - (3) 0.1µ 200~2K VDDH(5V) Speaker1 VDDH(5V) 3 100 µ AVDD (3.3V) 100µ VDDH(5V) IOB[15:0] IOA[15:7] 200~2K GPY0029A Speaker2 VDDH(5V) 2 1 VDD (3.3V) 100µ 0.1µ VDD 4.7K RESET 0.1 µ 0.1µ 0.1µ 0.1µ 20-50pF* RESET DAC1 DAC2 X32I 32768Hz X32O 20-50pF* VCOIN VMIC MICP MICN MICOUT OPI AGC VADREF IOA[6:0] V2VREF VEXTREF GPCE040A1 IOA[15:7] IOB[15:0] VDDIO VSSIO AVDD VDD AVSS VSS 3300p MIC 470K 3K 3K 3.3K 0.1 µ 1K 0.22µ 0.22µ 0.22µ 5.1K 4.7µ 47µ 5000p 0.1µ IOA[6:0] 220 µ GPCE040A1 Application Circuit (MIC_IN and with BJT amplifier, for 3-battery use only) Oct 01, 2013 Version: 1.4 18 © Generalplus Technology Inc. Proprietary & Confidential Different capacitor values may be required for different crystal/resonator used. Note*: These capacitor values are for design guidance only. GPCE040A1 8.4. Application Circuit - (4) 0.1 µ 200~2K VDDH(3.3V) Speaker1 VDDH(3.3V) Speaker2 200~2K IOA[15:7] IOB[15:0] VDDH(3.3V) 100 µ AVDD (3.3V) 100 µ VDD (3.3V) 100 µ 0.1µ VDD 4.7K VSS VDD AVSS AVDD VSSIO VDDIO X32I 32768Hz X32O GPCE040A1 IOB[15:0] IOA[15:7] DAC2 DAC1 RESET 20-50pF* RESET 0.1µ 0.1µ 0.1µ 0.1µ 20-50pF* VCOIN VMIC MICP MICN MICOUT OPI AGC VADREF VEXTREF V2VREF IOA[6:0] MIC 470K 3K 3K 0.1µ 3300p 3.3K 1K 0.22 µ 0.22µ 0.22µ 5.1K 4.7 µ 47 µ 5000p 0.1µ IOA[6:0] GPCE040A1 Application Circuit (MIC_IN and with BJT amplifier, for 2-battery use only) 220 Oct 01, 2013 Version: 1.4 19 © Generalplus Technology Inc. Proprietary & Confidential Different capacitor values may be required for different crystal/resonator used. Note*: These capacitor values are for design guidance only. GPCE040A1 8.5. Application Circuit - (5) 200~2K 0.1 µ VDDH(3.3V) Speaker1 VDDH(3.3V) Speaker2 0.1 µ VDD 4.7K RESET 0.1 µ 20-50pF* RESET DAC1 DAC2 IOA[15:7] VSS VDD AVSS AVDD VSSIO VDDIO IOA[15:7] 0.1 µ IOB[15:0] 100 µ 0.1µ 0.1 µ IOB[15:0] 100µ VDDH(5V) 3 AVDD (3.3V) 200~2K GPY0029A VDDH(5V) 2 1 VDD (3.3V) 100µ X32I 32768Hz X32O GPCE040A1 20-50pF* VCOIN VMIC MICP MICN MICOUT OPI AGC VADREF Note VEXTREF V2VREF IOA[6:0] 0.1µ 3300p 3.3K 0.1µ Note: Case(1): Use AVDD(internal) as AD top reference voltage by setting P_ADC_CTRL($7015) b7 = 0 VEXTREF V2VREF 100µF Case(2): Use V2VREF as AD top reference voltage by setting P_ADC_CTRL($7015) b7 = 1, b8 = 0 VEXTREF V2VREF 0.1µF Input external signal as AD top reference voltage. Case(3): Use external signal as AD top reference voltage by setting P_ADC_CTRL($7015) b7 =1, b8 = 1. (detail see the programming guide) VEXTREF V2VREF IOA[6:0] (7-channel LINE_IN) GPCE040A1 Application Circuit (LINE_IN and with BJT amplifier, for 3-battery use only) Oct 01, 2013 Version: 1.4 20 © Generalplus Technology Inc. Proprietary & Confidential Different capacitor values may be required for different crystal/resonator used. Note*: These capacitor values are for design guidance only. GPCE040A1 8.6. Application Circuit - (6) 200~2K 0.1µ VDDH(3.3V) Speaker1 VDDH(3.3V ) Speaker2 200~2K IOA[15:7] IOB[15:0] VDDH(3.3V) 100 µ AVDD (3.3V) 100µ VDD (3.3V) 100µ 0.1µ VDD 4.7K RESET 0.1 µ 0.1 µ 0.1 µ 0.1µ 20-50pF* RESET DAC1 DAC2 IOA[15:7] IOB[15:0] VDDIO VSSIO AVDD AVSS VDD VSS X32I 32768Hz X32O GPCE040A1 20-50pF* VCOIN VMIC MICP MICN MICOUT OPI AGC VADREF Note 0.1µ 3300p 3.3K 0.1 µ Note: Case(1): Use AVDD(internal) as AD top reference voltage by setting P_ADC_CTRL($7015) b7 = 0 VEXTREF V2VREF 100µF Case(2): Use V2VREF as AD top reference voltage by setting P_ADC_CTRL($7015) b7 = 1, b8 = 0 VEXTREF V2VREF 0.1µF Input external signal as AD top reference voltage. Case(3): Use external signal as AD top reference voltage by setting P_ADC_CTRL($7015) b7 =1, b8 = 1. (detail see the programming guide) V2VREF VEXTREF V2VREF IOA[6:0] (7-channel LINE_IN) VEXTREF IOA[6:0] GPCE040A1 Application Circuit (LINE_IN and with BJT amplifier, for 2-battery use only) Oct 01, 2013 Version: 1.4 21 © Generalplus Technology Inc. Proprietary & Confidential Different capacitor values may be required for different crystal/resonator used. Note*: These capacitor values are for design guidance only. GPCE040A1 9.PACKAGE/PAD LOCATIONS 9.1. Ordering Information Product Number Package Type GPCE040A1-NnnV-C Chip form GPCE040A1-NnnV-HL04n-W Green Package form - LQFP 80 Note1: Code number is assigned for customer. Note2: Code number (N = A - Z or 0 - 9, nn = 00 - 99); version (V = A - Z). Note3: HL04n-W, HL04 is assign for LQFP80, n is assign for customer, W is watch dog bonding option (W=0 enable, W=1 disable). 9.2. Package information 9.2.1. LQFP 80 D D1 E E1 e b A2 A c L1 Symbol A1 Dimension in inch Min. Typ. Max. A - - 0.063 A1 0.002 - 0.006 A2 0.053 0.055 0.057 b 0.007 0.009 0.011 c 0.004 - 0.008 D © Generalplus Technology Inc. Proprietary & Confidential 0.551 BSC. 22 Oct 01, 2013 Version: 1.4 GPCE040A1 Dimension in inch Symbol Min. Typ. D1 0.472 BSC. E 0.551 BSC. E1 0.472 BSC. e 0.020 BSC. L1 0.039 REF PAD No. Max. PAD No. PAD Name PAD Name 1 X32O 37 VSSIO 2 X32I 38 VDDIO 3 TEST 39 VDDIO 4 N/C 40 IOA8 5 VDD 41 N/C 6 N/C 42 N/C 7 N/C 43 IOA9 8 VSS 44 IOA10 9 N/C 45 IOA11 10 VSS 46 11 N/C 47 IOA13 IOA12 12 DAC1 48 IOA14 13 DAC2 49 IOA15 14 V2VREF 50 N/C 15 AVSS 51 N/C 16 AGC 52 VSSIO 17 OPI 53 N/C 18 MICOUT 54 SLEEP 19 MICN 55 IOB15 20 N/C 56 IOB14 21 MICP 57 IOB13 22 VADREF 58 IOB12 23 24 VEXTREF 59 IOB11 AVDD 60 NC 25 VMIC 61 N/C 26 N/C 62 N/C 27 VSS 63 IN/C 28 IOA0 64 VDDIO 29 IOA1 65 IOB10 30 IOA2 66 IOB9 31 IOA3 67 IOB8 32 IOA4 68 IOB7 33 IOA5 69 IOB6 34 IOA6 70 IOB5 35 IOA7 71 IOB4 36 © Generalplus Technology Inc. Proprietary & Confidential VSSIO 72 23 IOB3 Oct 01, 2013 Version: 1.4 GPCE040A1 PAD No. PAD Name PAD No. PAD Name 73 IOB2 77 N/C 74 IOB1 78 VDD 75 IOB0 79 VCOIN RESET 76 80 VSS 9.3. Storage Condition and Period for Package Package Moisture sensitivity level Max. Reflow temperature Floor life storage condition Dry pack LQFP LEVEL 3 220 +5/-0℃ 168Hrs @ ≦30℃/ 60% R.H. Yes Note1: Please refer to IPC/JEDEC standard J-STD-020A and EIA JEDEC stand JFSD22-A112. Note2: or refer to the “CAUTION Note” on dry pack bag. 9.4. Recommended SMT Temperature Profile This “Recommended” temperature profile is a ro ugh guideline for PPF(Pre-Plated Frame) pro duct with 63/37 solder p aste, we SMT process r eference. M ost of GE NERALPLUS leadframe recommend 240℃~245℃ for peak temperature. base product choice Matte Tin and Sn/Bi fo r plating recipe. © Generalplus Technology Inc. Proprietary & Confidential For 24 Oct 01, 2013 Version: 1.4 GPCE040A1 © Generalplus Technology Inc. Proprietary & Confidential 25 Oct 01, 2013 Version: 1.4 GPCE040A1 10. DISCLAIMER The information appearing in this publication is believed to be accurate. Integrated circuits sold b y Generalplus Technology are covered by the warranty and patent indemnification provisions stipulated in the terms of sale only. GENERALPLUS makes no warranty, express, statutory implied or by description regarding the information in this publication or regarding the fre edom of the de scribed chip(s) from patent infringement. FUR THER, GENERALPLUS MAKES N O WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PURPOSE. the specifications and prices at any time without notice. GENERALPLUS reserves the right to halt production or alter Accordingly, the reader is cautioned to verify that the data sheets and other information in thi s publication are current before placing orders. Products described her ein are intended fo r use in normal co mmercial applications. A pplications involving unusual environmental or reliabil ity requirements, e.g. milit ary equipment or medical lif e support equipment, are s pecifically not re commended without additional proc essing by GENERALPLUS for such applications. Please note that application circuits illustrated in this document are for reference purposes only. © Generalplus Technology Inc. Proprietary & Confidential 26 Oct 01, 2013 Version: 1.4 GPCE040A1 11. REVISION HISTORY Date Revision # Description Page OCT. 01, 2013 1.4 Add COMAIR logo to the cover page OCT. 12, 2010 1.3 Modify 3. FEATURES MAY 23, 2008 1.2 Modify 8. APPLICATION CIRCUITS. JUN. 30, 2006 1.1 1. Modify the 9.2 Ordering Information. 21 2. Delete the 9.3.2 PLCC84. 24 4 16-21 3. Modify the 8. APPLICATION CIRCUITS. DEC. 14, 2005 1.0 15-20 Original 28 Note: The GPCE040A1 data sheet v1.0 is a continued version of SPCE040A1 data sheet v1.1. © Generalplus Technology Inc. Proprietary & Confidential 27 Oct 01, 2013 Version: 1.4