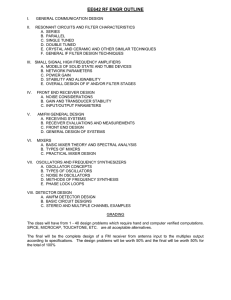

Frequency Translation Techniques for High

advertisement