Basic Logic Functions Switches in series (AND) Truth Tables

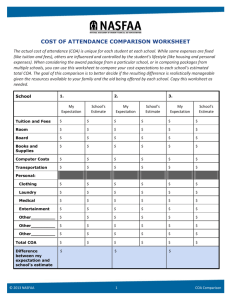

advertisement

Basic Logic Functions Logic Consider a simple switch: it has two positions: 0 OFF = 0, ON = 1 TOPICS: Logic Expressions 1 We can use the switch to allow current to flow to light a bulb Logic Gates Simplifying Logic Expressions 0 Sequential Logic (Logic with a Memory) 1 Consider f to indicate if the bulb is on, by denoting the switch to be A we can write: f=A George Boole (1815-1864), English mathematician, Boolean logic used in digital computers since the late 1930’s, for arithmetic functions, and storage COA 1 COA Switches in series (AND) Truth Tables A truth table define the output values of a function in relation to ALL possible input variables. Each line in the truth table represents a UNIQUE value of the input variables. Two switches can be used in series: A B 0 1 2 0 1 The bulb is on if switch A AND switch B are both on i.e. Input Variables f=A.B n ‘.’ is used to denote AND in Boolean algebra (also ‘ ‘) 2 entries ( n is the number of input variables ) COA 3 Output Variables f 0 0 0 1 4 if (switch A is NOT on) AND (switch B is NOT on) then the bulb is NOT on i.e. f = A.B 0 1 0 1 if either switch A OR B is on then the bulb is on: f=A+B A B 0 0 ‘+’ is used to denote OR in Boolean 0 1 Algebra (also ‘ ‘) 1 0 1 1 COA B 0 1 0 1 Alternative view for OR Can also consider two switches in parallel: B A 0 0 1 1 COA Switches in Parallel (OR) A f=A.B E.g. for the two switches in Series where the bar ( but f 0 1 1 1 so 5 COA ) indicates negation in Boolean Algebra f = A+B f = A+B (negate both sides) A.B = A+B (de Morgans rule) 6 1 Functions of two binary variables Exclusive OR connection Only one switch when on enables the bulb to be on: 0 1 0 A 16 ( = 24) functions can be performed between two binary variables: f = A⊕ B 1 B ‘⊕’ is used to denote EX-OR in Boolean Algebra EX-OR is often referred to as an Equivalence relation (i.e. the output is zero if both inputs are the same) A 0 0 1 1 B 0 1 0 1 COA f 0 1 1 0 A B f0 f1 f2 f3 f4 f5 f6 f7 f8 f9 f10 f11 f12 f13 f14 f15 0 0 1 1 0 1 0 1 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 E.g. 7 f3 = A A.B f4 = f2 = A.B f13 = A.B 1 1 0 1 1 1 1 0 1 1 1 1 A.B 8 Mathematical Laws also apply to Boolean Algebra: Relation Dual Relation A.0 = 0 A.A = A A.A = 0 A.1 = A A.(A + B) = A.A + A.B = A.(1 + B) = A A.(A + B) = A.A + A.B = A.B A+1=1 A+A=A A+A=1 A+0=A A + (A.B) = A + A.B = A.(1 + B) =A A + (A.B) = A + A.B =A+B Commutative Law (ordering may change): 9 e.g. A.B = B.A, A+ B = B + A Associative Law (brackets can be moved): e.g. A.(B.C) = (A.B).C = A.B.C A + (B + C) = (A + B) + C = A + B + C Distributive Law (can multiply out brackets): e.g. A.(B + C) = A.B + A.C (A + B).(A + C) = A.A + A.C + B.A + B.C = A.(A + C + B) + B.C COA 10 Electronic Logic Gates De-Morgans Rule: A+B = A.B, 0 1 1 0 0 COA Some Logic Relationships COA f0 = f1 = 1 0 1 1 Use concepts of Boolean algebra, often using voltages of 5V and 0V to represent 1 and 0. A+B = A.B To change form of expression: 1) Changes AND’s to OR’s and vice versa, 2) negate variables (or sub-expressions) 3) negate resulting expression Standard symbols: NOT AND OR EX-OR NAND NOR EX-NOR Examples: A.(C+D) = (A.C) + D = (A.B) + (C.D) = COA A.( C.D ) = A.( C.D ) (A+C)+D A+B+C+D a ‘ ‘ indicates negation 11 COA 12 2 Combinatorial Logic Circuits NAND Gates Can be used to implement any other function, e.g. A logic circuit whose outputs are logical functions of its inputs A 0 0 1 1 Consider the EX-OR function f = A ⊕ B From the Truth Table we can write: f = A.B + A.B B 0 1 0 1 NOT f 0 1 1 0 A f = A = A.A A AND f = A.B = A.B OR This can be represented by the logic circuit: A A.B B A f = A+B = A.B A+B B A A A.B A.B + A.B EX-OR A.B B B COA 13 We can obtain a “sum of products” equation directly from a Truth Table. P f C R Consider intermediate signals P, Q, R, where P = A.B, Q = B.C, R = A.C, and the output is f = A.B + B.C + A.C 14 Truth Table -> Boolean equation Can construct a Truth Table for a logic circuit, e.g. Q A+B B COA Logic Circuit -> Truth Table A B A f = A.B + A.B = A.B.A . A.B.B A B C P Q R f 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 1 1 0 0 0 1 0 0 0 1 0 0 0 0 0 1 0 1 0 0 0 1 0 1 1 1 COA 15 A B C f 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 1 1 0 0 1 0 1 1 A.B.C A.B.C A.B.C A.B.C So function f is TRUE when any of these combinations are TRUE A.B.C f = A.B.C + A.B.C + A.B.C + A.B.C + A.B.C COA Minimising Logic Expressions 16 1) Mathematical Laws e.g. Logic expressions can be simplified to reduce complexity (and also the number of gates used), in two main ways: f = A + ( B.C ) + ( B.D) = A + ( B.C ) . ( B.D ) 1) use mathematical laws (commutative, Associative, Distributive, de-Morgans etc). 2) use truth table to construct a ‘sum of products’ form and represent graphically (Karnaugh Map) de-Morgan = A + (B+C).(B+D) de-Morgan = A + B.B + C.B + B.D + C.D distributive = A + B.( B + C + D ) + C.D = A + B + C.D In either case the truth table for the logic expression before and after minimisation must be the SAME. COA 17 COA 18 3 2a) Sum of Products Simplifying Sum of products form can be simplified by looking for terms that differ by only one variable and its complement (X and X), e.g. Use the truth table to obtain the sum of products. (So called, since an OR ‘+’ is considered as a sum, and an AND ‘.’ as a product) A B C f 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 1 1 0 0 1 0 1 1 f = A.B.C + A.B.C + A.B.C + A.B.C + A.B.C A.B.C + A.B.C = A.B.(C + C) (C + C) = 1 A.B.(C + C) = A.B but So Simplify f : f = A.B.C + A.B.C + A.B.C + A.B.C + A.B.C f = = = = COA 19 COA 20 Adjacent values 2b) Karnaugh Maps Geometric (graphical) way to quickly derive minimal expressions for a logic function (of a few variables) Key idea of the Karnaugh Map is that horizontally and vertically adjacent squares correspond to input values that differ in only one variable. A three variable function can be represented by a 4x2 rectangle, AB C 0 00 01 11 A.B.(C + C) + A.B.C + A.B.(C + C) A.B + A.B.C + A.B A.B + A.(B.C + B) A.B + A.(C + B) AB 00 C e.g. 10 01 11 10 0 A.B.C 1 1 A.B.C COA NOTE : numbering on the edge of the Karnaugh Map - ‘Gray coded’ 21 COA 22 Example Karnaugh Maps AB C 0 1 AB 00 01 11 10 0 0 0 0 C 0 0 0 1 0 1 Further Example AB 00 01 11 10 0 0 1 0 C 0 0 0 1 0 1 00 01 11 10 1 1 0 1 1 0 0 1 01 11 10 0 1 0 0 0 1 1 1 1 0 C.B.(A + A) OR ⇒ 1 f = A.B + C.B f = A.B + A.B + A.C = B + A.C A.B 00 01 11 10 1 1 0 1 1 0 0 1 A.C ⇒ f = B + A.C B A.B.(C + C) COA AB C 0 A.C ⇒ A.B To use a Karnaugh map to obtain a logic expression, look for groupings of ones, e.g. AB 00 C A.B.C A.B.C Each square represents a particular value of the input variables (A, B, C in this case). 23 COA 24 4 Karnaugh Map Grouping ● Larger Karnaugh Maps Karnaugh maps can be used for more variables, AB e.g. (A,B,C,D) Left most-column is also adjacent to right mostcolumn, & top row is adjacent to bottom row. 01 11 10 A.B.C 11 1 10 e.g. A.B.C A.B.C Also: – Groupings may overlap – Minimum logic expression is obtained on minimum number of groupings – Group contains power of two elements (2,4,8,16 etc) COA 00 01 11 10 0 0 00 01 11 10 1 00 1 0 1 01 1 1 1 1 01 0 0 1 1 11 1 1 0 0 11 0 0 0 0 10 0 0 0 0 10 1 0 0 1 0 0 0 01 1 1 0 0 11 0 1 1 0 10 0 0 0 0 CD A.C.B A.B.D B.C.D 26 f = A + ( B . C ) + ( B . D) f = A.C.B + A.B.D + B.C.D or f = A.C.B + A.C.D + B.C.D Construct Truth Table: Can result in more than 1 logic expression (but equivalent) AB 00 0 1 0 1 01 1 0 1 0 11 0 1 0 1 10 1 0 1 0 Cannot get any groupings => no minimisation possible This is actually an EX-OR function between the 4 input variables: f = (A ⊕ B) ⊕ (C ⊕ D) COA 27 A B C D B.C 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Cout Full Adder Cin S inputs - A,B, Cin (each one bit) outputs - S, Cout (one bit) (B.C)+(B.D) f 1 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 0 1 1 1 1 1 0 0 0 1 1 1 1 1 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 CD AB 00 01 11 10 00 0 1 1 1 01 0 1 1 1 11 1 1 1 1 10 0 1 1 1 f = B + A + C.D 28 AN-1 BN-1 AN-2 BN-2 Cin A B Cout S 0 0 0 0 1 1 1 1 0 1 0 1 0 1 0 1 0 0 0 1 0 1 1 1 0 0 1 1 0 0 1 1 B.D N-bit Full Adder One-bit Full Adder (in Arithmetic Logic Unit - ALU) B 1 1 0 0 0 0 0 0 1 1 0 0 0 0 0 0 COA Common Combinatorial Circuits in Computers A f = B.D + A.C Function Minimisation A.C.D 00 01 11 10 CD COA AB 00 01 11 10 AB 0 f = A.D + A.C.D 25 Examples COA AB 00 0 CD 00 1 Movement from 1 square to an adjacent, results in the change of only ONE variable 01 0 CD 00 01 11 10 CD 00 AB 00 C 0 1 1 0 1 0 0 1 Cout FA FA SN-1 SN-2 ... A1 B1 A0 B0 FA FA S1 S0 0 Carry output from one Full Adder -> carry input of next 29 COA 30 5 Adder/Subtractor N-bit Adder/Subtractor To convert into an adder/subtractor: add control input (Z): AN-1 BN-1 AN-2 BN-2 Z = 0 -> S = A + B Z = 1 -> S = A - B Cout Z 0 0 1 1 B 0 1 0 1 A0 B0 Z Note: A - B = A + (-B) Problem: How do we calculate ‘-B’ ? Answer: Use two’s complement, i.e. invert the N-bit binary number B (Use EX-OR gates) and add 1 (Carry in) A1 B1 f 0 1 1 0 COA FA FA SN-1 SN-2 ... FA FA S1 S0 0 B B 31 COA 32 Demultiplexer Multiplexers & de-multiplexers a) Multiplexer - output is a selected input. b) de-Multiplexer - opposite of a multiplexer allowing an input to appear on any one of the outputs: e.g. a ‘4-1’ multiplexer (four inputs to one output) X0 X1 X2 Y X3 S0 S1 Y 0 0 1 1 0 1 0 1 X0 X1 X2 X3 S0 S1 Y0 Y1 Y2 A Y3 S0 S1 Y0 Y1 Y2 Y3 0 0 1 1 0 1 0 1 A 1 1 1 1 A 1 1 1 1 A 1 1 1 1 A S0 S1 e.g. Y0 = S0.S1.A Y = X0.S0.S1 + X1 S0.S1 + X2 S0.S1 + X3.S0.S1 COA 33 COA Decoders and Encoders 34 Active High Decoder Used to either encode a set of inputs into a defined representation on the outputs, or to decode the representation into a number of outputs Previous example decoder had an output which was active low (= 0). i.e. the active output and only this output was low. e.g. decoding 2 inputs to 4 unique outputs: Can also have active high outputs : X0 X1 Y0 Y1 Y2 Y3 X1 X0 Y0 Y1 Y2 Y3 0 0 1 1 0 1 0 1 0 1 1 1 1 0 1 1 1 1 0 1 1 1 1 0 e.g. 2 to 4 line decoder (active high outputs) X0 X1 Note that the two inputs select which output is active (active = 0 in this case) These decoders are often used to address unique memory locations in a micro-processor system COA 35 COA Y0 Y1 Y2 Y3 X0 X1 Y0 Y1 Y2 Y3 0 0 1 1 0 1 0 1 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 36 6 Sequential Logic Flip-Flop Operation So far have considered combinations of Logic gates (COMBINATORIAL LOGIC), but now consider a circuit whose outputs are fed back to inputs: Output Q is Set (to one) when S = 0 (& R = 1), and is Reset (to Zero) when R = 0, (& S = 1) If S = R = 1, then Q does not change S Q This behaviour is summarised in the truth table: ‘Flip-Flop’ P R Consider: then if and then then S = 1, R = 0 S = 1, R = 1 S = 0, R = 1 S = 1, R = 1 -> -> -> -> P = 1, Q = 0 P = 1, Q = 0 P = 0, Q = 1 P = 0, Q = 1 37 1 0 Q 1 0 Q 1 0 A modification to the previous flip-flop is known as the D-type transparent latch: D Q Q Enable when Flip-Flop output is not just dependent on the input (as in combinatorial logic) but also on its previous behaviour circuits of this type are called SEQUENTIAL circuits COA COA D x 0 1 40 Clocked Flip-Flops Flip-flops whose output changes only an a rising edge (clock) The truth table for the D-type transparent latch can be written as: Enable D Q Q 0 0 Q Q 0 1 Q Q 1 0 0 1 1 1 1 0 Enable 0 1 1 Enable = 1, Q = D (Q = D) Enable = 0, Q = no change (previous value) i.e. output can change only when the enable line is high 39 Truth Table Q Q 0 1 Q Q 1 0 Enable Q 0 Q 1 D D-type D Q Q D T JK-type J Clock K Q Clock Dn Clk 0 1 T-type Q Clock ↑ ↑ Q Q T Clk Q J K Clk Q 0 1 0 1 ↑ ↑ 0 0 1 1 0 1 0 1 ↑ ↑ ↑ ↑ Q 0 1 Q Q Q Often have additional gates included for set (=1) and reset (=0) (Important to understand the operation of these flip-flops) where ‘x’ stands for don’t care. COA P 38 time or: x x - hazard condition 1 0 0 1 no change D-type transparent latch Can also view this operation in a timing diagram R Q 0 1 0 1 COA Flip-Flop Timing Diagram 1 0 R 0 0 1 1 The flip-flop is able to STORE a value when both S = R = 1 COA S S 41 COA 42 7 Example circuits using Flip-Flops N-bit Shift Register A register that stores and shifts a number N-bit Register or Latch (stores N-bits) AN-1 AN-2 D-type A1 ... D-type A0 D-type D D-type D-type QN-1 QN-2 Q1 Q0 the N-bit number (AN-1 AN-2...A1A0) is stored in the register on a low to high ( ↑ ) transition of the clock. The number will then appear on the outputs (QN-1 ... Q0) COA D-type D-type 43 Q1 Q0 COA 44 Logic components considered so far have two possible states (1 or 0). However, there is a further gate termed a three-state buffer whose output can be placed in a third state (OFF): D-type QN-2 Q1 Q0 QN-2 Three-state Logic ... D-type D-type When a transition on the clock (low -> high) occurs, then each bit in the register will be shifted one place to the right N-bit Counter Clock D-type Clock Clock QN-1 ... D-type In QN-1 Enable Each flip-flop is clocked only on a transition of high -> low (negative clock edge) of the previous output. When Enable is High, the Input is disconnected from the output Note - use of a circle (on the input to the D-type) to indicate the negative transition COA Out When Enable is Low, the Input is connected to the output 45 COA Three-state Buses 46 Multi-bit Bus Can use three state buffers to allow different sources of data onto a common BUS. e.g. 4-bit bus Bus E1 Bus 4 e.g. 1-bit wide Bus Bus A A A D-type E1 E1 When E1 = 0, A will be placed on the Bus 4 B When E2 = 0, B will be placed on the Bus B B 4 D-type E2 E2 E2 When E1 = 0, A will be placed on the Bus When E2 = 0, B will be placed on the Bus N.B. Should not have E1=0 and E2 = 0 at the same time! COA Or 47 COA 48 8 Properties of Logic Gates ● Propagation Delay Logic values by Voltage level: Voltage Vmax Each gate has a propagation delay, typically nanoseconds (1x10-9s) or less. This limits the speed at which Logic circuits work. Propagation delays can be reduced by putting logic gates close together (eg. on the same IC - VLSI) e.g. Logic 1 V1min ‘Forbidden region’ V0max Typically (TTL), Vmax = 5, V1min = 2.8, V0max = 0.8 Logic 0 Gate Prop. Delay(ns) NOT 1.0 NAND 1.2 AND 1.7 OR 1.2 NOR 1.5 A B 0V Do NOT connect outputs together: f C (values for illustration only) (Three-state buffers ok) What is the maximum propagation delay in this circuit? COA 49 COA Example Programmable Logic Array - PLA Logic IC’s Elementary logic gates and functions can be obtained in small IC’s (e.g. 7400 - quad NAND gate). However, systems commonly use programmable logic devices. PAL’s PLA’s FPGA’s - Programmable Array Logic Programmable Logic Arrays Field Programmable Gate Arrays (Some contain up to 100’000s simple logic gates) m COA 51 COA AND array AND array x2 x3 52 Example PLA PLA Organisation x1 Output Buffers e.g. Can perform an ‘AND’ function on a combination of any inputs (and their inverses), followed by an ‘OR’. I.e. performs a ‘Sum of Products’ combinatorial function. I1 x1 AND x2 . . .. array . . xn I2n P1 . . . Pk O1 f1 OR . . . . array . . fm O Input Buffers and inverters ● 50 x1 I1 I2 I3 I4 I5 I6 x2 x3 I1 I2 I3 I4 I5 I6 P1 = X1 . X2 P2 = X1 . X3 P3 = X1 . X2 . X3 P4 = X1 . X3 f1 = P 1 + P 2 + P 3 P1 P2 P3 P1 P4 P3 f2 = P 1 + P 3 + P 4 P4 f1 f2 f2 OR array OR array Un-broken connections Links (Fuses) that can be broken COA P2 f1 53 COA 54 9 Summary (Logic) ● ● ● ● ● ● ● ● Processor components Boolean Algebra Logic Gates Function definition using Truth Tables Logic Function Minimisation (algebraic manipulation & Karnaugh Maps) Some common functional units Example Sequential Logic devices (using flip-flops) Three state logic (Buses) Programmable logic COA Also looked at some units that form major components of Microprocessors within a Computer System: 55 Adder / Subtractor (data processing) Registers (data storage) Busses (data transfer) COA Minimal µProcessor 56 Further Reading Clements: 8 Subtract Arithmetic Logic Unit (ALU) OR 8 Tannenbaum: Section 3.1, 3.2, 3.3.1 - 3.3.3 8 Register Buffer Clock Chapter 2 8 Bus Add Both cover combinatorial logic, Boolean algebra, Sequential logic, Programmable logic. Enable COA 57 COA 58 10