Lab Exercise 2 - Department of Computer Science, University of

advertisement

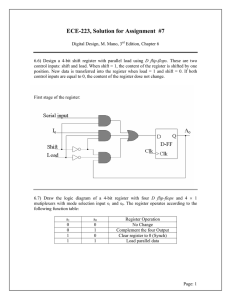

UNIVERSITY OF CYPRUS DEPARTMENT OF COMPUTER SCIENCE CS 121 – DIGITAL SYSTEMS LABORATORY LAB EXERCISE 2 LAB INSTRUCTOR: CHRYSOSTOMOS CHRYSOSTOMOU SPRING 2001 CS 121 – DIGITAL SYSTEMS LABORATORY LAB EXERCISE 2 CS 121 – Digital Systems Laboratory LAB EXERCISE 2 A. OBJECTIVES The purpose of this lab is: 1. To design and simulate a series of combinational circuits. 2. To create macros (or modules) and to build a top-level schematic consisting of underlying macros. 3. To enable students to built and test combinational circuits with the aid of the Digital Trainer. PRE-LAB B. THEORY - PREPARATION 1. Binary Ripple Carry Adder In the previous lab you designed a full adder. In this part you will be using this module to build a 4-bit adder with the use of macros (hierarchical design methodology). A parallel binary adder is a digital circuit that produces the arithmetic sum of two binary numbers using only combinational logic. The parallel adder uses n full adders in parallel, with all input bits applied simultaneously to produce the sum. The parallel adder is referred to as a ripple carry adder. The full adders are connected in cascade, with the carry output from one full adder connected to the carry input of the next full adder. Prepared by Chrysostomou Chrysostomos Department of Computer Science – University of Cyprus 1 CS 121 – DIGITAL SYSTEMS LABORATORY LAB EXERCISE 2 Figure 1 shows the interconnection of four full-adder blocks to form a 4-bit ripple carry adder. Figure 1 The augend bits of A and the addend bits of B are designated by subscripts in increasing order from right to left, with subscript 0 denoting the least significant bit. The carries are connected in a chain through the full adders. The input carry to the parallel adder is C0, and the output carry is C4. An n-bit ripple carry adder requires n full adders, with each output carry connected to the input carry of the next-higher-order full adder. Each full adder receives the corresponding bits of A and B and the input carry and generates the sum bit for S and the output carry. The output carry in each position is the input carry of the next-higher-order position. Observe that the design of this circuit by the usual method would require a truth table with 512 entries, since there are nine inputs to the circuit (4 bits for A, 4 bits for B and a Carry input). By cascading the four instances of the known full adders, it is possible to obtain a simple and straightforward implementation without directly solving this larger problem. This is an example of the power of hierarchy and reuse in design. Prepared by Chrysostomou Chrysostomos Department of Computer Science – University of Cyprus 2 CS 121 – DIGITAL SYSTEMS LABORATORY LAB EXERCISE 2 a. Use the XILINX software tool to create a macro symbol for a full adder circuit, designed in Lab exercise 1. b. Design the 4-bit ripple carry adder, shown in Figure 1, using the principle of hierarchy. c. Simulate the above circuit with a representative set of inputs. d. Print out the schematic and the waveforms obtained, and attach them in the report. e. Comment on the results. 2. 4-bit 1´s Counter The block diagram of a 4-bit 1´s counter is shown in Figure 2. A0 A1 A2 A3 X0 ? X1 X2 Figure 2 The circuit computes the number of 1’s at the inputs A0, A1, A2, and A3. The outputs X2, X1, and X0 range in value from binary 000 (decimal 0) to 100 (decimal 4), depending on the number of 1´s in the inputs. For example, when (A 0, A1, A2, A3) = 1001, (X 2, X1, X0) must be equal to binary 010 to indicate that there are two 1´s on the inputs. a. Having in mind the operation of a 4-bit 1´s counter explained above, use the design methodology that you have learned from the lectures to design such a logic circuit. • Identify and comment on the properties of the prime EPI and non-EPI of the output functions. b. Use the XILINX software tool to design the above circuit. Prepared by Chrysostomou Chrysostomos Department of Computer Science – University of Cyprus 3 CS 121 – DIGITAL SYSTEMS LABORATORY LAB EXERCISE 2 c. Simulate the circuit with all the possible combinations of inputs. d. Print out the schematic and the waveforms obtained, and attach them in the report. e. Comment on the results. 3. 8-bit 1’s Counter The block diagram of an 8-bit 1´s counter is shown in Figure 3. A0 S0 A1 A2 A3 A4 A5 A6 ? S1 S2 S3 A7 Figure 3 The circuit computes the number of 1’s at the inputs A0, A1, A2, A3, A4, A5, A6, and A7. The outputs S0, S1, S2 and S3 range in value from binary 0000 (decimal 0) to 1000 (decimal 8), depending on the number of 1´s in the inputs. For example, when (A0, A1, A2, A3, A4, A5, A6, A7) = 10000001, (S3, S2, S1, S0) must be equal to binary 0010 to indicate that there are two 1’s on the inputs. A way to implement the 8-bit 1’s counter using the principle of hierarchy and reuse of design is shown in Figure 4. Prepared by Chrysostomou Chrysostomos Department of Computer Science – University of Cyprus 4 CS 121 – DIGITAL SYSTEMS LABORATORY LAB EXERCISE 2 A7 A6 A5 A4 A3 A2 4-bit 1´s counter X5 X4 A1 A0 4-bit 1´s counter X3 X2 X1 X0 4-bit Ripple Carry Adder S3 S2 S1 S0 Figure 4 a. Use the XILINX software tool to design the 8-bit 1´s counter, shown in Figure 4. b. Simulate the above circuit with a representative set of inputs. c. Print out the schematic and the waveforms obtained, and attach them in the report. d. Comment on the results. Prepared by Chrysostomou Chrysostomos Department of Computer Science – University of Cyprus 5 CS 121 – DIGITAL SYSTEMS LABORATORY LAB EXERCISE 2 4. 3-bit 1’s Counter The block diagram of a 3-bit 1´s counter is shown in Figure 5. A0 X0 A1 A2 ? X1 Figure 5 The circuit computes the number of 1’s at the inputs A0, A1, and A2. The outputs X1 and X0 range in value from binary 00 (decimal 0) to 11 (decimal 3), depending on the number of 1´s in the inputs. For example, when (A 0, A1, A2) = 101, (X 1, X0) must be equal to binary 10 to indicate that there are two 1´s on the inputs. a. Having in mind the operation of a 3-bit 1´s counter explained above, use the design methodology that you have learned from the lectures to design and simulate such a logic circuit using the XILINX software tool. Print out the schematic and the waveforms obtained, and attach them in the report. Comment on the results. b. Use the Digital Trainer to build a 3-bit 1´s counter, using the circuit that you designed. • Due to the limited number of ICs provided, you may use NAND gates to implement one output function, and AND/OR gates to implement the other output function. c. Use the Logic Probe to verify the logic levels of the inputs and outputs. d. Comment on the results. e. Bring with you the designed circuit and be ready to demonstrate to the lab instructor the correctness of your design. Prepared by Chrysostomou Chrysostomos Department of Computer Science – University of Cyprus 6 CS 121 – DIGITAL SYSTEMS LABORATORY LAB EXERCISE 2 LAB C. EXPERIMENTAL RESULTS 1. BCD-to-Seven-Segment Decoder Digital readouts found in electronic calculators and digital watches use LEDs. Each digit of the readout is formed from seven segments, each consisting of one LED that can be illuminated by digital signals. A BCD-to-seven-segment decoder is a combinational circuit that accepts a decimal digit in BCD and generates the appropriate outputs for the selection of segments that display the decimal digit. The seven outputs of the decoder (a, b, c, d, e, f, g) select the corresponding segments in the display, as shown in Figure 4a. The numeric designations chosen to represent the decimal digits are shown in Figure 4b. Figure 4a Figure 4b The BCD-to-seven-segment decoder has four inputs for the BCD digit and seven outputs for choosing the segments. The truth table of the combinational circuit is listed in Table 1. Prepared by Chrysostomou Chrysostomos Department of Computer Science – University of Cyprus 7 CS 121 – DIGITAL SYSTEMS LABORATORY LAB EXERCISE 2 Table 1 Each decimal digit illuminates the proper segments for the decimal display. For example, BCD 0011 corresponds to decimal 3, whose display needs segments a, b, c, d, and g. The truth table assumes that a logic 1 signal illuminates the segment (LED on) and a logic 0 signal turns the signal off (LED off). The six binary combinations 1010 through 1111 have no meaning in BCD; therefore all the segments are turned off. a. Study the data sheet for such a decoder (type SN74LS47) given in the Introductory Tutorial on the Use of Lab Equipments. b. Use the Digital Trainer with the already 3-bit 1´s counter built in to generate the appropriate outputs of the BCD-to-7-segment decoder for the selection of segments that display the decimal digit. • Remember that a 3-bit 1´s counter has two outputs having a range in value from decimal 0 to decimal 3; therefore we only want to display numbers from 0 to 3. Think how to accomplish that by using only 2 inputs from the BCD-to-7-segment decoder and generating numbers from 0 to 3. Prepared by Chrysostomou Chrysostomos Department of Computer Science – University of Cyprus 8 CS 121 – DIGITAL SYSTEMS LABORATORY LAB EXERCISE 2 c. Discuss the results indicating whether your circuit functions properly. d. Be ready to demonstrate the correctness of your design. 2. Priority Encoder An encoder is a digital function having 2n input lines and n output lines. The output lines generate the binary code corresponding to the input value. Consider a four-input priority encoder with four inputs D0, D1, D2, and D3 generating two outputs A0 and A1. There is also a valid output designated by V. A priority encoder is a combinational circuit that implements a priority function. The operation of the priority encoder is such that if two or more inputs are equal to 1 at the same time, the input having the highest priority takes precedence. A higher priority for inputs is established with higher subscript numbers (going from the LSB to the MSB). For example, if both D2 and D1 are 1 at the same time, D2 has higher priority than D1; therefore the output lines generate the corresponding to the input binary number (binary 2). Hence, input D3 has the highest priority; so, regardless of the values of the other inputs, when this input is 1, the output for A1A0 is 11 (binary 3). D2 has the next priority level. The output is 10 if D2 = 1, provided that D3 = 0, regardless of the values of the lower priority inputs. The output for D1 is generated only if all inputs with higher priority are 0, and so on down the priority levels. The valid output V is set to 1 only when one or more of the inputs are equal to 1. If all inputs are 0, V is equal to 0, and the other two outputs of the circuit are not used and are specified as don’t care conditions. Prepared by Chrysostomou Chrysostomos Department of Computer Science – University of Cyprus 9 CS 121 – DIGITAL SYSTEMS LABORATORY LAB EXERCISE 2 Therefore, we form the truth table of a four-input priority encoder as follows (Table 2): Table 2 With the use of X’s, this condensed truth table with just five rows represents the same information as the usual 16-row truth table. Whereas X’s in output columns represent don’t care conditions, X’s in input columns are used to represent products terms that are not _ _ minterms. For example, 001X represents the product term D3D2D . 1 Just as with minterms, each variable is complemented if the corresponding bit in the input combination from the table is 0 and is not complemented if the bit is 1. If the corresponding bit in the input combination is an X, then the variable does not appear in the product term. Thus, for 001X, _the_ variable D0, corresponding to the position of X, does not appear in D3D2D1. The number of rows of a full truth table represented by a row in the condensed table is 2p, where p is the number of X’s in the row. For example, in Table 2, 1XXX represents 23 = 8 truth table rows, all having the same value for all outputs. In forming a condensed truth table, we must include each minterm in at least one of the rows in the sense that minterm can be obtained by filling in 1’s and 0’s for the X’s. Also, a minterm must never be included in more than one row such that the rows in which it appears have one or more conflicting output values. Prepared by Chrysostomou Chrysostomos Department of Computer Science – University of Cyprus 10 CS 121 – DIGITAL SYSTEMS LABORATORY LAB EXERCISE 2 a. Design a 4-input priority encoder with inputs and outputs as in Table 2, but with the truth table representing the case in which input D0 has the highest priority and input D3 has the lowest priority. Show the design methodology that you used to create such a circuit. b. Use the XILINX software tool to design a four-input priority encoder, using the circuit that you designed in part C.2a. c. Simulate the above circuit with all possible combinations of inputs. d. Print out the schematic and the waveforms obtained, and attach them in the report. e. Comment on the results. D. CONCLUSIONS The conclusions should contain a summary of the results obtained. Prepared by Chrysostomou Chrysostomos Department of Computer Science – University of Cyprus 11