Spice Models with Temperature-Bias-Frequency Concerns

advertisement

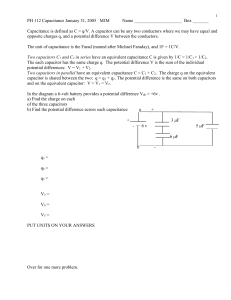

Capacitor EDA Models with Compensations for Frequency, Temperature, and DC Bias John Prymak, Peter Blais, William Buchanan, Edward Chen, Ken Lai, Gianpietro Malagoli, Allen Mayar, Matti Niskala, Axel Schmidt, Paul Staubli, Boris Vildaver KEMET Electronics Corporation, 2835 KEMET Way, Simpsonville, SC 29681 Phone: +1-864-963-6300, FAX: +1-864-228-4081, Email: johnprymak@kemet.com Abstract Models created to simulate behavior of capacitors are usually generated as simplistic as possible, using data gathered at room ambient temperatures and, normally with no DC bias applied. The simplest RLC model will use the nominal capacitance of the device, the minimum ESR obtained over a broad frequency spectrum, and an inductance based on the lowest inductance measured. The simpler model is preferred because many circuits deal with hundreds of capacitors and adding these to the computational activity slows the EDA programs down tremendously. In reality, the capacitance may change dramatically with frequency, as in the case of bulk or electrolytic capacitors where the capacitance at 300 kHz could be a small fraction of the nominal capacitance. The ESR is not a constant with frequency, and may vary by decades from the minimum. Based on many capacitor manufacturers, the variation of capacitance with temperature is specified in catalogs and is moderate for most requirements, but much larger variations of capacitance with the application of DC bias is like a “dirty little secret” that very few discuss (as high as 70% capacitance loss at rated voltage). The performance of the capacitor within an application at temperatures different from 25°C, with DC bias, and at various frequencies may behave dramatically different from that indicated by the model. Methods will be presented for quickly creating SPICE models that can be imported into several EDA software tools with a little more complexity than the simplest RLC, at variable temperatures and bias conditions, centered at any frequency, thereby reducing the errors created between modeled devices and real circuit. It will also be shown how a single models can be created to represent multiple capacitors or any number in parallel; thereby eliminating the major problem with extending computational times as multiple capacitors add multiple sub-circuits or nodes in the calculations. Simple Models (MLCC and Film Capacitors) The simplest model for a capacitor is the capacitor by itself, but this dismisses the parasitic resistance and inductance associated with real devices. The perfect capacitor would show ever-declining impedance with ever-increasing frequency, and have no series resonance. For very low frequency applications (mHz), some of the ECDL (electrochemical double-layer) capacitors may act as if they’re perfect, but the perfect capacitor is a myth. The problem is that for some EDA tools, the capacitor is treated as a perfect capacitor The RLC structure of a capacitor with a series resistance and series inductance is the minimal model for any practical capacitor model. The resistance accounts for the ESR (equivalent series resistance) of the capacitor as the conductive plates have some resistance and the act of charging and discharging the electric field in the dielectric creates a work function, losing energy in the process. The inductance accounts for the ESL (equivalent series inductance) as a defined magnetic field created because the path through the capacitor is constricted over the physical length between the terminals of the device. Now that the structure has been defined, how are the elements of the RLC model set? Consider the frequency scan of the 4.7 µF capacitor as shown in Figure 2. Based on the measured response at the self-resonance frequency (SRF) of 2.18 MHz, the measured ESR was used. Figure 1. Simple RLC circuit model. ©Electronic Components Association, Inc., Arlington, Virginia, USA 2010 Capacitor and Resistor Technology Symposium Proceedings, CARTS Conference, New Orleans, LA, March 2010 Page 1 of 13 The ESL was calculated based on a projected capacitance (C R – as there is a slight decay of capacitance with frequency) and the frequency (F R ) at which self-resonance occurs and the relationship defined with the following equation. Figure 2. Frequency scan of measured and modeled 4.7µF capacitor. The simple RLC model’s ESR performance only matches the actual ESR at the point this value was captured, at selfresonance. The discrepancies in ESR can be overcome by making the model more complex, but in the desire that the model be as simple as possible, we will concentrate on the impedance magnitudes as the idealized response. The simple RLC model appears to work extremely well for simulating the impedance magnitude up through 10 MHz, but appears to have an increasing deviation above that frequency with the greatest discrepancy at 100 MHz. Some manufacturers use the best ESR and ESL in a frequency scan for the “optimum” selection of the ESR and ESL in the RLC model. From the limited frequency measurements listed in Table 1, the “optimum” ESR and ESL selections would be the ESR of 3.06 mΩ at 10 MHz, and an ESL of 0.74 nH at 100 MHz. Table 1. Selecting ESR and ESL as seed values. Using the nominal capacitance of 4.7 µF and these “optimum” elements in the RLC model, the generated frequency response for the impedance magnitude versus frequency is as shown in Figure 3. Now the discrepancy at 100 MHz is nearly eliminated, but the SRF and difference in impedance near the SRF are increased. The difference in impedance at 100 MHz has not totally been eliminated because impedance has a resistive element, and changing the ESL did not have any effect on ESR as it remains frequency independent. ©Electronic Components Association, Inc., Arlington, Virginia, USA 2010 Capacitor and Resistor Technology Symposium Proceedings, CARTS Conference, New Orleans, LA, March 2010 Page 2 of 13 Figure 3. Comparing impedance magnitude versus frequency for optimum ESR and ESL selections. Looking at this discrepancy in terms of percent error (Figure 4), the slight discrepancies of the impedance based on SRF resistive and inductive elements shows errors up to 26% at 100 MHz, but the errors in impedance for the optimum selections are as high as 170% nearest the SRF. The huge errors associated with the optimum solution are created because the ESL declines between the SRF and 100 MHz. Figure 4. Error of impedance magnitude versus frequency (calculated versus measured). Modifying the Simple RLC Some manufacturers like to quote this ESL as representative of their pieces because “lower is always better” whereas KEMET typically quotes the ESL at SRF for their pieces. Some manufacturers have claimed that their pieces are better than KEMET’s because of the lower ESL. Actually, both of these ESLs are wrong. The ESL changes with frequency, and this effect is more noticeable in the high CV product of MLCCs. In low value MLCCs, this effect is hardly measurable and using a constant ESL will not generate large errors. ©Electronic Components Association, Inc., Arlington, Virginia, USA 2010 Capacitor and Resistor Technology Symposium Proceedings, CARTS Conference, New Orleans, LA, March 2010 Page 3 of 13 L1 L2 L3 R2 R3 R1 C1 Figure 5. RL networks added to simple RLC. By adding a couple of RL networks to the simple RLC (Figure 5), an effect of decreasing ESL can be simulated, and along with a decreasing ESL, and increasing ESR (as measured) is also be created. In Figure 6, the plots of impedance for the actual measurement and the modified RLC with RL networks are consistently equal. The SRFs are the same and the 100 MHz impedances are the same. In Figure 7, the error percent show that they are not exactly the same, but the maximum error is less than 5%. This error could be reduced by adding additional RL networks, but again these added elements would add computational time with minimal benefit realized. Figure 6. Impedance response of actual versus RLC with RL networks. Figure 7. Error in impedance magnitude for RLC with RL networks versus measured response. ©Electronic Components Association, Inc., Arlington, Virginia, USA 2010 Capacitor and Resistor Technology Symposium Proceedings, CARTS Conference, New Orleans, LA, March 2010 Page 4 of 13 Temperature and Voltage Factors By changing the temperature to -55°C or +85°C, this creates changes in capacitance and ESR. In Table 2, the capacitance and ESR at -55°C and at +85°C are shown in relation to the +25°C readings. The change in capacitance and ESR, both contribute to a change in impedance. Table 2. Capacitance and ESR at various temperatures. The plot of the absolute percent error for the impedance (Figure 8) for the most part throughout the frequency spectrum reflects the change in capacitance, and this change is within the 20% window for accurate impedance projections. The largest errors occur near self-resonance where the impedance reflects the changes in ESR at these temperatures and these changes are well beyond the desired 20% window. Figure 8. Absolute percentage error of impedance at -55°C and +85°C, referenced to +25°C readings. For MLCCs with dielectrics that have a non-linear temperature coefficient of capacitance (TCC) or have higher values of dielectric constant, there is an increasing susceptibility to DC bias voltage. With this device, it is an X5R dielectric and rated at 6.3 Vdc. By applying 5 Vdc, 60%v of the capacitance is lost, and the ESR declines to nearly 50% of its “0Vdc” bias ESR level. Table 3. Capacitance and ESR versus applied DC bias voltage. The combined effect of the DC bias change is shown in Figure 9, where the error is now greater than 100% and higher for impedance values below the SRF (more dependent on capacitance ) than impedance levels above the SRF (more dependent on inductance) for this device. ©Electronic Components Association, Inc., Arlington, Virginia, USA 2010 Capacitor and Resistor Technology Symposium Proceedings, CARTS Conference, New Orleans, LA, March 2010 Page 5 of 13 Figure 9. Absolute error in impedance magnitude comparing 5Vdc to 0Vdc bias conditions. The typical models prescribed by the manufacturer may include a parallel resistive element for simulating the leakage or insulation resistance of the capacitor. A series RC circuit may represent a dielectric absorption behavior of the capacitor, or a parallel resonance capacitance for the device. For KEMET (Figure 10), we have two models that we use for MLCC and film capacitors, one (on the left of Figure 10) for lower value capacitors in which the changing inductance is not significant and includes no series RL networks. The other model (on the right) which includes series RL models is very new and we are in the process of offering this alternative model for all values greater than 10 uF. Figure 10. Models used for MLCC and film capacitors. ©Electronic Components Association, Inc., Arlington, Virginia, USA 2010 Capacitor and Resistor Technology Symposium Proceedings, CARTS Conference, New Orleans, LA, March 2010 Page 6 of 13 Electrolytic Capacitors These capacitors should never be modeled as simple RLC circuits as these devices have an RC-Ladder effect in which the capacitance decays rapidly with increasing frequency. This results in a broader or flatter impedance response as it nears and holds a minimum impedance level for a longer duration. Figure 11. Capacitance versus frequency for two electrolytic type capacitors. In Figure 11, a “wet” electrolytic aluminum SMD capacitor is shown on the left, and a “dry” tantalum SMD capacitor is shown on the right. The plots represent measured capacitance versus frequency, at various ambient temperatures for these devices. Because the roll-off of capacitance shifts with temperature, the resistive elements of the RC-Ladder are changing. The net effect must represent the resistance and its sensitivity to temperature and the capacitance and its sensitivity to temperature. The capacitance change (+12% to -15%) with temperature is measured at 120 Hz, and from these plots it can be seen that the capacitance change with temperature will be much greater in higher frequencies. Two of the models we use for the aluminum and tantalum capacitors are shown below (Figure 12). The 5RC model is used for most of our capacitors and the 3RC-RL is used only for the latest, very-low ESR devices, as we can measure the changing inductance. Figure 12. Two model circuits for aluminum and tantalum capacitors containing the RC-Ladder. Using the simple RLC circuit and the capacitance, ESR, and ESL at 100 kHz for a T495V477M006 capacitor, creates the error plot of Figure 13. The capacitance error drops to 0% at 100 kHz, but this is the only frequency where that ©Electronic Components Association, Inc., Arlington, Virginia, USA 2010 Capacitor and Resistor Technology Symposium Proceedings, CARTS Conference, New Orleans, LA, March 2010 Page 7 of 13 capacitance (~170 µF) is valid. The low frequency impedance has an error greater than 100%, as the capacitance in this region is closer to nominal (470 µF). Because the impedance continues to decline above the 100 kHz frequency, the capacitance error gets even higher in this region. Figure 13. Simple RLC Error plot based on 100 kHz data. Using the 500 kHz readings to set the RLC elements, the capacitance is ~47 µF at 500 kHz (Figure 14). Now the impedance error is much larger in the low frequency realm than the impedance error in the high frequency realm. Once again, the only accurate point for the capacitance is at 500 kHz, the element frequency. Figure 14. Simple RLC Error plot based on 500 kHz data. Using the 5RC model and the data collected at 100 kHz, the plot shows an impedance error below 20% throughout the frequency spectrum (Figure 15). The capacitance error is below 20% throughput the spectrum, with a peaking of 20% near the point of resonance for this device. Since ESR in this model is only factored as the capacitance decays, the error for the ESR below 30 kHz and above 2 MHz is above the desired 20% window. ©Electronic Components Association, Inc., Arlington, Virginia, USA 2010 Capacitor and Resistor Technology Symposium Proceedings, CARTS Conference, New Orleans, LA, March 2010 Page 8 of 13 Figure 15. Error plot for 5RC model using 100 kHz data of T495V477M006 device versus measured. Using the 500 kHz data to set the 5RC elements does not appear to improve the accuracy of the results comparing the model to the actual data. The impedance error is smaller in the low-frequency region, but higher in the mid-frequency region. Figure 16. Error plot for 5RC model using 500 kHz data of T495V477M006 device versus measured. In any case, the 5RC model shows that the impedance conforms to the 20% window, whereas the simple RLXC model shows unacceptable performance. For tantalum capacitors with lower capacitance, smaller sizes and much higher ESR values, a 9RC model is used as the capacitance declines over such a long frequency period. For some of the latest “low ESR” devices, the capacitance declines very little before the SRF is encountered, allowing only a 3RC ladder design. For some of these very low ESL designs, it is critical for the signal integrity group to model the impedance near SRF as closely as possible, including any decay of ESL from the SRF up to 100 MHz. In the following plot of a T528Z477M2R5ATE005RL150pH device with 5 milliohms of ESR and an ESL of 150 pH, the simple RLC model created with data read at 500 kHz shows the typical near perfect correlation to the actual ©Electronic Components Association, Inc., Arlington, Virginia, USA 2010 Capacitor and Resistor Technology Symposium Proceedings, CARTS Conference, New Orleans, LA, March 2010 Page 9 of 13 readings only at 500 kHz. The capacitance error is near 100% in the lower frequencies and near 1000% in ht e upper frequencies. The impedance error is close the capacitance error in the lower frequencies, but because the capacitance is a minor reactance in the upper frequencies, the error in impedance is diminished. Figure 17. A simple RLC model using the 500 kHz reading for a T528Z477M2R5ATE005 device. Using the 3RCRL model the impedance error is now a maximum of 4% throughout the entire frequency range. The capacitance error is below 10% over this entire range also. Again, the ESR in the lower frequencies has no frequency component and its error is approaching 100%, but in the higher frequency range, the RL network does create a frequency controlled ESR, and its error is maintained close to the 20% limit. Figure 18. The error response for the 3RCRL simulation of the T528Z477M2R5ATE005 device. Earlier we showed the impact of changing temperature for the MLCC. The changes with temperature are compounded in the electrolytic capacitor because the roll-off is factored by both changes in capacitance and resistance. In Figure 19, the impedance generated by the 5RC model with seed values at -55°C, +25°C, and +85°C is very close to the actual ©Electronic Components Association, Inc., Arlington, Virginia, USA 2010 Capacitor and Resistor Technology Symposium Proceedings, CARTS Conference, New Orleans, LA, March 2010 Page 10 of 13 measurements. Figure 20 shows the deviation of the temperature extremes to the 25°C reference as a percentage error, which is much larger than that for the MLCCs shown earlier (Figure 8). Figure 19. Changing impedance with temperature dependent seed values in 5RC. Figure 20. Percent error of 5RC Impedance at temperature versus impedance at 25°C. EDA Models [3] On the KEMET web site, there is a page dedicated to a listing of created models. These models are collected in common groups (style, size, dielectric, etc.) and compressed into ZIP files. These can be downloaded and used in several EDA software versions that allow importing subcircuit entities. These models were all created at 25°C, with no DC bias – just like every other manufacturer. You can also download the KEMET Spice [4] software which has a capability for creating models at a specific temperature, with a specific DC bias. You can create an entire family of models for specific EDA software, from the ©Electronic Components Association, Inc., Arlington, Virginia, USA 2010 Capacitor and Resistor Technology Symposium Proceedings, CARTS Conference, New Orleans, LA, March 2010 Page 11 of 13 list as shown in Figure 21. Once the type is selected, you decide what capacitor types are to be included, and the temperature, voltage, and frequencies. Figure 21. KEMET Spice model export capability. Creating these models is a capability built into the KEMET Spice software. For the entire surface mount product listing in this software (aluminum-polymer, ceramic, film, and tantalum, tantalum-polymer), these models can be exported in several formats. Figure 22. Customizing the models temperature, bias, frequency, and types. After the model type is selected, the user then has the capability of creating models for unique temperature, bias, and frequency conditions. The user may also restrict the part types from which the models are created. In Figure 22, the selection is restricted to 0201 through 1206 MLCCs, T495, T510, T520, and T525 part types. For each set of conditions, the models may be directed to specific directories. ©Electronic Components Association, Inc., Arlington, Virginia, USA 2010 Capacitor and Resistor Technology Symposium Proceedings, CARTS Conference, New Orleans, LA, March 2010 Page 12 of 13 Simple Models versus Computation Time The one complaint that we’ve heard when we talk about more realistic models with higher element counts is that because there may be tens of these capacitors in parallel in several locations, the higher element count in these passive models will slow down the response and extend the computational time for the circuit. There is a solution. Consider a microprocessor decoupling scheme in which twenty-two 0805 ceramic chip capacitors are being used for power decoupling. Adding twenty-two networks to the analysis can be avoided by combining these twenty-two devices into a singular or reduced count circuit. The simplest factor would be to build a single model for the twenty-two capacitors. The main capacitance (C1) of the single model (Figure 23) might be 19.71 uF (at 1 MHz), and add 22 of these 7element networks to the circuit, or add the capacitance of the twenty-two (484 uF at 1 MHz) and this becomes the main capacitance (C1) of a single 7-element model circuit. Some may argue that in this application, the ESLs and ESRs from each capacitor to the power planes are different. In this case you could add three networks (one of 10 capacitors, one of 7 capacitors, and the last of 5 capacitors) thereby reducing the network count from 22 down to three. Each of the three would have different ESRs and ESLs in series with the networks to compensate for the different path lengths of these groups. The KEMET Spice software allows you to define the external ESR and ESL, and multiples of any of the capacitors. Any circuit with multiple capacitors would have a number centered in brackets (e.g., “C0805C226K9PAC[22].ckt”). Figure 23. Creating a singular model circuit for multiple capacitors. Bibliography [1] J. Prymak - KEMET Electronics Corp., “SPICE Modeling of Capacitors”, CARTS 1995 Proceedings, Components Technology Institute, Inc., March 1995 [2] J. Prymak, Long B, Prevallet M. - KEMET Electronics Corp., “KEMET Spice – An Update”, CARTS 2004, Components Technology Institute, Inc., March 2004 [3] J. Prymak - KEMET Electronics Corp., “KEMET Spice Software shows response for multiple capacitor filters”, Arrow Asian Times, April 2007 [4] KEMET S-Parameter, NetList, Cadence, Ansoft, Mentor, Sigrity, Simplex, Touchstone models and files (http://www.kemet.com/kemet/web/homepage/kechome.nsf/weben/kemsoft#netlist) [5] KEMET Spice, Version 3.7.43, ©1998-2010 KEMET Electronics Corp., Greenville, SC 29606 (http://www.kemet.com/kemet/web/homepage/kechome.nsf/weben/kemsoft#) [6] Prymak, Blais, Buchanan, Chen, Lai, Malagoli, Mayar, Niskala, Schmidt, Staubli, Vildaver - KEMET, “Generating Capacitor Spice Models with Compensations for Frequency, Temperature, and DC Bias”, Virtual CARTS Europe, http://ec-central.org/CARTSEurope/2009/virtual/index.html, November 2009 ©Electronic Components Association, Inc., Arlington, Virginia, USA 2010 Capacitor and Resistor Technology Symposium Proceedings, CARTS Conference, New Orleans, LA, March 2010 Page 13 of 13