IMECNEWSLETTER

SEEDS FOR TOMORROW’S WORLD: IMECNOLOGY

N° 36 - July 2003

IMEC provides novel post-processing

techniques for cost-effective high-Q inductors

Research in the domain of mobile

communication services and

portable wireless electronics

focuses on smaller size and

weight, higher bandwidth and

lower power consumption. To

achieve such low-power, lownoise, and high-bandwidth

portable applications, miniaturization and integration of passive

components is required. This

remains problematic since many

passive components cannot be

integrated cost-effectively with

sufficient quality or size on the

same Si die. This also applies to

inductors: conventional on-chip

inductors show low quality factors

(Q, typically 5 to 10).

IMEC has developed a novel technique for the realization of induc-

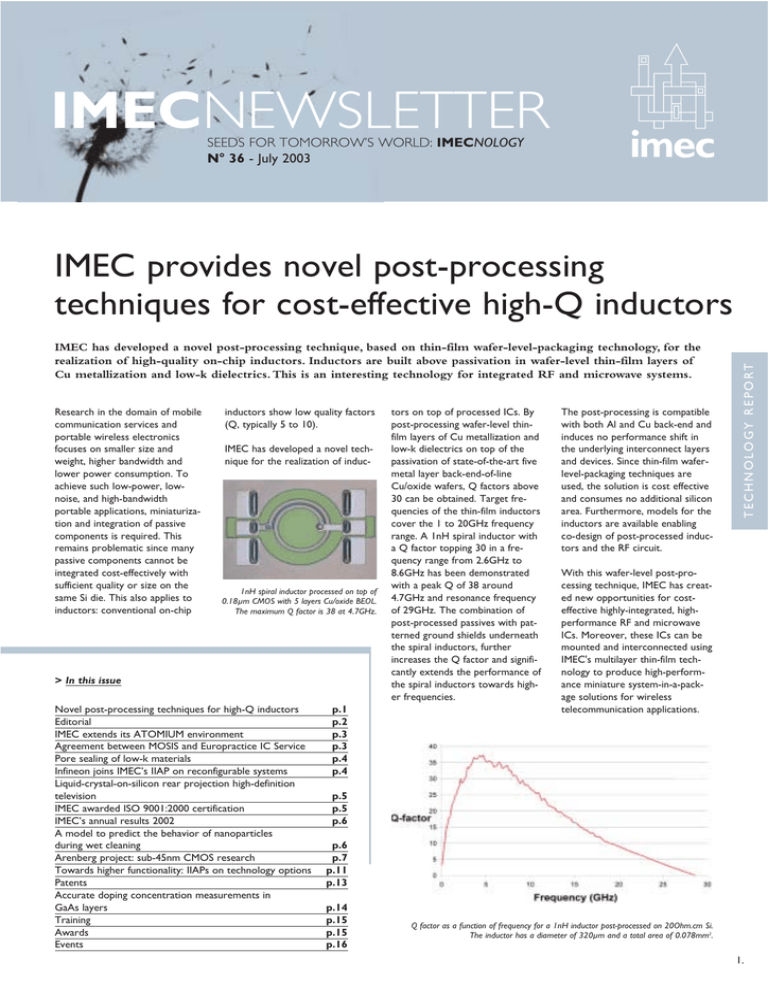

1nH spiral inductor processed on top of

0.18µm CMOS with 5 layers Cu/oxide BEOL.

The maximum Q factor is 38 at 4.7GHz.

> In this issue

Novel post-processing techniques for high-Q inductors

Editorial

IMEC extends its ATOMIUM environment

Agreement between MOSIS and Europractice IC Service

Pore sealing of low-k materials

Infineon joins IMEC’s IIAP on reconfigurable systems

Liquid-crystal-on-silicon rear projection high-definition

television

IMEC awarded ISO 9001:2000 certification

IMEC’s annual results 2002

A model to predict the behavior of nanoparticles

during wet cleaning

Arenberg project: sub-45nm CMOS research

Towards higher functionality: IIAPs on technology options

Patents

Accurate doping concentration measurements in

GaAs layers

Training

Awards

Events

p.1

p.2

p.3

p.3

p.4

p.4

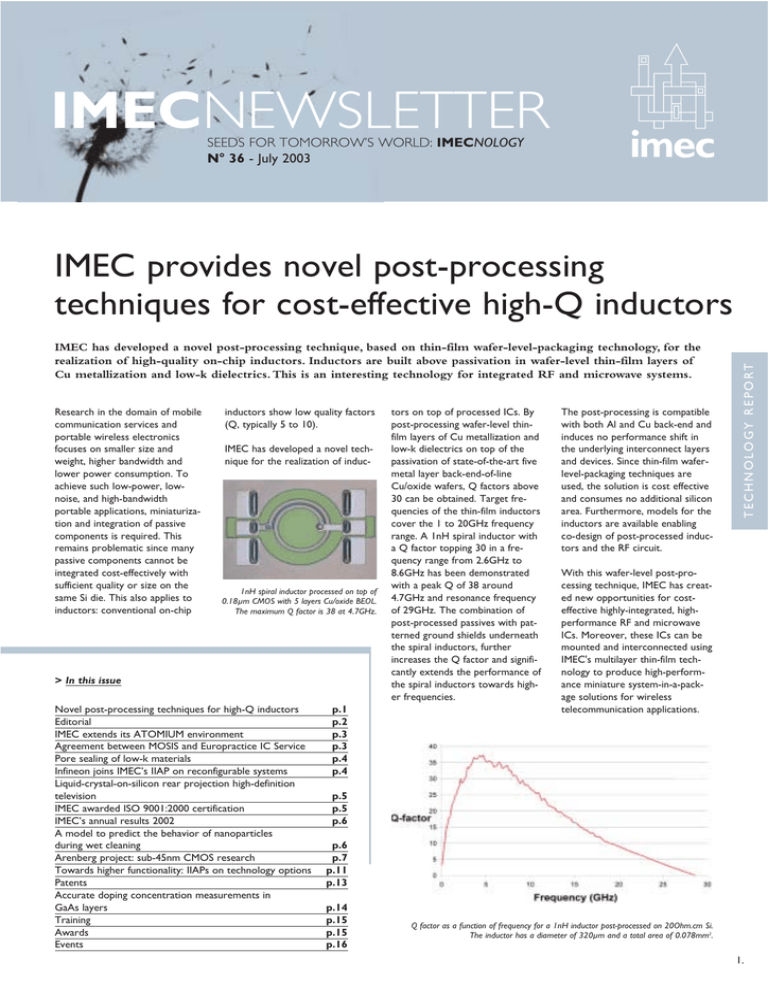

tors on top of processed ICs. By

post-processing wafer-level thinfilm layers of Cu metallization and

low-k dielectrics on top of the

passivation of state-of-the-art five

metal layer back-end-of-line

Cu/oxide wafers, Q factors above

30 can be obtained. Target frequencies of the thin-film inductors

cover the 1 to 20GHz frequency

range. A 1nH spiral inductor with

a Q factor topping 30 in a frequency range from 2.6GHz to

8.6GHz has been demonstrated

with a peak Q of 38 around

4.7GHz and resonance frequency

of 29GHz. The combination of

post-processed passives with patterned ground shields underneath

the spiral inductors, further

increases the Q factor and significantly extends the performance of

the spiral inductors towards higher frequencies.

TECHNOLOGY REPORT

IMEC has developed a novel post-processing technique, based on thin-film wafer-level-packaging technology, for the

realization of high-quality on-chip inductors. Inductors are built above passivation in wafer-level thin-film layers of

Cu metallization and low-k dielectrics. This is an interesting technology for integrated RF and microwave systems.

The post-processing is compatible

with both Al and Cu back-end and

induces no performance shift in

the underlying interconnect layers

and devices. Since thin-film waferlevel-packaging techniques are

used, the solution is cost effective

and consumes no additional silicon

area. Furthermore, models for the

inductors are available enabling

co-design of post-processed inductors and the RF circuit.

With this wafer-level post-processing technique, IMEC has created new opportunities for costeffective highly-integrated, highperformance RF and microwave

ICs. Moreover, these ICs can be

mounted and interconnected using

IMEC's multilayer thin-film technology to produce high-performance miniature system-in-a-package solutions for wireless

telecommunication applications.

p.5

p.5

p.6

p.6

p.7

p.11

p.13

p.14

p.15

p.15

p.16

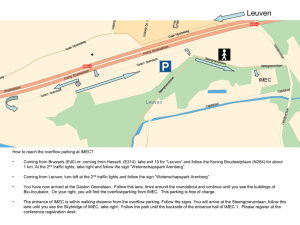

Q factor as a function of frequency for a 1nH inductor post-processed on 20Ohm.cm Si.

The inductor has a diameter of 320µm and a total area of 0.078mm2.

1.

Editorial

Colophon

Publisher

Prof. Gilbert Declerck, President

Editors

Mieke Van bavel

Phone: +32 16 288 010

E-mail: Mieke.Vanbavel@imec.be

Els Parton

Phone: +32 16 281 467

E-mail: Els.Parton@imec.be

Corporate Communication

Manager

Katrien Marent

IMEC Kapeldreef 75

B-3001 Leuven – Belgium

Phone: +32 16 281 880

Fax: +32 16 281 637

E-mail: Katrien.Marent@imec.be

USA contact

Patrick Verbist / Raffaella Borzi

IMEC, Inc.

960 Saragota Ave, Suite 206

CA 95129 – San Jose

California – USA

Phone: +1 408 551-4501/4502

Fax: +1 408 551-4505

E-mail: Patrick.Verbist@imec.be

E-mail: Raffaella.Borzi@imec.be

China contact

Teng Gao

IMEC Shanghai Office

Units C60-C66, 11/F

Shanghai Mart

2299 Yan’an Road West

Shanghai 200336 – P.R. China

Phone: +86 21 6236-0700 ext. 18

Fax: +86 21 6236-0706

E-mail: Gao.Teng@imec.be

IMEC representative Japan

Akihiko Ishitani

Phone: +81 90-5795-9108

E-mail: Akihiko.Ishitani@imec.be

Contributors

Ben Beddegenoots, Gerald Beyer, Dirk

Boghe, Rudi Cartuyvels, Matty Caymax,

Stefaan Decoutere, Stefan De Gendt, Bart

De Mey, Vic Fonderie, Wim Fyen, Johan

Haspeslagh, Marc Heyns, Katrien Marent,

Paul Mertens, Marc Meuris, Kurt Ronse, Tom

Schram, Johan Stiens, André Van Calster,

Luc Van den hove, Jan Van Houdt, Els

Vanlee and Dirk Wouters

2.

The semiconductor industry faces a research dilemma, which is not to be underestimated. The cost of research is increasing dramatically. This is due not only to

the transition from 200mm to 300mm, with the associated higher operational

costs to a large extent due to the considerably higher wafer cost. Tool costs are

also rising almost exponentially with each new technology generation. At the

same time, the need for research has never been as high. Whereas in the past the

same materials would easily support four to five technology generations, today

nearly each technology generation requires the introduction of more than one

new material. And in spite of all our extensive roadmapping activities of recent

years, the specific roadmap for the introduction of many process options is all but

Luc Van den hove

unclear (see e.g. the continuing exploration of various lithography options for

sub-65nm applications). Consequently, several process choices must be investigated in parallel, requiring a

great deal of research efforts and hence resources.

Whereas the dramatic increase of research costs and needs is obvious, financial resources to meet with

these costs and needs will soon prove insufficient. The recession in the semiconductor industry, as we have

experienced it in recent years, may well mark the transition to a period of slower growth in this industry.

Hence, the reduced revenue growth rates make it harder to provide for the steadily increasing research

budgets. Partnering for research may very well be the only way out of this research dilemma. Companies

will be prepared to share the cost of research, as they are under constant pressure to establish and maintain product differentiation in a highly competitive environment.

The decision whether to perform this advanced process research on 200mm or 300mm wafers should not

be taken lightheartedly. Nowadays, we see that development is linked to manufacturing much more closely

than before. This meets with the pressing requirement to keep reducing time and resources needed to

transition from technology development to manufacturing. Development is performed preferably on 300mm

equipment in order to facilitate the transition into manufacturing. In principle, this can be supported by

advanced device and process research on 200mm

wafers. However, timing and financial constraints

prevent suppliers from developing the most

Luc Van den hove, on the

advanced equipment for 200mm and for 300mm

concurrently, resulting in state-of-the-art equipresearch dilemma and the need

ment being available only for 300mm wafers in the

for a centralized 300mm

early phase of new tool introduction.

Consequently, advanced process research

research platform.

requires a 300mm research facility. Whereas

development facilities are being closely interfaced

with the early manufacturing sites, it will be more

meaningful to perform research in a centralized facility serving various development organizations.

Especially, in view of contamination risks, it will be preferable not to physically link such research facility to

a development line. Indeed, as already mentioned, many new materials will have to be introduced in order

to support increasing device and interconnect performances in future technology generations, and each of

these materials constitutes a potential contamination threat.

Continuation of state-of-the-art process research also involves meeting increasingly stringent reliability

requirements. Materials and devices used in present-day microelectronics technologies are pushed to the

intrinsic limits of reliability. Moreover, new reliability challenges arise from the introduction of new materials, processes and technologies, such as high-k dielectrics, Cu, low-k dielectrics, new silicide materials, new

barrier materials a.s.o. The use of new materials and processes also will have a strong impact on the packaging reliability. It will be an enormous research challenge to maintain current reliability levels, since these

new materials and processes are introduced faster than the capabilities to understand their reliability properties and failure mechanisms. Therefore reliability studies will be an indispensable part of process development in the 300mm era.

As a result, it appears mandatory to set up an efficient operation for focused silicon technology research in

a centralized research platform. IMEC is determined to establish such a 300mm process research platform

in close collaboration with IC manufacturers as well as equipment suppliers. The activities are organized in a

set of programs, enabling very advanced research at reduced cost, targeting at any point in time technology

generations which are two to three nodes ahead of that being ramped up in manufacturing. Based on its

long-standing track record and expertise, IMEC’s core focus in these programs is on advanced process

module and device research, with several programs being devoted to the exploration of new materials.

Encouraged by numerous positive reactions from industry and from the research community alike, we

strongly believe that this is the right approach in order to untangle the research dilemma, to adequately

respond to the process challenges, to keep research affordable and to maintain the critical mass necessary

to meet with the excruciating time-to-market requirements in our industry.

Luc Van den hove, Vice President IMEC, heading the SPDT (silicon process and device technology) division

A special insert inside this Newsletter is devoted to IMEC’s centralized 300mm research platform

and the various sub-45nm CMOS research programs.

The entire content of this publication is protected by copyright, full details of which are available at IMEC. All rights reserved. No part of this

publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means – electronic, mechanical- photocopying,

recording or otherwise – without prior permission of the copyright owner.

Contact person: Katrien Marent – Phone: +32 16 281 880 – E-mail: Katrien.Marent@imec.be

IMEC extends its ATOMIUM environment

with the ‘memory allocation and

assignment’ functionality

IMEC’s new ATOMIUM/MemoryArchitect tool assists designers in optimizing the memory architecture for multimedia and telecommunications applications. This extension to the ATOMIUM tool suite (a toolbox for optimizing memory I/O using geometrical models) is the first memory synthesis and mapping tool that is able to handle complex

applications under real-time constraints.

To address this need, IMEC has

developed the ATOMIUM/

MemoryArchitect tool. It allows

designers to gain a clear insight

into memory-bandwidth costs. It

decides which data should be

accessible in parallel in order to

meet the timing constraints with an

‘as low as possible’ memory cost.

Besides translating the timing constraints into optimized architectural

The ‘memory allocation and assignment’ component of the ATOMIUM/

MA tool uses the architectural constraints to define an optimized

memory architecture for a specific

application, providing sufficient

memory bandwidth to meet the

application’s real-time constraints.

The MemoryArchitect tool accepts

the following inputs:

• the application specified in ANSIC;

• timing constraints for the application;

• a user-definable library characterizing the memory modules it can

use;

• profiling information;

• a (user-definable) assignment of

data to memory hierarchy layers.

From this input, the tool computes

the following results:

• an optimized memory allocation

for each hierarchy layer (how

many memories, how many ports

on each memory, the bit width of

each memory, etc.);

• an optimized assignment of all the

data to memory modules (which

array has to be stored in which

memory module);

• absolute cost estimates for the

memory architecture (power,

silicon area, performance,

number of memories, number

of ports etc.);

• an optimized distribution of the

available time budget over the different loops and functions of the

application.

Moreover, the MemoryArchitect

tool does not just provide a single

solution but provides a whole set

of Pareto-optimal solutions from

which the designer can choose.

This allows the designer to make

well-informed trade-off decisions

(e.g., trade off silicon area for less

power consumption).

The ATOMIUM tool suite comes

with a highly intuitive graphical user

interface with several views that

can help the designer to optimize

the memory-related aspects of the

application. The design environment is available for industrial partners in IMEC’s industrial affiliation

program (IIAP) on MPEG-4 and

SoC++.

Screenshot of the ‘memory allocation and

assignment’ functionality of the ATOMIUM/

MA tool: the assignment view shows the

different memories allocated for a memory

partition and how the data have

been assigned to them. It allows for very

easy identification of causes of inefficiency,

such as bit-width and/or word-depth waste,

‘hot’ data structures allocated to a large

memory etc.

TECHNOLOGY REPORT

Current state-of-the-art memory

synthesis and mapping is based on

ad-hoc methods to arrive at a

memory architecture. The lack of a

formalized methodology and tool

support restricts designers in

exploring the range of solutions

available. Much better results could

be obtained with tools that support

these design steps.

constraints, it also gives cost estimates for the resulting architectures.

ATOMIUM/MemoryArchitect has

been successfully applied on an

MPEG-4 video encoder and

decoder, a wavelet image compressor, a turbo decoder, and other

multimedia and telecommunication

applications.

INDUSTRY LINK

In data-dominated applications, typically found in the multimedia and

telecom domain, the system cost

(in terms of power consumption

and area) and performance is largely determined by data storage and

transfer. To obtain high-performance and low-cost implementations

of these applications, the memory

architecture has to be optimized.

Agreement between MOSIS and Europractice IC Service

Europractice IC Service has reached an agreement with its US counterpart, MOSIS, to

expand their prototyping service with AMI Semiconductor (AMIS) technology.

Europractice IC Service, the

European provider of low-cost, fast

prototype services and small-volume production, coordinated by

IMEC, already offers the 0.7µm I2T

100V process of AMIS Belgium to

its customers, while MOSIS offers

the C5F 0.5µm mixed-signal

process with maskless electrically

erasable progammable read-only

memory (EEPROM) option. Under

Europractice multiproject wafer.

the new agreement, customers of

both IMEC and MOSIS will have

access to both AMIS technologies,

through their local multiproject

wafer (MPW) service.

US costumers may send their

designs to MOSIS to be processed

in 0.7µm I2T 100V CMOS, a highvoltage technology for automotive,

smart power and medical applica-

tions, for processing by IMEC on

its MPW runs. In the same way,

customers of IMEC’s Europractice

IC Service may benefit from this

collaboration by sending designs to

be processed in the C5F 0.5µm

maskless EEPROM technology to

IMEC, for processing by MOSIS.

For Europractice IC Service, the

cooperation with MOSIS on both

technologies will facilitate access to

a much broader customer base and

will enhance the MPW offer.

3.

Pore sealing of low-k materials

Gerald Beyer, program manager of IMEC’s industrial affiliation program on Cu/low k,

reviews the importance of pore sealing of porous low k materials and the various

efforts that IMEC has made in this field.

INDUSTRY LINK

VIEW POINT

used to the

solidity of oxide,

now have to deal

with the high diffusivity of precursors, solvents, and last

but not least,

moisture in the

porous materials,

all of which are

detrimental to

the performance

and reliability of

the interconnect.

As early as

Semicon Europe

2001, Karen

Maex, IMEC felTime-dependent dielectric breakdown of a porous low-k matelow, pointed out

rial (k=2.3), integrated with the conventional porogen burnthat pore sealing

out and the post-etch porogen burn-out (PEBO) (International

Interconnect Technology Conference (IITC) proceedings 2003).

is key to obtaining acceptable

dielectric reliabilThe introduction of low-k materi- ity performance for porous low-k

als is driven by power-consumpfilms. Since then, IMEC has piotion issues of advanced interconneered methodologies to characnects. Today it is recognized that

terize the integrity of the sealing

dielectric materials with a dielecapproach, such as the HF-dip

tric constant below three are

method to decorate sealing

porous to some degree. In the

defects or ellipsometric

ultra-low-k materials, porosity

porosimetry to obtain a quantitamay constitute 40% or more of

tive measure of the sealing

the volume of the material.

defects on a wafer. These methTherefore, integration and reliaods were validated by dielectric

bility engineers, who have been

reliability measurements and were

The first attempt at pore sealing

was the deposition of a rather

thick, dense dielectric liner over

the surface of a porous

silsesquioxane (SSQ) material.

Even though this approach is difficult to integrate in sub-100nm

wires - the wire cross-section is

significantly reduced and the etch

back of the liner is critical in dualdamascene structures - it allowed

us to study the impact of pore

sealing on leakage and dielectric

breakdown of damascene structures. Since then, a number of

pore-sealing methods have been

identified and are being explored

in IMEC’s advanced interconnect

affiliation program.

Today, one of the most promising

approaches to pore sealing of

low-k dielectrics using a porogen

technology, is to create porosity

not prior to dielectric etch but

after it. This approach, which is

termed ’post-etch porogen burnout (PEBO)’, avoids the formation

of open pores at the sidewall.

The method allows scaling of the

thickness of the PVD barrier to

reach a high dielectric reliability

lifetime, under user conditions,

approaching the intrinsic reliability

properties of the porous low-k

material.

In the subtractive sealing method,

the surface of a porous material is

reconstructed under the influence

of a plasma or radiation such that

a densification of the surface is

achieved. Control of the plasma

or radiation is critical in order to

limit the densification to the first

few nm of the surface.

Gerald Beyer.

In the additive approach, the clogging of pores is pursued by the

formation of self-assembling

monolayers.

Infineon joins IMEC’s industrial affiliation proInfineon, one of Europe’s largest semiconductor companies, has joined IMEC’s industrial affiliation program (IIAP)

that focuses on technology for reconfigurable systems. Through this program, IMEC’s expertise in design technology

for reconfigurable systems will become available for Infineon’s future system-on-chip (SoC) platforms.

Last year, IMEC launched the

reconfigurable-systems IIAP,

focusing on design technology and

platform architectures for reconfigurable systems. More specifically, the IIAP targets the exploitation of reconfiguration to implement dynamic system behavior. It

will enable ‘software-like’ use of

4.

eventually adopted by other R&D

groups, too.

future reconfigurable SoC platforms. Such future SoC platforms

will consist of tiles containing

combinations of application-specific components, various types of

instruction-set processors, fineand coarse-grain reconfigurable

hardware, and memories, which

will communicate through an on-

chip network. On these

platforms, various tasks will be

created dynamically either in software or hardware and relocated

at run-time from software to

hardware and back. In this way,

the requested quality-of-service

(QoS) of the various simultaneously running applications will be

guaranteed.

The IIAP therefore concentrates

on architectural exploration,

operating systems for resource

management and dynamic task

relocation, modeling of dynamic

system behavior and optimal mapping of dynamic applications on

Liquid-crystal-on-silicon rear projection

high-definition television

IMEC’s associated laboratory INTEC (Ghent University) has developed a large-area high-definition television (HDTV)

prototype, based on liquid-crystal-on-silicon (LCoS) technology. The HDTV-LCoS system stands out, with its low

production cost and high resolution.

The LCoS technology relies on

the direct application of liquid

crystal on CMOS driver chips. To

this end, a 0.7’’ wide extended

graphics array (WXGA) CMOS

backplane has been designed and

manufactured with an 11µm pixel

size. This backplane can operate

in native-DVD-compatible

WXGA (1280x768 pixels), as well

as in standard XGA (1024x768

pixels). In addition to developing

the LCoS chips, a digital interface

board based on a XILINX FPGA

has been designed and built,

enabling the appropriate driving

of the LCoS back-planes from

standard digital video sources. A

graphic user interface allows a

user-friendly setting of all the

light-valve characteristics. Other

associated technologies have been

developed, such as a 3µm vertically aligned liquid-crystal cell

assembly technology enabling high

contrast ratios and fast video

response. The technology uses

anorganic alignment layers. Color

management was enabled using a

3-valve configuration and a compact color management unit.

Picture of a projected DVD movie.

LCoS rear projectors promise to

be a cost-effective answer for

building compact large-area

HDTV sets. Currently, the technology is under investigation for

commercialization by a spin-off

company.

For more information:

Herbert.Desmet@UGent.be

IMEC awarded ISO 9001:2000 certification

IMEC

recently

received the

ISO 9001

re-certification, following an external audit by the Société Générale

de Surveillance (SGS). The ISO cer-

tion in 1998. The 2000 version of

tification represents an industryrecognized level of quality and

the ISO quality standard not only

service that enables companies to

focuses on the quality of the end

be confident in their decision to

product, but places greater

Order IMEC’s brochure on Nanotechnology by

partner with

IMEC.

IMEC

received

accountability on executive mansending an e-mail to Laurence.Gea@imec.be

agement’s involvement, customer

its original ISO 9001:1994 certificate for the whole of its organizasatisfaction and measurable quality

objectives in the quality system.

This certification strengthens

IMEC’s commitment to systematically evaluate and analyze the efficiency of its quality system aiming

at a continuous improvement and

an integral quality assurance.

TECHNOLOGY REPORT

To provide a cost-effective, highresolution system, IMEC’s associated laboratory INTEC has developed a large-area HDTV prototype using LCoS technology. The

basic idea is to put liquid-crystal

light valves on Si wafers, which

enable high-resolution, low-cost

miniature displays. The developed

HDTV-LCoS system is most suited for multimedia and DVD

home-theater applications.

NEWS FLASH

Today’s large-area HDTV sets,

developed for the home entertainment market, are based on

very expensive or complicated

technologies, using traditional

cathode ray tubes, liquid-crystal

displays or plasma flat screens. In

addition, users demand increasingly higher resolutions.

gramming and hardware/software

multitasking.

The combination of Infineon’s

expertise in platforms and technologies and IMEC’s programming

infrastructure assets for seamless

hardware/software multitasking in

reconfigurable computing platforms, will result in easy-to-use

heterogeneous reconfigurable systems targeting future needs.

HL

Model

Appl1

HL

Model

Appl2

HL

Model

ApplN

...

Compilation

Refinement

...

ApplN

QoSN( )

QoS-aware rescheduling of HW

and SW tasks (HW/SW migration)

Middle-ware

Multi-processor/task RTOS

ISP1

ISP2

...

ISPN

static interconnect network

ASIC

High-level modeling & mapping

Performance Modeling

Task Concurrency Management

Appl1

Appl2

QoS1( ) QoS2( )

RUN TIME

reconfigurable SoC platforms.

Xilinx Inc. became the first member of the IIAP. Infineon now is

the second organization to join

the program. IMEC and Infineon

will collaborate in developing an

optimized architecture targeted at

Infineon’s key application areas. It

will take upcoming technology

features into consideration to

serve as a platform for future

deep-submicron SoCs. Special

attention will be paid to the

architectural requirements for the

platform to enable ease of pro-

COMPILE TIME

gram on reconfigurable systems

Re-configurable

Distr.

memory

arch.

RTOS support for HW/SW

multi-tasking

Novel reconfigurable architectures

suited for HW and SW multitasking

Mission: enabling ‘software-like’ use of future

reconfigurable SoC platforms.

5.

NEWS FLASH

TECHNOLOGY REPORT

IMEC’s annual results 2002: 15% rise in

contract revenue

IMEC’s 2002 results show an increase in contract revenue

of 15%. These good results were obtained thanks to the

unique business model for cooperative research, in which

costs, talent, risks and intellectual properties are shared.

ment with the Flemish Government

for a period of 5 years.

International contract revenues

increased in 2002 by 25.5% to 50.2

million euros or 48.55% of IMEC’s

contract-generated revenue.

> Continued on p.14

A comprehensive model to predict the behavior

of nanoparticles during a wet-cleaning process

IMEC has developed a comprehensive model to calculate

the particle-removal efficiency of a full cleaning process,

i.e. cleaning, rinsing and drying. Comparison of experimental results and calculations has proved the accuracy

of the model and provided new insights into the wetcleaning process.

As device dimensions shrink, we

are moving from the micro- into

the nanosize range. As a result of

this, the negative impact of

process impurities, such as small

pieces of solid material – referred

to as nanoparticles - increases. In

order to obtain optimum device

performance after a complete

processing sequence, several

cleaning steps are performed with

the aim of removing these particles from the wafer surface. This

is usually accomplished by using

dedicated cleaning mixtures, followed by a rinsing and drying step.

Recent investigation has revealed,

however, that a highly efficient

cleaning step alone is not a guarantee for the successful removal

of nanoparticles. Indeed, once the

particles are removed from the

wafer surface, they become subjected to Brownian motion in the

cleaning tank and – because of

their small dimensions – they can

diffuse relatively far into the cleaning liquid. When the wafer is subsequently transferred to the rinsing tank, an amount of nanoparticles is transferred together with a

carry-over layer of cleaning liquid.

Depending on the rinsing conditions, particles can even redeposit

on the wafer surface. The latter

can take place, for instance, when

during rinsing a pH region is

6.

In 2002, IMEC’s contract revenue

rose by more than 15% to nearly

105 million euros. Today, IMEC

generates 76% of its total budget

(138 million euro), with the

remaining 24% funded by the

Flemish Government. In 2002,

IMEC signed a new frame agree-

reached that induces attractive

particle-surface interactions.

Furthermore, nanoparticles can

also deposit on the surface during

the drying step. Indeed, when liquid evaporation takes place during

drying, the particles in the evaporating liquid end up on the surface

as drying residues. Consequently,

the total efficiency of the cleaning

step is reduced as a result of the

redeposition of the nanoparticles

during the subsequent rinsing and

drying step.

In order to obtain an optimal

process performance of a full

cleaning sequence, IMEC has

developed a comprehensive model

that not only takes into account

the particle-removal efficiency of

the cleaning step, but also the

effect of the rinsing and drying

step. Here, three important

parameters of the model are discussed. A first one is the amount

of cleaning liquid carried over

from the cleaning tank to the rinsing tank. This amount depends on

the liquid properties (such as viscosity and surface tension) as well

as on a number of process parameters (such as withdrawal speed

and transfer time). A second

important parameter in the model

is the transition point, which specifies when attractive interactions

during the rinsing step become

possible, leading to adsorption of

nanoparticles on the wafer surface. This transition point is calculated from a number of characteristic values of the rinsing step

(such as the pH of the rinsing liquid and the boundary layer thickness of the liquid flow). A third

parameter is the amount of liquid

evaporation during the drying

step. Since the wafer can be considered as a flat plate, the amount

of evaporating liquid (per unit

wafer area) can be expressed as

an evaporated thickness. This

thickness is a characteristic value

for a particular drying step and

can be determined empirically for

each drying technique. For the

commonly used spin-drying

process, the evaporated thickness

is a few microns, while for a number of advanced drying techniques

(developed at IMEC), values of

approximately two orders of magnitude lower can be obtained.

To illustrate the applicability of

the model, SiO2 wafers were

intentionally contaminated with

a known amount of Al2O3

nanoparticles and subsequently

cleaned in dilute HF/HCl, rinsed

and dried. For this sequence, the

residual amount of Al2O3 particles was measured as a function of

the rinsing time.

Experimental and theoretical

results are plotted for a standard

(non-optimized) cleaning sequence

using water as the rinsing liquid.

Under these conditions, the

nanoparticles can redeposit on

the surface when a certain pH

range is reached during the rinsing

step. The model gives a good

description of the experimental

results. It can also be seen that

the fraction of redeposited

nanoparticles is significant. In contrast to ones intuition, a longer

rinsing time is, therefore, not necessarily better for such a process.

Based on these results, an optimization of the process was carried out by changing the pH of the

rinsing solution such that particle

redeposition during the rinsing

step was avoided. Similarly, experimental and theoretical results are

plotted for the optimized process

sequence. In this case, the model

also provides a good description

of the experimental results and

clearly shows the improvement in

process performance that has

been obtained. Additionally, the

model can be used to correlate

this information with the process

parameters discussed above. In

this way, the number of experiments needed to develop an optimized process can be significantly

reduced.

Comparison between

experimental results and

calculations using IMEC's

model for a standard

cleaning process and an

optimized cleaning process.

Join forces in sub-45nm

CMOS research

To address the challenges in the changing research environment, IMEC decided

to establish a 300mm process research facility in close collaboration with IC

manufacturers as well as equipment suppliers. The activities are organized in a

set of programs for sub-45nm CMOS technologies, enabling very advanced

research at reduced cost, two to three generations ahead of manufacturing technology. IMEC believes that this is the right approach to untangle the research

dilemma the industry has to deal with.

Based on its interdisciplinary research in the domains of systems-on-a-chip and

of systems-in-a-package (both from the systems and from the technology point

of view), IMEC clearly has the skills and assets to extend current CMOS technology with extra functionality. In due time, this will allow broadening the focus and

activities at the 300mm Si research platform from the scaling of feature sizes

towards the combination of heterogeneous technologies.

Research will be performed for technology nodes at least two generations ahead

of industrial needs (“N+2” and “N+3”) and will be aligned with - and possibly

even ahead of - the overall timing and objectives of the international technology

roadmap for semiconductors (ITRS).

In line with industry’s transition, the tool set for the execution of these

programs will gradually transition from 200mm towards 300mm.

"Advanced Si Research Platform"

"N+3"

"N+2"

"N+1"

"N"

Manufacturing

Research

Research

Development

Device exploration

Device optimization

Process integration

IMEC programs

2004

2007

32nm

22nm

45nm

32nm

65nm

45nm

90nm

65nm

Timing of the advanced Si research platform activities. Technology node “N” refers to the

technology generation ready for volume production ramp-up. The grey area represents IMEC’s

scope of advanced research in process modules and devices. When industry is ramping up a

process of technology node “N” for volume production, industrial pilot lines focus on development of the next technology node “N+1” and the research environment should concentrate

its efforts on process modules and devices for the “N+2” node and beyond.

The new research facility will be located adjacent to the current IMEC facilities

in order to share human resources (skills and know-how), infrastructure and

metrology tools.

Key features

• Very flexible research fab:

- clean room: 2200m2 ball room concept;

- FOUP wafer transport with mini-environments (300mm SMIF);

- 3-level clean room with fab level for process equipment, sub-fab level for

supporting equipment, lower level for utilities.

• Ultra-short cycle time:

- fully single wafer (wherever possible);

- full continuous operation (24hrs/7days).

• State-of-the-art processing equipment including the world’s most advanced

litho clusters.

> How to join IMEC’s sub-45nm CMOS research programs?

The IMEC industrial affiliation program (IIAP) is IMEC’s premium R&D cooperation formula for joint R&D between industrial researchers and IMEC research

teams focused on a specific topic or technology area. Each industrial partner

joins the IIAP research program on a bilateral basis, with clearly defined technical

scope and deliverables, allowing the partner to tune the program to its industrial

needs.

Customized programs can be defined and executed by the industrial partner

who therefore makes use of IMEC’s facilities. IMEC supports the research

activities of the industrial partner via personnel and its know-how.

Potential partners are semiconductor manufacturers, software providers,

equipment suppliers and material suppliers.

7.

Explore IMEC’s

(sub-)45nm programs

Lithography

157nm

&

high-NA

193nm

Substrate modules

High-µ

USJ

Silicides

Gate stack

High-k

Strained Si

SiGe

Advanced

Interconnect

Ultra

low-k

Metal

gate

Alternative Devices (Emerald)

EUVL

UCP

Wafer

Level

Packaging

Ge-based devices

Core CMOS programs

NVM - Flash

BiCMOS

FeRAM

Technology options

> Lithography programs: 157nm and Extreme-UV patterning

The main target of the lithography programs is to provide patterning solutions

for the critical 45nm- and 32nm-node layers. The programs are centered on the

world’s first full-field lithography tools (delivered by ASML through a strategic

partnership) for each generation. In these programs, various projects are being

executed in the areas of: resist process characterization and benchmarking;

detailed imaging characterization; research on optical extension techniques; reticle characterization (including pellicle solutions) and in-situ and in-line metrology.

These programs will build upon the background that IMEC has developed

over the past 10 years. Similar programs on 248nm and 193nm patterning

were completed successfully.

IMEC breakthroughs on the 193 patterning program:

• line-edge-roughness characterization and reduction;

• investigation of advanced imaging techniques;

• achievements on critical-dimension (CD) metrology;

• exploration of optical-extension techniques.

ASML delivers first full-field 157nm tool to IMEC

ASML Holding NV (ASML) has delivered the industry’s first full-field 157nm

step-and-scan tool to IMEC. The new system, called the Micrascan VII, is the

first 157nm full-field tool able to create working chips. Tests at ASML’s facility in Wilton, Connecticut, have already demonstrated the exceptional quality

and capabilities of the tool. This

shipment plus orders from other

customers will advance the

development of 157nm technology.

> Implementation of high-k dielectrics and

metal gates in scaled planar devices

The goal of this program is to build up fundamental understanding and to provide solutions for the implementation of high-k materials and metal gates into

scaled planar devices for sub-45nm technologies. Equivalent-oxide-thickness

IMEC breakthroughs:

• development of atomic-layer-deposition (ALD) techniques and fundamental

understanding of atomic-layer chemical-vapor-deposition (ALCVD) and

metal-organic CVD (MOCVD) growth;

• improvement of high-k layer formation and the study of interface growth

and reduction;

• development and benchmarking of various characterization techniques;

• identification of the need for higher-k dielectrics for sub-1nm EOT targets;

(EOT) levels ranging from 1nm towards 0.5nm (requiring materials with higher k

values than provided by the currently considered Hf-based materials) and both

single and dual metal-gate options will be investigated.

• model development;

• understanding of mobility issues;

• study of compatibility and implementation of high-k materials with poly-Si

gate electrodes;

• exploration of metal-gate electrodes;

• development of processes for the fabrication of short-channel transistors

with etched metal gates, and of gate last process (cold processing).

High-k dielectrics and metal gates: 0.8nm-EOT nMOS and pMOS transistors demonstrated with HfO2 and TiN metal gate

by metal gates allows a further improvement in device performance by avoidThe aggressive scaling of advanced devices has placed a high priority on finding

ing poly-Si depletion that reduces the equivalent inversion capacitance.

a suitable high-k gate dielectric. These materials are needed because they proUsing TiN gates and HfO2 as dielectric, aggressive scaling down to 0.8nm

vide the required specific capacitance at a considerably larger physical thickequivalent oxide thickness (EOT) was demonstrated in both nMOS and

ness than SiO2, thus allowing reduction of the gate leakage current by suppMOS transistors. Results showed a large reduction in leakage current.

pression of direct tunneling. Replacing the commonly used poly-Si electrodes

8.

Excellent nMOS and pMOS device performance was demonstrated. The

threshold voltage of both devices was close to the expected ideal values,

indicating a low charge density in the film and a good control on the gate

metal work function. Compared to their counterpart devices with poly-Si

gates, a significant improvement in electron and hole mobility was observed.

The instabilities due to trapping were strongly reduced as compared to typical results on high-k films with poly-Si electrodes, bringing the long-term performance of these gate stacks close to the ITRS roadmap specifications.

These results demonstrate the potential of high-k dielectrics and metal gates

for sub-1nm EOT scaling.

Gate leakage vs EOT

of TiN/HfO2 stack as

compared to poly-Si/SiO2.

> Emerging CMOS devices for future technology generations (EMERALD)

The EMERALD program studies CMOS architectures with better scaling properties than traditional bulk devices for the 45nm generation and beyond. The activities focus on two specific device concepts: fully-depleted silicon-on-insulator

IMEC breakthroughs:

On the MuGFET project:

• achievement of encouraging CMOS electrical results on nFETs and pFETs;

• proof of the capability to pattern 50nm Lgate and 50nm fin structures;

• optimization of the process flow in current lots.

(FD-SOI) FETs and multi-gate FETs (MuGFETs), both finFETs and triple-gate

FETs. The implementation of advanced process modules and materials into these

non-planar concepts will be investigated.

On the FD-SOI project:

• demonstration of the process capability;

• realization of a 30nm thin-film SOI with Lgate=70nm;

• achievement of a raised source/drain (S/D) by selective epitaxial growth;

• development of a spacer/replacer process;

• attainment of promising initial CMOS electrical results.

> Advanced interconnect solutions for future technology generations

The program targets novel on-chip interconnect solutions to overcome the

interconnect bottleneck, based on a collaboration between different disciplines:

design architectures, packaging and back-end-of-line technologies. This includes

research on novel ultra-low-k materials, on air-gap technology, on the fabrication

IMEC breakthroughs:

• achievements on Cu wires, including the development of ALD for barrier

deposition;

• evaluation of various low-k dielectrics, including the development of poresealing techniques;

• patterning of narrow lines and spacings by advanced lithography and their

and characterization of ultra-narrow conducting wires and on reliability characterization. Research will also be performed towards wafer-level packaging solutions that will provide global wiring functionality and high-quality passive component implementation.

evaluation; formation of sub-80nm wires and spacings by e-beam;

• setting up a database of reliability data on Cu/SiO2 and Cu/low k;

• development of new solutions to overcome the interconnect bottleneck;

• realization of on-chip wafer-level packaged interconnects and integrated

passives.

> Cleaning and contamination control for sub-45nm process technologies

In this program, various generic techniques, required for optimized cleaning

processes, will be investigated. Topics covered involve: development of singlechemistry cleaning solutions, research towards and characterization of singlewafer cleaning techniques; megasonic cleaning, the use of supercritical cleaning

IMEC breakthroughs:

• development of a cleaning roadmap towards more cost-effective,

environmentally benign and highly effective cleans;

• development and demonstration of the IMEC clean system as an

attractive alternative to the RCA-type cleans;

• study of the effects of metallic contamination and of wafer defects on

gate-oxide integrity (GOI) and establishing the importance of Si-surface

roughness on the quality of thin-gate oxides;

• exploration of various cleaning methodologies (cleaning mixtures,

solutions; fundamental studies on particle-solid interactions and metallic

contamination removal; and detailed research on metrology for contamination

and defects.

ozonated chemistries, single-chemistry cleaning, single-wafer wet cleaning;

application-specific cleans);

• development of innovative drying methods (investigation of Marangoni-type

drying, highlighting the importance of rinsing/drying in the overall cleaning

performance, development of novel drying methods for single-wafer

processing);

• development of advanced analytical methods for contamination control;

• study of nanosized particle removal using megasonic.

9.

Two new programs expand IMEC’s

sub-45nm research

> Implementation of high-mobility layers and advanced source/drain

engineering solutions in scaled planar devices

The goal of this program is to provide solutions for improved device performance by implementing strain in the transistor channel layer and advanced

source/drain anneal and silicidation technologies for the scaled planar MOS

devices. Strain can be introduced in the channel by epitaxial growth of tensile

strained Si layers on a strain relaxed SiGe buffer (SRB) layer. The introduction of

a strained Si layer may offer a potential solution to improve the carrier mobility.

The program is organized in several working packages, with activities centered

on the formation of strained Si layers on top of SRB layers (using newly developed and IMEC-patented epi-techniques); the formation of ultra-shallow and

abrupt junctions and silicides in bulk Si and strained Si/SiGe substrates; a detailed

engineering study on the effect of strain in the channel, induced by the strained

Si, but also by the other processing steps; the development of adequate characterization techniques; and device characterization and modeling.

Within this program, partners can benefit from major breakthroughs that

IMEC has already achieved in the area of

• strained Si on SiGe transistors: the development of an alternative

production technique for thin SRBs;

• ultra-shallow junctions: Ge+F+B junctions, solid-phase epitaxial regrowth

(SPER), Flash annealing, laser annealing, in-situ B SiGe;

• silicides: screening of various silicides and fundamental studies.

Breakthrough on the development of very thin SRBs:

The first type of SRBs that has been developed is the thick (several micrometer) graded SRB. These SRBs have several drawbacks, such as rough surfaces

and high production cost.

fabrication of isolation structures inside SRB layers with

high Ge contents can be avoided.

IMEC has developed an alternative production technique for very thin SRBs

(thickness <200nm). These SRBs contain a carbon doping spike in a thin,

supercritical SiGe layer. The result is a highly relaxed (> 90%), low-defect

density (1e5/cm2) layer with an extremely smooth surface (root mean square

(RMS) roughness <1nm), requiring no CMP step. With this technology,

wafers with a high-quality blanket strained Si layer can be manufactured.

Additionally, this process offers the possibility to grow the full layer stack

(SRB + strained Si) in a selective way inside windows in an isolation pattern

without deposition on the field oxide. This way, all problems related to the

This result is of valuable

importance for IMEC’s recently launched IIAP on the implementation of high-mobility layers and advanced source/drain

engineering solutions in scaled

planar devices.

Cross-sectional scanning electron microscope (SEM) picture of a facet-free SRB layer inside a shallow-trench-isolation (STI) active area (the faint vertical lines are sample-preparation artefacts).

> Germanium CMOS devices for future technology generations

The program on Ge CMOS devices will explore a Ge-based technology to fabricate high-performance CMOS transistors in a process compatible with silicon

baseline CMOS. Ge has recently regained significant interest within the semiconductor industry due to its attractive properties such as high mobility and compatibility with high-k materials. These features make Ge CMOS devices ideally

suited for high-performance, low-power circuits, with even an improved performance compared to advanced strained Si layers.

The Ge CMOS devices program targets the feasibility demonstration of fabricat-

IMEC can build on its longstanding partnership with leading Ge suppliers,

high-end wafer manufacturers and other key market players; on its track

record in Si process and device integration and on its state-of-the-art

pilot lines and analytical toolset.

ing Ge devices compatible with a state-of-the-art Si production line. These Ge

devices will include high-k materials and metal gates to obtain aggressively scaled

equivalent-oxide-thickness (EOT) targets. Ultimately, the program aims at the

fabrication of high-performance CMOS transistor structures in Ge that can be

used for future technology generations.

The program is organized around four working packages, covering Ge

substrates; process-step development; device fabrication; and modeling and

characterization.

Cross-section transmission electron

microscopy (TEM) analysis of a 10nm

HfO2 layer, deposited with an atomiclayer-deposition (ALD) technique on a Ge

surface, showing a uniform and atomically smooth interface.

IMEC, Soitec and Umicore collaborate to develop germanium-on-insulator technologies for the (sub-)45nm node

10.

IMEC, Soitec and Umicore have joined forces to help overcome the scaling

challenges for sub-45nm device geometries identified in the international

technology roadmap for semiconductors (ITRS). Through a groundbreaking

collaborative agreement, the three companies will enable both fabrication of

germanium-on-insulator (GeOI) substrates and development of semiconductor devices on these substrates.

wafer. IMEC will leverage its extensive knowledge of high-k materials, metal

gates, device development and characterization, and process integration to

develop a high-k layer deposition technique for GeOI substrates, as well as

defect inspection techniques for the completed GeOI wafers. Finally,

advanced devices will be fabricated to demonstrate the potential of GeOI

substrates for the sub-45nm node.

Each participant in this collaborative effort will contribute state-of-the-art

technological expertise in its respective arena, sharing data and findings

throughout the process. Umicore, which has a solid background in the commercialization and development of germanium substrates, will be responsible

for the production of the crystalline germanium wafers. Soitec will apply its

expertise in fabrication methodology, using its proprietary Smart Cut™

process to transfer a germanium layer from these wafers to form a GeOI

IMEC will incorporate the findings of this joint work into its recently

launched industrial affiliation program targeting development of a Ge-based

technology to fabricate high-performance CMOS transistors, using process

steps compatible with a state-of-the-art IC manufacturing environment. The

resulting technology solution is expected to enable the industry to achieve

the manufacturing requirements for the 45nm technology node and beyond.

In addition to IMEC’s core CMOS programs, IMEC presents three industrial affiliation programs (IIAPs) aimed at developing next-generation technology options: Flash memory program, BiCMOS process integration and

INDUSTRY LINK

Towards higher functionality:

IMEC’s industrial affiliation programs

on technology options

MOCVD-deposited ferroelectric films for scaled FeRAM. These options

will initially be implemented in the 130 or 90nm technology nodes.

> Flash memory program

Because of the finite limit that is reached for further tunnel oxide scaling

below 8-10nm, erase (and also programming) voltages are no longer being

scaled in the case of conventional floating gate Flash and electrically erasable programmable read-only memory (EEPROM) technology. Consequently,

the periphery becomes relatively larger, which increases cost and decreases

performance. In the case of stand-alone memory, this evolution has led to

the combination of a full HV CMOS process being integrated with the Flash

module (no longer containing true low-voltage CMOS). For the case of

embedded memory, the situation is even more severe because these applications require a reasonable degree of CMOS compatibility by definition.

Therefore, alternatives for conventional tunneling- and hot-carrier-based

Flash memory are needed and are already emerging today for the 90 and

the 65nm nodes. Basically, three approaches are possible: (1) pushing out

the limits of conventional Flash memory; (2) the evolutionary approach:

exploring alternative concepts aiming at eventual (and partial) replacement

of Flash and EEPROM memory in some specific applications, or (3) the rev-

IMEC breakthroughs:

• IMEC has developed a failure rate model that is able to predict the

anomalous charge loss behavior in Flash memory, independent of the

cell technology or technology generation. The model has been applied

to data from different IDMs creating a unique modeling platform with

a high level of confidence.

• IMEC was the first to process memory cells using an engineered barrier with high-k layers for fast tunneling at low voltages, showing the

Operational 4Mbit 0.18µm HIMOSTM Flash memory circuit

IMEC has fabricated a 4Mbit Flash memory based on its 0.18µm

HIMOSTM technology. The chip contains positive and negative charge

pumps, the associated clock generators for the programming and erase

operations, 16 sense amplifiers and an address transition detection

scheme for fast random access. It further includes special test modes

that allow extensive disturb testing and the extraction of analogue information (cell threshold voltages and read currents) from the memory

array for studying cell uniformity on sufficiently large statistics.

The memory measures 10mm2 (without the I/Os) and is divided into

128 sectors of 32kbits each, which can be separately erased and reprogrammed. First measurements have indicated that the array can be programmed to positive threshold voltages in 10µs, using source-side hotelectron injection, and can be erased to negative threshold values using

the Fowler-Nordheim erase method. The used on-chip

programming/erase voltages are 9V and -6V, respectively.

Simultaneously, a poly-erase version, which is intended for low-power

olutionary approach: searching for a unified memory that replaces several

types of memory such as static random access memory (SRAM), dynamic

RAM (DRAM), read-only memory (ROM), EEPROM and Flash.

IMEC’s Flash program explores innovative non-volatile memory technology,

concepts and solutions for the 90nm generation and below, which can

replace or substantially improve the conventional floating-gate approach

(the evolutionary approach). Time-to-market has become so critical for

new generation technologies that this approach is most likely to be successful. The three main modules of the program are:

• scaling issues of Flash memory, focused on the search for novel tunnel

dielectric and interpoly dielectric layers, based on high-k materials such as

Al2O3 and HfO2;

• reliability issues, mainly low-field leakage in floating-gate Flash memory and

• exploratory research on charge-trapping devices, such as novel nitride

concepts or silicon-rich-based concepts.

fundamental feasibility of combining such a concept with sufficient

cycling endurance and retention.

• IMEC has invented two new promising nitride memory concepts that

solve the major problems of the conventional 2-bit nitride storage cell.

The breakthroughs and their underlying concepts are extensively protected by IMEC patents.

operation, is being explored as well as an interesting alternative for further downscaling of IMEC's proprietary Flash technology towards the

130nm and 90nm nodes.

The 4Mbit HIMOSTM Flash memory in 0.18µm CMOS.

> Continued on p.12

11.

> Continued from p.11

> IMEC extends its BiCMOS IIAP towards very-high-speed applications

The use of carbon in SiGe heterojunction bipolar transistors (HBTs) creates new possibilities for device engineering and performance optimization.

In the period 2001-2002, IMEC’s IIAP on BiCMOS process integration successfully demonstrated the use of carbon for device engineering towards

optimization of the low-power performance of SiGe HBTs, with state-ofthe-art low-power performance for Ft, noise figure and current-mode-logic

(CML) gate delays. Applications in the 2-5GHz range were targeted.

Integration was demonstrated on the 0.18µm CMOS platform, together

with a suite of high-quality passive components.

The future of the program is directed towards the use of carbon for device

engineering and performance optimization for very-high-speed SiGeC

Key achievements in 2001-2002

In the period 2001-2002, the main objective of the IIAP was to use carbon in SiGe HBTs for improvement of the low-power performance for

2-5GHz applications.

HBTs, with peak Ft and Fmax around 150GHz in phase 1, and 200GHz in

phase 2. The timeframe is 2003-2005. The integration will be demonstrated

on the 0.13µm CMOS platform.

The IIAP is organized in three work packages:

• NPN HBT development: bipolar-module development and optimization.

• BiCMOS process integration: integration of the bipolar module in the

CMOS baseline process.

• BiCMOS with integrated RF passives: full BiCMOS process integration

including integrated RF passive components (integrated metal-insulatormetal (MIM) capacitors and post-processed thick Cu inductors).

Partners can participate in one or more work packages.

Optical microscope

picture of the postprocessed inductor.

A differential epitaxial-base SiGeC HBT module with deep-trench/shallow-trench isolation (DTI/STI) was developed, with silicided external

base and poly-emitter. Integration was demonstrated by processing full

0.18µm BiCMOS lots with integrated high-quality MIM capacitors and

thick Cu post-processed inductors, an

optional high-Ohmic poly-resistor of

1kOhm/sq and a double poly-capacitor of

1.1fF/µm2.

The low-power performance optimization

resulted in a power reduction for CML

gates with more than a factor 2 compared

with the previous generation. The low-current Ft increased with 70%, while maintaining a high peak Ft and Fmax at 60GHz and

80GHz respectively, for a breakdown voltage BVceo > 3.0 Volt. The increased Ft at

low current densities provides the designer

with higher gain at the current densities

typically used in low-noise amplifiers

(LNAs), voltage-controlled oscillators

(VCOs) and mixers.

Key activities in 2003-2005

An HBT module for very high frequencies

will be developed and integrated on a

0.13µm CMOS platform. Focus of the program is on advanced lithography for emitter window definition, improved isolation from a low-temperature DTI module with low collector-to-substrate capacitance and

steep buried layer n-type profile,

Cross-sectional SEM of

SiGeC HBT with DTI. TEM

of emitter/base region.

dielectric layer deposition with very low thermal budget, and aggressive

SiGe:C profile engineering. The HBT module will be integrated in an

analog CMOS platform with 5 layers of Cu/oxide back end, and extended with MIM capacitors and post-processed inductors.

> MOCVD-deposited ferroelectric films for scaled FeRAM

The integration of ferro-electric memories with deep sub-micron technologies is an interesting option for on-chip non-volatile memories. Their lowvoltage operation, fast programming speed and high write endurance make

them very attractive for use in portable embedded systems such as smartcards and ID tags.

Activities on ferro-electrics at IMEC focus mainly on two issues: ferro-electric material development and FeRAM integration process development.

12.

Until now, two main ferro-electric material systems have been investigated:

PZT (lead-zirconate-titanate) and SBT (strontium-bismuth-tantalate).

Both materials have their benefits and drawbacks. For memory operation,

SBT is favored because of its superior reliability characteristics such as low

fatigue and imprint. However, for memory fabrication, PZT has the advantage of lower film-formation temperature. Indeed, for applications such as

embedded memory in scaled CMOS technologies, the thermal budget

required for the crystallization of SBT films has to be decreased.

> Continued from p.12

Recently, IMEC began exploring a promising new material, BLT

(= lanthanum-substituted bismuth titanate), which shows excellent

reliability characteristics, similar to SBT, but with lower forming

temperature compared to SBT. So, BLT could be a possible replacement

material for SBT in future technologies.

On the other hand, the higher processing temperature of SBT is due partly

to the typical two-steps process used for its formation, i.e. low-temperature deposition as an amorphous film followed by a high-temperature crystallization anneal. Indeed, low (~600°C)-temperature deposition of SBT in a

one-step process has been demonstrated before.

The currently proposed affiliation program will focus on the development

of the deposition technology of these highly reliable Bi-containing materials,

SBT and BLT, compatible with scaled CMOS technologies. Metal-organic

chemical-vapor deposition (MOCVD) has been chosen as the deposition

technology, because of its compatibility with scaled technology nodes and

its applicability for three-dimensional capacitor fabrication. The objectives

of the MOCVD-ferroelectric materials program are (1) establishing the

BLT and/or ‘low-temperature/1-step’ SBT film-formation process and (2)

experimentally proving the feasibility of these materials for making scaled

FeRAMs. The latter includes investigation of thickness scaling, fabrication

and test of small-area BLT/SBT FeCAPs and evaluation of 3-D FeCAP possibilities (investigating the quality of sidewall material).

tion technology, IMEC is also strongly positioned to study the integration aspects of this new material in advanced CMOS technologies. The

integration tools, being compatible with Bi-based materials, allow a

state-of-the-art formation of small capacitors.

New patents granted

PATENTS

IMEC can rely on its strong experience in ferro-electric material

research on both PZT and SBT. Its recent development of the SBTMOCVD process will actively contribute to the realization of the first

objective of the program. On the basis of its experience in SBT integra-

120nm SBT-MOCVD layer deposited over etched bottomelectrode/oxygen barrier stack on W-plug contact.

Europe

• Etching of CoSi2 in HF-based solutions (EP 0750338)

• Method of fabrication of infrared radiation detectors and more particularly infrared sensitive bolometers (EP 0867702)

• A probe tip configuration, a method of fabricating probe tips and use thereof (EP 0899538)

• Method and system for multi-level iterative filtering of multi-dimensional data structures (EP 0938061)

Japan

• System for detecting a latent image using an alignment apparatus (JP 3399949)

USA

• Probe tip configuration and a method of fabrication thereof (US 6504152)

• A device for detecting an analyte in a sample based on organic materials (US 6521109)

• Apparatus and method for wet cleaning or etching a flat substrate (US 6530385)

• A high-voltage generating device, high-voltage generation methods and use of said high-voltage generating devices (US 6531852)

• A method and apparatus for testing supply connections (US 6531885)

• A method and apparatus for video compression (US 6532265)

• A device and a method for thermal sensing (US 6545334)

• Method of fabrication of a ferro-electric capacitor and method of growing a PZT layer on a substrate (US 6545856)

• Low-cost electroless plating process for single chips and wafer parts and products obtained thereof (US 6548327)

• Method for removing organic contaminants from a semiconductor surface (US 6551409)

• Flip-chip assembly process with isotropically and non-conductive adhesives (US 6555414)

• Device and circuit for electrostatic discharge and overvoltage protection applications (US 6570226)

• Method of removing a liquid from a surface of a rotating substrate (US 6568408)

• Chemically sensitive sensor comprising arylene alkenylene oligomers (US 6572826)

13.

> Continued from p.6

In 2002, IMEC had some hundred

contracts with businesses in the

Flemish region, and an important

contribution was made by SMEs,

accounting for 75% of IMEC’s partnerships in Flanders. The relative

share of the revenue from Flanders

remains high, alongside IMEC’s

strong international growth.

TECHNOLOGY REPORT

Last year, IMEC continued to build

its technology portfolio with its

IMEC’s number of employees

expanded to 1263 in 2002, including some 360 guest researchers

and industrial residents. IMEC’s

researchers work together with

international customers, on various

technological challenges, within the

framework of IMEC’s unique business model in which costs, talent,

risks, knowledge and therefore,

intellectual property, are shared.

This business model has proved

successful over the past few years.

More than ever before, businesses

must continue to invest in

research, even in times of economic uncertainty, in order to be able

to bring new products to market.

The costs of research in the semiconductor sector continue to rise

and the technological challenges

increase. By working together on

research, businesses can find profitable solutions to problems.

Accurate doping concentration measurements

in highly-doped n-GaAs layers @ λ=10.6µm

Extracting information about the doping concentration in semiconductor layers is very important for the fine-tuning

of (opto-)electronic devices. ETRO, IMEC’s associated lab at the university of Brussels (VUB), has developed an accurate model and sensor structure, necessary to achieve accurate doping concentration measurements in highly-doped

semiconductor layers.

8

Research at ETRO-VUB focuses

on the problem of optically calibrating high doping concentrations, i.e. between 1x1018 and

2x1019cm-3, in n-GaAs layers. At

high doping concentrations, it is

very challenging to find an accurate model expressing the relation between a measured parameter and the actual doping concentration. This is due to the

complication of the band structure at higher energy levels in a

multiple conduction band semiconductor. It was proposed to

exploit the optical properties of

the semiconductor close to the

resonant frequency of the free

electron oscillations. When a

laser is used to excite the semiconductor such that its wavelength λ corresponds to the

plasma wavelength of the semi4π2c2mε

conductor

λplasma ≈

q2N

(λplasma: the electron plasma oscillation wavelength ω; m, the electron effective mass; N, the doping

concentration), the transverse

magnetic (TM) or p-polarized

reflectivity coefficient becomes

very sensitive to any variation of

material and structural parameters. For the excitation of the

free electron plasma oscillations

in highly-doped n-GaAs, one can

exploit the emission spectra (911µm) of a CO2 laser.

In order to derive accurate information about the doping concen14.

own intellectual property rights as

a basis for cooperation with industrial partners. Its impressive scientific results are demonstrated, inter

alia, by the strong growth in the

number of patents filed (43) and in

more than 1150 scientific publications and conference proceedings.

More than half of this was realized

in collaboration with Flemish universities.

tration, two conditions need to

be fulfilled: first, a detailed model

needs to be derived for the optical properties of the highly doped

III-V semiconductor, and secondly, a sensitive multilayer structure

needs to be designed to measure

the optical properties. The complex-valued refractive index of the

semiconductor layer in the highdoping-concentration case needs

to be calculated based on a quantum-mechanical model taking into

account the non-parabolicity of

the central Γ-valley, the

anisotropic characteristics of the

L and X satellite valleys and the

intervalley and equivalent and

non-equivalent intravalley transitions as well as the hot optical

phonon effect. When a high concentration of electrons is optically excited, they disturb the

equilibrium distribution of the

lattice vibrations of the semiconductor, leading to the hot optical

phonon effect.

Once an advanced model has

been developed to predict the

optical properties of a semiconductor material, it is also essential to be able to design an optimal sensor structure to measure

the optical properties of a material, i.e. the doping concentration. An optimization procedure

was developed to derive the

optimal sensor structure for a

given doping-concentration

range. This optimization proce-

dure is based on the characteristics of Brewster-type modes in

multilayer structures. When one

excites a Brewster-type mode, i.e.

an optimal resonant mode of a

multilayer structure, the reflectivity completely vanishes. This zero

reflectivity minimum is very sensitive to the doping-dependent

parameters of the highly doped

semiconductor layer. This yields

linear and non-linear reflectivity

measurements of the doping concentration in specially designed

structures with accuracies of

about 0.1%. Another achievement

was the measurement of the spatial variation of the doping concentration along a semiconductor

wafer within a spatial accuracy of

about a few 100µm.

The evaluation of the semiconductor model with the existing

literature of the last 30 years on

experimental doping-concentration measurements in an optical

way, shows that the model is able

to clarify experimental results in a

consistent way, which frequently

questions the models used in the

past. Doping-concentration

errors in literature of up to 100%

could be traced. It is clear that

this model and these measurement techniques can be extended

to other III-V ternary and quaternary compounds.

For more information:

jstiens@etro.vub.ac.be

Intensity-dependent nonlinear reflection coefficients for a fixed angle of incidence

θ=40° and three different doping concentrations: n=1.18, 1.20, 1.22x1019cm-3. In all

cases the doped-layer thickness d=0.2µm, λ=10.6µm and tL=300K. The sensitivity

indicates the ratio between the accuracy of a ∆R measurement and the resulting ∆

accuracy. E.g. a ∆R measurement accuracy of 4% yields a ∆n accuracy, which is almost

40 times smaller, meaning a 0.1% doping concentration measurement accuracy.

Microelectronics Training Center: program

After three successful sessions in the past, MTC is planning a new session of the process technology course. This is being lectured by 12

renowned international experts in the field.

• Silicon processing for ULSI circuit fabrication

Scheduled at IMEC on: October 27-30, 2003

MTC will also repeat several highly successful courses:

• Unified meta-flow introduction: the grandmother of all system design flows

Scheduled at IMEC on: September 2-3, 2003

ISPSD 2002 Best Paper Award

for the paper entitled

‘Manufacturing of high aspectratio p-n junctions using vapor

phase doping for application in

multi-Resurf devices’

(International Symposium on

Power Semiconductor Devices

and ICs 2002, 4 – 7 June, Santa

Fe, New Mexico, USA).

Authors: C. Rochefort, R. van

Dalen (Philips Research Leuven)

and N. Duhayon, W. Vandervorst

(IMEC, Leuven).

For more information:

Bart De Mey

Bart.DeMey@imec.be

Tel: +32 16 281 249

www.imec.be/mtc

Rik Jonckheere has received the

2003 International Collaboration

Award from the SEMI Europe

Standards program

for providing an outstanding contribution in international cooperation of the SEMI Standards

Program.

2003 Microwave Prize of the

Microwave Theory and

Techniques Society

Since 1998, Rik Jonckheere has

led the task force on ‘Definition

of specifications (terminology) for

for the paper entitled ‘Accurate