university of cincinnati - OhioLINK Electronic Theses and

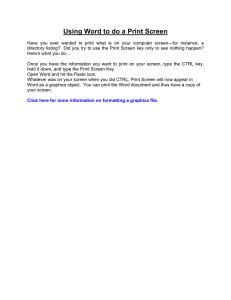

advertisement