KHAN-DISSERTATION-2014 - SMARTech Home

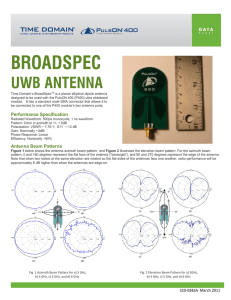

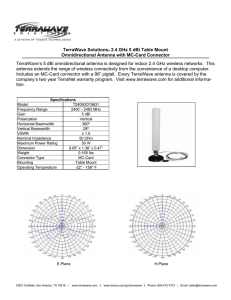

advertisement

Design and Development of Organically Packaged

Components and Modules for Microwave and MillimeterWave Applications

A Ph.D. Dissertation

Presented to

The Academic Faculty

by

Wasif Tanveer Khan

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in

Electrical and Computer Engineering

School of Electrical and Computer Engineering

Georgia Institute of Technology

December 2014

Copyright © 2014 by Wasif Tanveer Khan

Design and Development of Organically Packaged

Components and Modules for Microwave and

Millimeter wave Applications

Approved By:

Professor John Papapolymerou, Advisor

School of Electrical and Computer

Engineering

Georgia Institute of Technology

Professor Madhavan Swaminathan

School of Electrical and Computer

Engineering

Georgia Institute of Technology

Professor Andrew Peterson

School of Electrical and Computer

Engineering

Georgia Institute of Technology

Professor John Zhang

School of Chemistry and

Bio-Chemistry

Georgia Institute of Technology

Professor John Cressler

School of Electrical and Computer

Engineering Georgia Institute of

Technology

Date Approved: November 12th, 2014

II

To my beloved wife (Saira), daughter (Areebah), brother (Atif), and parents (Tanvir and

Mah Jabeen) for their unswerving faith and support

III

ACKNOWLEDGEMENTS

First of all, I would like to thank Allah Almighty for blessing me with such a

great opportunity and granting me courage and strength to achieve this milestone in my

life.

My deepest gratitude goes to my Ph.D. advisor Prof. Dr. John Papapolymerou

who, despite my rudimentary knowledge about EM tools and absolutely no experience in

cleanroom fabrication, provided me with an opportunity to work in his microwave circuit

technology (MircTech) research group in my first semester at Georgia Tech. I thank him

for showing unflinching trust in me, giving me time to learn EM tools and fabrication,

and providing me with many opportunities to work on good problems and develop some

great mm-wave components and modules. His support and guidance has helped me

become a good researcher. I have learnt a lot (design, fabrication, assembly and

measurement of mm-wave on-chip and on-package components and modules) during the

last few years.

I would like to extend my sincere thanks to my Ph.D. defense committee

Professor John D. Cressler, Professor Andrew F. Peterson, Professor Madhawan

Swaminathan and Professor John Zhan for serving on my Ph.D. defense committee and

providing me with their worthy guidance and feedback.

During my Ph.D., I was fortunate enough to collaborate with research groups

(SiGe Research group, GEMS, mixed signal design group), supervised by other

professors, which provided me some excellent opportunities to extend the horizon of my

research. I thank my advisor, Dr. John Papapolymerou, research engineer Dr. Cagri

Ulusoy, and other professors Dr. John Cressler, Dr. Hua Wang, Dr. Madhawan

IV

Swaminathan, Dr. Alenka Zajic, and research engineer Dr. Venky Sundaram for

providing me with opportunities to work on such interesting projects. While working on

these projects, I developed great working relationship with the members of SiGe, GEMS

and mixed signal design group. I would like to thank, Rob Schmid, Peter Song, Steve

Horst, Saeed Zeinolabedinzadeh, Farzad Inanlou, Seunghwan Kim, Song Hu, Taiyun Chi,

Jong Seok Park, Kyuhwan Han, Nelson Lourenco, and Srikrishna Sitaraman for their

help and collaborative work.

How can I forget my own MircTech research group members! I owe special

thanks and gratitude to all of them. I had a great time working with every one of them. I

owe a debt of gratitude to graduated members, Dr. David Chung, Dr. Arnaud Amadjikpe,

Dr. Negar Tavassolian, Dr. Yuan Li, Dr. Carlos Donado, Dr. Benjamin Lacroix, Dr.

Swapan Bhattachariya, and last but not the least Dr. Chad Patterson from whom I learnt a

whole lot about fabrication and EM tools. I would like to especially thank Dr. Chad

Patterson for taking out time and train me on cleanroom and laboratory equipment.

I would like to deeply acknowledge my current group members (Dr. Cagri

Ulusoy, Spyridon Pavlidis, Outname Lemtiri Chlieh, Aida Vera, Fan Cai, Christopher

Barisich, Sensen Li, George Alexopolis) and visiting student from France, Gaetan

Dufour, with whom I enjoyed good friendship and excellent working relationship. Their

new ideas and problems helped me reinforce my knowledge and further explore new

interesting topics. They helped me during the time of distress and made my journey

through Ph.D. a lot easier. I would cherish all my life those amazing last moments of IMS

submission deadline almost every year 5:00 am in the morning and all group lunches. I

V

would like to especially thank Dr.Cagri Ulusoy for having great discussions, ideas and

guidance.

I wish to acknowledge my sponsors Higher Education Commission Pakistan,

United States Educational Foundation in Pakistan for granting me MS leading to Ph.D.

Fulbright scholarship. It was indeed a generous award from my homeland. I would also

like to thank other sponsors of my research; Sony corporation, National Science

Foundation, and Intel Corporation. I also want to extend my sincere thanks to Dr.Anjum

Ali and Irfan Iqbal. Their worthy guidance and suggestions were very helpful in

preparing my application for graduate studies and Fulbright Scholarship.

I want to recognize the efforts of Liza Salter and Scott Sladek for taking care of

all administrative needs and cleanroom staff (especially Gary Spinner, Charlie Suh, Vinh

Tran, and Richard Shafer) for keeping cleanroom equipment up and running so we can

meet our deadlines and finish our Ph.D in a timely fashion.

I am grateful to my friends Muqarrab, Ubaid, Hassan, Minhaj, Shoaib, Ahmad

Usman, Naveed, Umar Tariq, Samee Ullah and Waseem whom company made my life

here at Georgia Tech full of life and excitement. I would never forget many east coast

and west coast trips which some of us enjoyed together.

Finally and most importantly, I would like to thank my family (wife Saira,

daughter (Areebah), brother (Atif) and my parents (Tanvirr and Mah Jabeen) for their

endless prayers and unswerving support through thick and thin. I am forever indebted to

my mother and father for their unwavering support, love and affection. On many

occasions, only my parents’ prayers gave me enough strength and confidence to

overcome obstacles. I would also like to thank my in-laws for their support and love. I

VI

highly appreciate my beloved wife’s support who endured happily all my deadlines and

sometimes odd and unusual working hours. She really was a true strength behind me.

Since I got married to her, my life has been more organized and productive. Thanks a lot

Saira for your unswerving support and unending love. During my Ph.D., Allah also

blessed us with a beautiful daughter Areebah, whose presence at home always relieved

me of my day-long tiredness and fatigue.

Without the contribution of each and every body mentioned above, it would have

been a much difficult journey. I would remember and miss all cherished moments which

I enjoyed during my Ph.D. I wish everybody best of luck for their future endeavors.

VII

TABLE OF CONTENTS

Page

ACKNOWLEDGEMENTS..……………………………………………………………

IV

LIST OF TABLES………………………………………………………………………

XII

LIST OF FIGURES……………………………………………………………………..

XIII

SUMMARY…………………………………………………………………………….

XIX

CHAPTER

1

INTRODUCTION……………………………………………………………....

1

1.1 Overview and Potential of mm-Wave Applications and Market ……...

1

1.2 Organization of the Dissertation ……………………………………....

4

PART - I

Characterization of Liquid Crystal Polymer from 110 GHz to 170 GHz

2

REVIEW OF RF SUBSTRATES AND THIER CHARACTERIZATION METHODS. 7

2.1 RF Substrates for mm-Wave Modules…………………………………...

7

2.2 Characterization of Electrical Parameters of Dielectric Materials ………

10

2.3 Material Characterization Methods………………………………………

12

2.3.1 Capacitance or Parallel Plate Method (DC to 30 MHz)………......

14

2.3.2 Free Space Method………………………………………………..

15

2.3.3 Cavity Resonators..………………………………………………..

15

2.3.4 Transmission Line Techniques..…………………………………..

16

2.3.5 Fourier Transforms Infrared Spectroscopy (1 to 100 THz)…...…..

17

2.3.6 THz Time Domain Spectroscopy (TDS) (0.1 THz to 10 THz)…...

17

2.4 Challenges in the Characterization of LCP in the D-band and

3

Proposed Method………………………………………………………….

17

CHARACTERIZATION OF LCP FROM 110 TO 170 GHZ……………………..

19

3.1 Extraction of the Relative Permittivity……………………………………

20

3.2 Extraction of the Loss Tangent and Investigation of the Radiation Loss…

22

3.2.1 Total Loss Calculation……………………………………………...

24

3.2.2 Conductor Loss Calculation………………………………………..

24

3.3 Fabrication and Measurements…………………………………………….

27

SUMMARY PART I………………………………………...……………………

31

VIII

PART - II

Design and Development of on-chip and Antenna-in-Package Solutions

for mm-wave Applications

4

DEVELOPMENT OF ANTENNA-IN-PACKAGE SOLUTIONS ON ORGANIC

SUBSTRATES………………………………….…………………………………….

33

4.1 Background and Prior Art of AiP Solutions………………………………….

33

4.2 An Ultra-Wide-band W-band End-fire Antenna……………………………..

36

4.2.1 Tapered Slot Antenna (TSA) Design Theory………...………...….....

37

4.2.2 TSA Design on LCP………...………...….....…...………...…............

38

4.2.3 Fabrication and Measurements of TSA..….....…...………...…............

42

4.3 Integration of V-band and W-band Antennas with SPDT Switch on Organic

Substrate………...………...….....…...………...…...............….......................

44

4.3.1 Dipole Antenna Design Theory………...………...….....…...…..........

45

4.3.2 Integration of V- and W- Band Antenna Arrays on Organic Substrate.. 47

5

DEVELOPMENT OF AN ON-CHIP ANTENNA.. ……………………………..…..

50

5.1 Background and Prior Art …………………………………....………...….....

50

5.2 Antenna Design …………………………………....………...…......…..........

54

5.2.1 On-chip Antenna Design using Localized Back-side Etching…..........

57

5.2.2 Antenna Design on LCP…..........…………....………...…......…..........

67

5.3 Fabrication …………………………………....………...…......…..................

68

5.4 Measurement Results and Discussion………....………...…......….................

69

5.4.1 On-chip Antenna Measurements…..........……...…......…....................

71

5.4.2 On-package Antenna Measurements…..........……...…......…..............

76

SUMMARY PART II…………………....………...….....…......…............................

79

PART - III

Design and Development of K-, V-, W, and D-band Front-end

Component sand Modules for Microwave

and Mm-wave Applications

6

BACKGROUND/LITERATURE SURVEY.. ……………………………..…..…....

82

6.1 Advanced Packaging Solutions for the Development of Mm-wave Modules... 82

IX

7

DEVELOPMENT OF K- AND V-BAND MODULES ON LCP…………...…..…....

90

7.1 Low Phase Noise K-Band Oscillator on Organic LCP Substrate………….....

90

7.2 Low Cost 60 GHz RF Front-end Transceiver Integrated on Organic

Substrate……………………………………………………………………..

99

7.2.1 Antenna Design…..........……...…......….............................................

99

7.2.2 Fabrication…..........……...…......…..................................................... 101

7.2.3 Measurements and Results..……...…......….......................................... 104

8

DEVELOPMENT OF W-BAND MODULES ON LCP…………...…..….................. 107

8.1 LNA Design…………......……...…......…........................................................ 108

8.2 Flip-chip Package Design...……...…......…....................................................... 109

8.3 Antenna Design…………...……...…......…..................................................... 119

8.4 Fabrication of Packaged LNA and Receive Module......................................... 121

8.5 Results and Measurements of Packaged LNA……........................................... 123

8.6 Results and Measurements of W-Band Packaged Receive Module...….........

125

8.7 Recommended Guidelines…………………………………………...…........... 129

9

DEVELOPMENT OF D-BAND MODULES ON LCP…………...…..….................. 103

9.1 D-band Indoor Path-loss Mesurements....…..................................................... 130

9.1.1 Measurement Setup…..........……...…......…......................................... 131

9.1.2 Path loss Mesurements........……...…......….......................................... 131

9.2 D-band Characterization of Co-planar Wave-guide and Microstrip

Transmission Lines and SIW on LCP ……………………………………… 135

9.2.1 Design of CB-CPWs….......……...…......…........................................

136

9.2.1.1 Design of Via-less 60 ohms CB-CPWs and 80 ohms Microstrip

Line……………………………..……………………….……… 137

9.2.1.2 Design of CB-CPW to Microstrip Transition Line………….....

138

9.2.1.3 Design of TRL Lines for Microstrip Loss Extraction……...….. 139

9.2.2 Fabrication…………………………….….......……...…......…............ 140

9.2.2.1 Additional Fabrication Considerations……………………... …. 141

9.2.3 Measurements………..……………….….......……...…......…............. 146

9.2.3.1 80 ohms Microstrip Loss Extraction with TRL Calibration….. .. 149

9.2.3.2 Via-Less 60 ohms CB-CPWs Measurements after LRRM

Calibration……………………………………………….…... … 150

9.2.3.3 Comparative Study Between CPWs Fabricated using 2 µm

and 9µm Cu…………………………………………..……......... 152

X

9.2.3.4 CPW to Microstrip Line Transition and Substrate Integrated

Waveguide (SIW)………..…………………………..…….......... 153

9.3 Characterization of a Low-loss and Wide-band (DC to 170 GHz)

Flip-chip Interconnect on an Organic Substrate………………………........... 155

9.3.1 The Design of a Flip-chip Interconnet….......……...…......….............. 156

9.3.2 Fabrication and Flip-chip Bonding……………………………............ 159

9.3.3 Measurements and Results……….……………………………............ 161

SUMMARY PART III…………………....………...….....…......….................... 165

10 CONTRIBUTIONS…………….……….………………………...…..….................... 168

11 FUTURE WORK...…………….……….………………………...…..….................... 170

APPENDIX A Facilities Used…….….………………………...…..…............................

171

LIST OF AUTHOR’S PUBLICATIONS………………………...…..….......................... 173

REFERENCES………………………….………………………...…..….........................

178

VITA………………………….………………………...…..…........................................... 200

XI

LIST OF TABLES

Page

Table 3.1: Dimensions of Ring Resonators and Transmission Lines (mm)…………

28

Table 5.1: On-chip Antenna Design Parameters…………………………………….

59

Table 5.2: On-package Antenna Design Parameters……………………………….

68

Table 5.3: Comparison between State-of-the-art On-chip Antennas…….…………..

78

Table 7.1: Comparison of Oscillators’ Phase Noise and Output Power….…………..

99

Table 7.2: Tx/Rx Total Gain Calculation……………………………...….………….. 106

Table 8.1: Antenna Design and Chip-Model Parameters………………….…………. 110

Table 8.2: RLC Values vs bump_h for Interconnect Eq.Model………..….…………. 119

Table 9.1: Measurement Parameters…………………………………....….…………. 132

Table 9.2: Design Parameters of CB-CPW Lines…………………….….…………… 138

Table 9.3: Design Parameters of Microstrip Lines……………………….…………… 139

Table 9.4: TRL Line Lengths…………………………………………….…………… 140

Table 9.5: LCP Package-and Chip- Model Parameters………………….…………… 158

Table 9.6: Comparison between State-of-the-art Flip-chip and Wirebond Interconnect 164

Table 9.7: Comparison of Flip-chip with other Interconnects……………………….

XII

164

LIST OF FIGURES

Page

Figure 1.1: Wireless technologies and applications in operation …………………………..

2

Figure 1.2: Some future potential applications at mm-wave and terahertz frequencies ……

2

Figure 2.1: (a) Free space measurement setup [16] (b) open resonator method

measurement setup, (c) cavity resonator [17], (d) ring resonator, (e)

Terahertz Time domain spectroscopy (TDS) method, (f) filled

waveguide method ……………………………………………………………

13

Figure 3.1: (a) open-gap-MRR-gap-open structure, (b) open-gap-open, (c) simple microstrip

(d) CBCPW cross-section …………………………………………………….

Figure 3.2: Radiation loss simulation results for microstirp, open-gap-open and open-gap-MRR-gap-open structures ……………………………………………….

26

27

Figure 3.3: (a) TRL lines standards, (b) ring resonator, (c) coupling gap between

the feed line and MRR ………………………………………………………..

29

Figure 3.4: Measured S21 of Ring Resonator ……………………………………………..

29

Figure 3.5: Measured/extracted relative permittivity using ring resonator dielectric

characterization method ………………………………………………………

30

Figure 3.6: Measured/extracted loss tangent using ring resonator dielectric

characterization method ……………………………………………………….

30

Figure 4.1: HFSS model with dimensions ………………………………………………….

39

Figure 4.2: Conventional microstrip-to-slot transition...……………………………………

39

Figure 4.3: Simulated S11 showing difficulty to realize slot width of (10um) for

50 ohms ………………………………………………………………………..

40

Figure 4.4: Current flow on the transition [68] ....................……………………………….

41

Figure 4.5: Equivalent circuit model of the microstrip-to-slot transition [68]……………..

41

Figure 4.6: Fabricated back to back transition …………………………………………….

42

Figure 4.7: Measured S-Parameters of the new transition …………………………………

42

Figure 4.8: Fabricated antenna and measurement setup: (a) measurement setup; (b) backside

of substrate (ground having TSA profile; (c) µstrip-to-slot transition with slow

wave structure (d) top side of substrate with CPW line…………………………

43

Figure 4.9: (a) Measured and simulated gain and S11 and (b) H plane co and cross polarization

measured and simulated results ..………………………………………………..

XIII

44

Figure 4.10: (a) HFSS model of integration of switch with antenna, (b)snapshot of fabricated

module, (c) wide-band wire-bond transition with compensation stub, (d)

measurements underway, and (e) cross-sectional view of integrated module

…………………………………………………………………………………… 48

Figure 4.11: (a) Measured and simulated gain and S-parameters and (b) H plane Co and

Cross polarization measured and simulated results …………………………….

49

Figure 5.1: Schematic view of a Yagi-Uda antenna including measurement pads ………….

55

Figure 5.2: On-chip Yagi-Uda antenna HFSS EM-model …………………………………..

58

Figure 5.3: Cross-sectional view of on-chip end-fire Yagi-Uda antenna with LBE ………..

58

Figure 5.4: Simulated insertion loss of back-to-back balun structure ………………...…….

60

Figure 5.5: Simulated effect of the silicon wall in front of the antenna (Si_f) on the

E-plane radiation pattern ……………………………………………………….

62

Figure 5.6: Simulated effect of the silicon wall in front of the antenna (Si_f) on the

H-plane radiation pattern……………………………………………………….

62

Figure 5.7: Effect of thin layer of Si (Si_r), in the cavity under the antenna on

return loss (S11…………………………………………………………………

63

Figure 5.8: Simulated effect of the silicon side-wall thickness (Si_s) on the H- and E-plane

radiation patterns at 143 GHz ………………………………………………….

64

Figure 5.9: Field distribution of on-chip antenna (a) side view, (b) 3D view ……………..

65

Figure 5.10: (a)Variation in the gain by varying the thickness of Si wall in front of the

antenna (Si_f), thickness of side-wall of Si (Si_s), and (b) cavity size (cav_l)

(refer to Fig. 5.1 and 5.2 for parameter identification), (c) variation in the

gain vs frequency by changing the length of the director (dir_l), and

(d) variation in the gain vs frequency by changing the length of the

driver(drv_l) …………………………………………………………………..

66

Figure 5.11: On-package Yagi-Uda antenna HFSS EM-model ……………………………

67

Figure 5.12: (a) On-chip Yagi-Uda antenna, (b) On-chip Yagi-Uda antenna after the

guard-ring is removed ………………………………………………………..

68

Figure 5.13: Yagi-uda fabricated on LCP substrate……………………………………….

69

Figure 5.14: (a) Probed antenna, (b) Setup for E-plane radiation pattern measurements…

70

Figure 5.15: Block Diagram of the radiation pattern measurement setup ………………...

70

Figure 5.16: Measured and simulated return loss and gain of the on-chip antenna with LBE .. 72

Figure 5.17: Measured and simulated E- and H-plane radiation patterns at 143 GHz of on-chip

antenna with LBE (a) E-plane, (b) H-plane …………………………………….

XIV

73

Figure 5.18: Block Diagram of the chip-to-chip link measurement setup…………………….

74

Figure 5.19: Link measurements for two on-chip antennas placed in front of each other…….

74

Figure 5.20: Simulated and Measured on-chip antenna efficiency …………………………… 76

Figure 5.21: Measured and simulated return loss and gain of antenna-in-package on an organic

substrate LCP ……………………………………………………………………. 77

Figure 5.22: Measured and simulated E- and H-plane radiation patterns of on-package (LCP)

antenna on an organic substrate ………………………………………………….. 79

Figure 6.1:

Advanced packaging techniques (a) SoC [94] (b) SiP [95], (c) SoP [97]……….. 83

Figure 6.2: (a) Micro-Coax based Packaging, (b) package using hot vias, and (c) package

using waveguide apertures ……………………………………………………...

85

Figure 6.3: Packaging interconnect technologies (a) embedded wafer level ball grid

array[107], (b) embedded wafer level package [109], (c) flip-chip [111],

and (d) wire-bond [110]………………………………………………………...

86

Figure 7.1: (a)Layout of /2 microstrip resonator coupled with microstrip line and

(b) simulated reflection coefficient of the resonator …………………………..

91

Figure 7.2: Block diagram of 1-port oscillator design …………………………………….

93

Figure 7.3: Complete schematic of the circuit ……………………………………………..

93

Figure 7.4: Micrograph of the fabricated circuit (dimensions in mm)…………………….

94

Figure 7.5: Simulation results for different lengths of short circuit stub and different

diameters of vias ……………………………………………………………..

95

Figure 7.6: Simulated reflection coefficient of the resonator …………………………….

96

Figure 7.7: Measured output power of oscillator …………………………………………

97

Figure 7.8: Measured phase noise ………………………………………………………..

98

Figure 7.9: Simulated phase noise ………………………………………………………..

98

Figure 7.10: 60 GHz 4×1 Yagi-Uda array layout. ………………………………………....

100

Figure 7.11: Block diagram of the Tx/Rx module………………………………………….

102

Figure 7.12: (a) Layout of the proposed package solution for the 60 GHz Tx/Rx module, (b)

Fabricated and assembled Tx/Rx module …………………..……………….

102

Figure 7.13: Fabricated capacitive stub to nullify the effect of ribbon inductance………..

103

Figure 7.14: Simulated return loss results with and without the capacitive stub …………

103

Figure 7.15: Measured S11 of active antenna array ……………………………………….

106

Figure 7.16: (a) Receiver side H-plane Co-polarization at 59 and 61 GHz,transmitter side

H-plane co-polarization at 60 GHz, Hcr polarization at 59 GHz and simulated

H-plane 60 GHz passive antenna, (b) measured Tx/Rx gain vs frequency plot

XV

from 55 to 65 GHz ……………………………………………………………

106

Figure 8.1: Circuit schematic of the designed LNA……………………………………….

108

Figure 8.2: (a) Flip-chip transition model (b) cross section of flip-chip when only substrate

is extended (c) cross section of flip chip when pad size is increased …………

109

Figure 8.3: (a) Cross sectional view of the package (b) Top View of the module for

packaged LNA …………………………………………………………………

110

Figure 8.4: Simulated S-parameters for flip-chip transition with 50 Ω GSG pads on the input

and output of the chip model. The insertion loss includes the loss of the CPW

line on the package ……………………………………………………………

112

Figure 8.5: Sweeping the parameter sub_ext (a) S11 (b) S21 while bump_rad= 25 µm and

bump_h =40 µm and pad_ext= 30 µm are kept constant ……………………

113

Figure 8.6: Sweeping the parameter pad_ext (a) S11 (b) S21 while bump_rad= 25 µm and

bump_h =40 µm and sub_ext =30 µm are kept constant ……………………

114

Figure 8.7: Sweeping the parameter bump_rad (a) S11 (b) S21 while pad_ext= 30 µm,

bump_h =40 µm, and sub_ext =30 µm are kept constant ……………………

115

Figure 8.8: Sweeping the parameter bump_h (a) S11 (b) S21 while bump_rad= 25 µm,

sub_ext =30 µm, and pad_ext= 30 µm are kept constant …………………….

116

Figure 8.9: Smith chart showing inductive and capacitive behavior by varying the parameter

bump_h while bump_rad= 25 µm, sub_ext =30 µm, and pad_ext= 30 µm ….. 116

Figure 8.10: Simulated S-parameters results for optimization of flip-chip parameters: bump

height, bump_rad and pad size. Insertion loss vs dimensions of parameters at 94

GHz and 110 GHz are shown …………………………………………………. 117

Figure 8.11: (a) Simplified HFSS flip-chip model (b) Extracted RLC Equivalent Model …

118

Figure 8.12: S21 and S11 correlation between HFSS and RLC flip-chip equivalent model …. 118

Figure 8.13: S21 and S11 correlation between HFSS and RLC flip-chip equivalent model … 119

Figure 8.14: Yagi-Uda antenna design parameters …………………………………………

121

Figure 8.15: (a) Fabricated Sample and (b) measurement in progress after assembly ……… 122

Figure 8.16: 8.16. (a) Yagi-Uda Antenna (b) SiGe LNA (c) Gold bumped SiGe LNA (d)

Fabricated and assembled Rx module ………………………………………… 123

Figure 8.17: (a) On-chip and Packaged LNA gain and return loss measurement (on- chip

and packaged S12 are omitted and (b) on-chip and packaged measured noisefigure of LNA ……………………………………………………………….

124

Figure 8.18: Measured and simulated reflection coefficient and gain of the passive antenna

and the active receive module ………………………………………………… 125

XVI

Figure 8.19: Block diagram of the measurement setup for radiation pattern measurement ..

126

Figure 8.20: Simulated and measured E- and H-plane radiation patterns of passive antenna .. 127

Figure 8.21: Simulated and Measured H- plane radiation patterns of passive of active

Module………………………………………………………………………….. 128

Figure 8.22: Simulated and measured E-plane radiation patterns of active module ………… 128

Figure 9.1:

Measurement setup for short range channel characterization in (a) LOS

environment and (b) partially obstructed LoS environment ………………….. 132

Figure 9.2:

Measured and theoretical path loss in LoS environment for several different

distances between the Tx and Rx …………………………………………….

Figure 9.3:

133

Measured path loss when LoS path is obstructed by ceramic mug, paper cup,

and a pcb board ……………………………………………………………..

134

Figure 9.4:

Design of via-less CB-CPW …………………………………………………

138

Figure 9.5:

Designed CB-CPW to microstrip transition ………………………………….

138

Figure 9.6:

Fabricated samples: (a) 1 mm long microstrip line, with CPW to microstrip

transition and showing the TRL calibration reference planes, (b) 0.5 mm long

60 ohms CB-CPW line (c) 2 mm long 60 ohms CB-CPW ………………….

141

Figure 9.7:

Fabricated structures using 2 and 9 µm of Cu ………………………………… 142

Figure 9.8:

(a) Step: 1 Cutting sample from the panel …………………………………….

Figure 9.8:

(b) Step: 2 Blue tape attachment ……………………………………………… 143

Figure 9.8:

(c) Step: 3 Etching of Cu for alignment vias …………………………………

143

Figure 9.8:

(d) Step: 4 Alignment, CPW and SIW via drilling ……………………………

144

Figure 9.8:

(e) Step: 5 Sputtering Cu on bottom side to metallize vias …………………… 144

Figure 9.8:

(f) Step: 6 Patterning the top side …………………………………………….

145

Figure 9.8:

(g) Step: 7 Patterning the bottom side ……………………………………….

145

Figure 9.9:

(a) Measurement Setup, (b) sample ready to be probed, (c) measurements

underway ……………………………………………………………………..

142

146

Figure 9.10: 9.10 Measurement of the thru standard after LRRM calibration (a) including

reflection coefficients, (b) Without S11 and S22 to adjust the scale of S21……… 147

Figure 9.11: TRL calibration lines ………………………………………………….………. 148

Figure 9.12: Measurement of the thru standard after TRL calibration ……………………… 148

Figure 9.13: (a) Measured s-parameters of the 0.5mm and 1mm long µstrip line after TRL

calibration (b) measured S21 of 0.5mm, 1 mm long microstrip lines …

150

Figure 9.14: 80 ohms microstrip attenuation vs. frequency (dB/mm) and (dB/𝝀g)…………

150

Figure 9.15: Via-less 60 ohms, CB-CPWs measurements after LRRM calibration ……….

151

XVII

Figure 9.16: Real and imaginary effective dielectric constant vs frequency ……………….

152

Figure 9.17: Comparison between CPW lines fabricated using 2 and 9 µm of Cu ………..

153

Figure 9.18: Fabricated CPW to microstrip transitions and SIWs …………………………

154

Figure 9.19: S-parameters of CPW to microstrip transition ……………………………….

154

Figure 9.20: S-parameters of CPW to microstrip to SIW transition ……………………….

155

Figure 9.21: (a) 3-D flip-chip structure in HFSS, (b) top view, (c) RLC equivalent model … 157

Figure 9.22: EM-simulated results of the flip-chip transition (LCP chip flipped on LCP

package) ……………………………………………………………………….. 159

Figure 9.23: Discontinuity caused due to high force during flip-chip bonding ……………… 160

Figure 9.24: Fabricated (a) LCP chip, (b) LCP with gold bumps, (c) LCP package with

high impedance sections, and (d) LCP chip flipped on LCP package ………… 161

Figure 9.25: Measured and simulated return loss and insertion loss for circuits shown in

Fig. 3…………………………………………………………………………… 162

Figure 9.26: Measured insertion loss of flip-chip transitions with 45 and 85% overlap of

the bump on the landing pad of the package, and insertion loss of the

back-to-back transition in dB/mm ……………………………………………… 163

XVIII

SUMMARY

This Ph.D. dissertation demonstrates the design and development of microwave

and mm-wave on-chip and on-package antennas and organically packaged components

and modules ranging from 20 GHz to 170 GHz.

Because of the tremendous amount of media streaming, video calling and high

definition TV and gaming, the biggest challenge for the wireless industry is the

increasing demand of high data rates. Utilization of mm-wave frequencies is an attractive

option to meet this high demand. In addition to higher data rate requirements for personal

area networks, precision requirements of passive remote sensing and imaging radars have

pushed the need to design radio frequency (RF) front ends in the W-band (75 GHz -110

GHz), D-band (110 GHz -170 GHz) and even at higher frequencies. Recent advances in

low cost semiconductor technologies allow realization of low-cost on-chip RF front-ends

in the high millimeter wave (mm-wave) frequencies, making it possible to realize

compact systems for these application areas. Although integrated circuits (ICs) are one of

the main building blocks of a mm-wave system, in order to realize a fully functional

wireless system, cost-effective antenna design and packaging are two important preconditions. Researchers have investigated and reported low-cost electronics packaging up

to 100 GHz to a great extent on ceramic substrates, but mm-wave packaging above 100

GHz is relatively less explored, particularly on organic substrates.

For packaging of next generation wireless systems, at present, ceramic based

materials are used for advanced package design. Liquid crystal polymer (LCP) is an

organic substrate material that has been demonstrated to be a competitive substrate and

packaging material due to its excellent electrical properties, flexibility and multi-layer

XIX

lamination capability. It has a low dielectric constant (~3.0), a low dielectric loss (0.003),

and temperature stability up to 305 ˚C across a wide frequency range (1-110 GHz). This

material can be processed in large panels with standard printed circuit board (PCB)

manufacturing process. For these reasons, for this work, LCP has been chosen as a

substrate and packaging material to develop organically packaged components and

modules for microwave and mm-wave applications.

The objective of this Ph.D. research was to design and develop mm-wave

components and modules on LCP, to investigate the viability of this organic substrate and

development of fabrication techniques in the K- (18-26.5 GHz), V- (50 to 70 GHz), W(75 to 110 GHz), and D- (110 to 170 GHz) bands. Additionally, a demonstration of a

micro-machined on-chip antenna has also been presented. This dissertation is divided in

three parts: (1) characterization of liquid crystal polymer from 110 to 170 GHz. (2)

development of highly radiation efficient on-chip and AiP antennas, and (3) development

of mm-wave modules with the integration of antennas.

(1)

Since LCP has not been characterized in the D-band, the first part of this

dissertation shows the characterization of LCP using ring resonators from 110 to

170 GHz. The challenge in the characterization at such a high frequency was to

address the issue of radiation loss which may affect the accuracy of extracted

electrical parameters. To analyze the radiation loss resulting from the ring

resonators or feeding structures, a new study has been carried out to address this

issue and extracted electrical parameters from 110 to 170 GHz have been

presented.

(2)

The second part of this dissertation demonstrates the development of on-chip

XX

and on-package antennas. Development of highly radiation efficient antennas and

their integration is an active research area. For potential applications in the E- and

W- band, we have demonstrated the design and development of a wide-band (73

GHz to 91 GHz) single element end-fire tapered slot antenna on LCP with a gain

of 8 dBi. To realize such a wide-band antenna, a new wide-band transition was

optimized for its optimum performance in the W-band. The integration of two

mm-wave antennas, operating at different frequencies, pose challenges (in terms

of coupling and isolation). For the first time we have integrated V-band and Wband antennas using a Hittite chip with optimized spacing showing the excellent

performance in terms of radiation patterns and isolation between two antennas.

Highly efficient on-chip antenna is an ultimate solution towards the

miniaturization of the systems. The development of such antennas is an up-hill

task because of the low-resistivity and high dielectric constant of silicon. In this

work we also demonstrate the development of an end-fire antenna with simulated

and measured radiation efficiency of 82 % and 76%, respectively. This

demonstration paves the way for the development of future chip-to-chip

communication and other potential application at mm-wave and sub-mm wave

frequencies.

(3)

The third part of this dissertation is devoted to the successful demonstrations of

organically developed modules, where antennas are integrated with different

components and wide-band mm-wave interconnects are optimized. We have

developed a 20 GHz low low-cost and low-phase noise oscillator and a 60 GHz

transceiver packaged on LCP using the wire-bond interconnect technology.

XXI

Because of its parasitics, wire-bond interconnect suffers from the issues of high

insertion loss and narrow bandwidth. Therefore, to develop low-loss systems, flipchip interconnects are preferred. Using the flip-chip interconnect, we have

developed mm-wave modules on LCP platforms in the W- and D-band, where the

benefits for this material can be exploited for wireless systems. Since LCP is a

soft and flexible substrate, a process needs to be developed for flip-chip

interconnect otherwise the thermo-compression technique or flipping the chip

using the sliver epoxy technique

may degrade the performance of the

interconnect by creating cracks in the metal and dents in the substrate. For the

first time, we have demonstrated a wide-band flip-chip interconnect from DC to

170 GHz with an insertion loss of as low as 0.2 dB. Moreover, high frequency

operation requires the use of thin substrates to avoid a surface wave issue and

meet the fine-pitch of the high frequency probes. This requires the realization of

fine features as small as 15 to 20 µm. On LCP, whose surface roughness is on the

order of 1-2 µm, a special process needs to be developed and extra care during the

fabrication is required to realize fine features. All these issues are addressed in the

dissertation. We have also investigated the possibility for D-band short-distance

indoor communications. Indoor line-of-sight and obstructed line-of-sight path loss

measurements have been taken and presented.

XXII

CHAPTER I

INTRODUCTION

1.1 Overview and Potential of mm-Wave Applications and Market

In today’s modern world, there has been an increased demand for high

performance wireless systems both in commercial and defense sectors. Some of the

applications include AM and FM radio transmission (153 KHz to 108 MHz), radio

frequency identification (RFID) (120 to 150 KHz 13.56 MHz, 433, 3.1 to 10 GHz),

global positioning system (GPS, 1-2 GHz), cellular communication (800 MHz, 2.4 GHz),

prospective 5G cellular communication (28 and 38 GHz) [1], WiFi (2.4 GHz, 5 GHz, 60

GHz in future) [2], satellite communication (4- 6 GHz) , military radar systems (8-12

GHz), digital satellite television (11-13 GHz), WPAN (60 GHz), automobile collision

avoidance radars (26 GHz, 77 GHz), microwave back haul communication (6, 11, 18, 23

38 GHz, 71 to 77 GHz, 81 to 86 GHz), mm-wave body scanning and imaging (94 GHz),

chip-to-chip communication (80 GHz and above), high resolution medical imaging (122

and 140 GHz and above) [3], radio astronomy(ALMA project) [4-5], short-distance high

speed communication ( 300 GHz and above) and terahertz medical applications. Some of

the above mentioned wireless systems have matured over the years and have been

commercialized, but some systems, especially mm-wave systems, are still in the research

domain. A snapshot of some of the wireless technologies in operation is shown in Fig.

1.1. Some of these products have been developed but the enhancement of the

performance and reducing the cost always demands for more research. Some of the

potential future applications are illustrated in Fig. 1.2.

1

Some of the other active research areas in the wireless domain are wireless power

transfer, wireless gas and electricity metering, energy harvesting, personal area networks

at 60 GHz and above, near field communication, and 5G cellular communication using

disruptive technologies like pico cell and cellular communication at mm-wave

frequencies using large scale MIMO.

Figure 1.1 Wireless technologies and applications in operation

Figure 1.2 Some future potential applications at mm-wave and terahertz frequencies

2

One example of a high speed communications link at 60 GHz or higher include

downloading a Blu-ray movie from a kiosk in a few seconds with mm-wave enabled

devices. Another application is streaming uncompressed high-definition audio/visual

content between a portable device and a graphics display. Most of these links are line-ofsight (LoS) links and indoor shadowing could block the direct communication. Efforts

are being expended to develop switched beam and MIMO techniques, where mm-wave

communication will be enabled using beam forming algorithms. The Internet-of-things is

another huge area, which will interconnect everything around us and according to Cisco’s

report, by year 2020, there will be 50 billion interconnected devices which will require

significant amount of upgrade in our existing wireless and wired infrastructure to enable

real-time flow of information [6-7]. This will create a trillion dollars of new markets and

industry. This internet of things, 5-G cellular communication personal area networks, and

high definition video streaming and imaging will require different specifications based of

the application. Some of these are data rates of 10 Gb/s, 10 years of operations for

machine-to-machine (M2M) sensing devices (10bps, 1Ah), as well as 1 ms real-time

latency to enable the flow of real time information[8].

To realize the aforementioned potential applications, a multitude of technologies

need to be developed. An important area that poses challenge to meet the demand of

higher data rates, low latency, and precision imaging is the development of radiation

efficient mm-wave antennas and the development and integration of antennas with other

low-cost mm-wave front-end components and modules. In this Ph.D. dissertation,

packaging and integration challenges towards the development of low-cost and highly

efficient mm-wave components and modules have been addressed and low-cost solutions

3

have been developed for potential mm-wave applications ranging from 20 GHz to 170

GHz.

1.2 Organization of the Dissertation

This dissertation is divided in three parts: (1) characterization of liquid crystal

polymer from 110 to 170 GHz, (2) development of highly radiation efficient on-chip and

AiP antennas, and (3) development of mm-wave modules with the integration of

antennas.

Chapter 2 reviews mm-wave substrates for advanced mm-wave packaging and

available techniques to characterize mm-wave substrates. It also identifies the challenges

and limitations of mm-wave substrate characterization using different techniques. In

Chapter 3 of this dissertation, the characterization of liquid crystal polymer from 110 to

170 GHz will be presented and a new study/technique to address the issue of radiation

loss, which may cause inaccuracies in the extraction of electrical parameters, is

presented. Chapter 4, in the beginning, reviews the existing antenna-in-package (AiP)

solutions and then describes the development of AiP solutions on organic substrate. Two

unique designs are presented. The first design is the demonstration of an ultra-wide-band

(73 to 91 GHz) tapered slot antenna with a new optimized wide-band mm-wave

microstrip-to-slot-line transition. The focus of the Chapter 5 is the development of highly

radiation-efficient end-fire on-chip antennas for future chip-to-chip and other

applications. This chapter starts with the challenges associated with on-chip antennas and

existing on-chip antenna solutions, and then explains our proposed highly radiationefficient (with measured state-of-the-art radiation efficiency of 76 %) on-chip antenna

solution. Chapter 6 reviews the advanced available packaging technologies. In Chapter 7

4

of this dissertation, the development of a K-Band low phase noise oscillator and a V-band

60 GHz transceiver using wire-bond interconnect technology are described. In Chapter 8,

we present the design and development of organically packaged flip-chip based W-band

receive module. A flip-chip transition for W-band is optimized and state-of-the-art

performance of a W-band module is presented. Chapter 9 pushes the frequency limits

towards 170 GHz and describes the development of D-band transmission lines, flip-chip

based modules and measurements of indoor obstructed and non-obstructed line-of-sight

measurements. It also presents the guidelines (for assembly and fabrication) to develop

mm-wave components on LCP.

5

PART I

Characterization of Liquid Crystal Polymer

from 110 GHz to 170 GHz

6

CHAPTER II

Background/Review of RF Substrates and their Characterization

Methods

Since LCP has not been characterized in the D-band, and one of the objectives of

this dissertation is to develop components and modules in the D-band. Therefore, it’s

very important to characterize LCP and extract its electrical parameters (dielectric

constant and loss tangent) so that the extracted electrical parameters are used in the

development of D-band components and modules. This chapter reviews the RF substrates

and their characterization method. In chapter 3, the characterization of LCP will be

presented.

2.1

RF Substrates for Mm-Wave Modules

In addition to the excellent electrical properties, packaging substrates should be

cost effective and compatible with different package integration technologies. To enable

the packaging of next generation wireless systems, many new materials are explored for

advanced package design. The desired characteristics for mm-wave packaging materials

are low dielectric loss (loss tangent), low and stable dielectric constant, hermeticity, low

coefficient of thermal expansion and multi-layer capability. Mainly, two kinds of

substrates meet the desired properties: ceramic substrates and organic substrates. Until

recently, packaging materials used for mm-wave packaging are advanced microwave

composites and ceramics. Some of these include alumina, high temperature co-fired

ceramics (HTCC) and low temperature co-fired ceramics (LTCC).

Prior to 1990s, multi-layer structures were realized using HTCC materials, which

7

are derivatives of alumina (alumina oxide). Multi-layer lamination was performed by

stacking layers of alumina plates and firing at approximately 1500 ºC to bond and harden

the plates. Unfortunately, this high temperature requirement prohibited the use of highly

conductive metals like silver, copper or gold (which all melt between 962 – 1085 ºC) [9].

Instead of high conductance metals, lower conductance metals like tungsten and

molybdenum were used. Since high conductance metals are necessary for high frequency

devices, HTCC were limited in their frequency range [10].

In the late 1990s, the customer driven wireless market pushed the developers of

RF hardware towards higher RF frequencies and greater circuit integration. HTCCs were

limited to lower frequencies because of their higher co-firing temperature and their

expensive manufacturability and assembly. As a solution to these problems, a ceramicorganic hybrid, known as low temperature co-fired ceramic (LTCC) was created. LTCCs

could be fired at 850-900 ºC, which permitted the use of high conductance metals. This in

turn extended the possible frequency range to much higher frequencies [10]. LTCC is the

current preferred packaging material, but there is a trade-off that after firing, the ceramic

shrinks in all three directions by 15-20%. This introduces an additional level of

complexity [11]. Moreover, LTCC has a higher dielectric constant (𝜺r = 5.9-9.1) that is

detrimental for antenna radiation efficiency [12]. Another limitation of ceramic based

substrate is that these are processed in a smaller tile size (5 inch x 5 inch or 8 inch x 8

inch in a very few foundries) [13], which makes the process expensive. Therefore, efforts

were made to find and develop a new low-cost and low-loss mm-wave substrate material

that can be processed in large panels and also have a low laminate temperature for multilayer packaging solutions.

8

In the past two decades, alternative organic substrate materials have been

developed. Polytetrafluroethylene (PTFE or Teflon), FR-4 and LCP are three examples.

PTFE and FR-4 are both used as printed circuit board (PCB) materials. PTFE offers

excellent RF performance but the cost is higher than other alternatives. FR-4, whose

name is an abbreviation of “flame resistant 4” is a good substrate material only at

frequencies up to 10 GHz [14]. Another limitation of FR-4, HTCC, and LTCC materials

is that multi-layer structures are usually monolithic (made of the same material). In the

case of FR-4, layers are bonded together using a laminating material such as Vialux (by

Dupont). And because of the poor adhesion property of PTFE, packaging with PTFE can

be difficult. But LCP has the advantage that it can bond to itself or to almost any other

material. Because of this and other excellent properties of LCP, which are listed below, in

early 2000, researchers started investigating LCP as a potential high frequency substrate

[15]:

Excellent electrical properties i.e., a low dielectric constant (~3.0), a low

dielectric loss (0.003), and temperature stability up to 305 ˚C across a wide

frequency range (1-110 GHz).

Low lamination temperature, 285 ºC

Low coefficient of thermal expansion compatible with Ag, Cu, Au

3-D multi-layer lamination capability

Flexibility for application in conformal flex circuits

Near hermetic

Flame retardant

Compatible with sequential buildup process in a printed circuit board foundry

9

LCP combines most of the strengths and almost none of the weaknesses of other

materials i.e.; it is low cost, easily packaged and has excellent RF performance. For

these reasons, LCP is chosen as a substrate and packaging material for this research.

LCP has been characterized up to 110 GHz. Since, we plan to develop mm-wave

modules up to 170 GHz, therefore it is important to characterize it up to 170 GHz to

extract its electrical parameters (dielectric constant and lost tangent or dissipation

factor).

2.2

Characterization of Electrical Parameters of Dielectric Materials:

As discussed earlier, the two electromagnetic properties, which define microwave

materials, are permittivity ɛ and permeability µ. ɛ indicates how the medium reacts

when an electric filed is applied, whereas µ indicates how the material reacts if a

magnetic field is applied. To take into account the losses of the material, permittivity and

permeability are both expressed in complex values:

ɛ = ɛ´ - j ɛ´´

µ = µ´ -j µ´´

= ɛo .ɛr (1 – j tan δɛ)

= µo . µr (1 – j tan δµ)

(1.1),

(1.2)

A material is classified as “dielectric” if it has the ability to store energy when an external

electric field is applied. By applying a DC voltage source across a parallel plate capacitor,

we can store an electric charge. Capacitance is defined as the charge “q” per applied

voltage “V” that is Co = q/V. Therefore, Co is also defined as

Co= ɛo (A/d),

(1.3)

10

where A is the area, d is the distance between the two plates, and ɛo = 8.85x10-12 (F/m)

is a universal constant. If a material is inserted between two plates, the capacitance is

increased by a factor ɛr =C/Co , which leads to

C= ɛrɛo (A/d),

(1.4)

In the above expression ɛ is the added storage capability and called the dielectric constant

or relative permittivity. For complex representation

ɛr = ɛr´ - j ɛr´´

(1.5)

The real part is called the dielectric constant and represents the amount of energy stored

and the imaginary part represents the loss factor. The imaginary part is always greater

than zero and is usually much smaller than loss tangent. Loss is also denoted by the loss

tangent tan δ which is defined as the ratio of the imaginary part of the dielectric constant

to the real part. The loss tangent is called tan delta or the dissipation factor.

Dielectric material, that is, insulators, possess a number of important electrical

parameters which make them useful in the electronics industry. Ferroelectric materials

such as barium titanate exhibit spontaneous polarization without the presence of an

external electric field. Their dielectric constants are orders of magnitude larger than those

of normal dielectrics. Thus, they are quite suitable for the manufacturing of small-sized,

highly efficient capacitors. They can also be utilized for memory devices in computers.

Other materials such as ceramics and organics are used as microwave substrates

and accurate measurements of these properties (dielectric constant and loss tangent) can

provide valuable information to properly incorporate the material into its intended

11

application. All materials of interest to the millimeter-wave package are assumed to be

isotropic and nonmagnetic (µr = µo ).

2.3

Material Characterization Methods:

In the following, a brief overview of material characterization methods is given.

Over the years there has been an abundance of methods developed for measuring

permeability and permittivity. These techniques include:

1- Capacitive or parallel plate Method (DC to 30 MHz)

2- Free space method

3- Cavity resonators

4- Transmission-line techniques

a. Open-ended coaxial probe techniques

b. Transmission and Reflection Method using Coaxial T.L and waveguide

c. CPWs and microstrip lines

d. Ring Resonators and T resonators

5- Fourier transform infrared spectroscopy ( 1 to 100 THz)

6- THz time domain spectroscopy (TDS)

Fig. 2.1 illustrates some of the characterization methods enumerated above.

To select a characterization method, one should consider:

1- The exploited frequency range

12

2- The physical properties of the material of concern: is it magnetic or not, low loss

or lossy, isotropic or anisotripic, homogeneous or heterogeneous, dispersive or

not and

3- The shape and nature of the available samples, i.e plate or thin films, liquid or

solid, elastomeric or granular.

Fig. 2.1 (a) Free space measurement setup [16] (b) open resonator method measurement

setup, (c) cavity resonator [17], (d) ring resonator, (e) Terahertz Time domain spectroscopy

(TDS) method, (f) filled waveguide method.

At microwave frequencies, generally higher than 1 GHz, transmission line, resonant

cavity, ring resonator and free-space techniques are commonly used. Each method has its

range of applicability and its limitations. For example, techniques based on cavities are

accurate, but not broad band. The resonant techniques have the ability to measure high

13

quality factor low loss materials but in a narrow frequency band. Resonant methods are

used to extract the permittivity of low loss materials. A material is normally classified as

a low-loss material if tan δ is less than 0.005. Medium loss refers to materials with 0.005

≤ tan δ ≤ 0.1. In general low-loss materials experience very little change in permittivity;

therefore, resonant techniques are well suited for low-loss materials. The broad band

techniques are well suited for high loss low Q materials. Nondestructive techniques,

although not most accurate, allow the maintenance of material integrity. Transmission

line techniques are the simplest of the relatively accurate ways of measuring the electrical

parameters of the materials. Transmission line measurements are made in waveguide,

coaxial line and planar transmission lines (CPWs or microstrip lines). The three major

problems encountered in transmission line measurements are air-gaps, half-wavelength

resonances, and over-moding.

In the following, we will briefly touch upon some characterization techniques

which are used to extract electrical parameters of the substrates.

2.3.1 Capacitance or Parallel Plate Method (DC to 30 MHz) [18]

The parallel plate method is used for frequencies below 30 MHz. LCR meter,

impedance bridges or impedance analyzer measurements are used to measure the parallel

plate capacitance of an electrode dielectric. [19-20]. The permittivity is then obtained

from the capacitance measurement and the material dimensions. Instead of a parallel

plate capacitor, inter-digital capacitors can also been used in certain circumstances, e.g

biosensors to determine remote complex permittivity [21]. The complex capacitance and

the permittivity can be calculated using the non-destructive method from 10 Hz up to 100

MHz. The capacitive method works well if the wavelength is much longer than the

14

conductor separation. In the lower megahertz range, the classical approach treats the

sample as a lossy capacitance measured in a bridge circuit or resonated with an inductor.

Above 1 MHz, the effectiveness of screening electrodes diminishes rapidly with

frequency. Therefore, the established two terminal resonance substitution method,

proposed by Hartshorn and Ward [22], is used. This method has poor uncertainties but is

used because of its ability to measure low losses.

2.3.2 Free Space Method

In this method, as shown in Fig. 2.1 (a), a sample is placed in between the two

horn antennas and measured S-parameters are used to extract electrical parameters. There

are some experimental difficulties such as theoretically the sample should of infinite size

and the propagating wave should be a planar wave. In reality, we can only go closer to

these ideal cases. A dielectric lens is used to focus the beam on a sample area of at least a

wavelength squared. This method is useful at mm-wave frequencies. But at very high

frequencies, the antenna size becomes very small and traditional microwave sources do

not work.

2.3.3 Cavity Resonators

Resonant cavities, illustrated in Fig. 2.1 (c), have very high Q and resonant modes

can be determined as functions of dimensions and relative permittivity. In the split cavity

resonator demonstrated by Kent [23] and further developed by Janezic and Baker-Jarvis

[24], the sample is inserted between the two halves of a cylindrical cavity excited in the

TE01,2q+1

mode. The permittivity is extracted by measuring the resonant frequency and the

dimensions. The material’s loss tangent is extracted by calculating the bandwidth of the

measured peak. Other geometries that can be used for cavity resonant methods are

15

dielectric cylinders, as demonstrated by Hakki and Coleman [25] and Courtney [26], and

non-radiative dielectric waveguides (NRD) [27]. The Fabry-Petro open resonator

technique has been shown to be suitable for characterization up to 300 GHz [28-29].

2.3.4 Transmission Line Techniques

Transmission line techniques generally fall into the following categories:

Off-resonance waveguide and coaxial line, full scattering parameter, 2-port

measurements.

Off-resonance short-circuit line, 1-port measurements.

Open-circuit techniques.

Resonant transmission-line techniques.

The off-resonance techniques can be broadly grouped into two categories:

Point-by-point or uncorrelated-point techniques.

Multi-point or correlated-point techniques.

A detailed discussion of transmission line (Coaxial line and Rectangular Waveguide)

techniques employing off-resonance techniques is given in [30].

Coaxial lines are broadband in the TEM mode and therefore are attractive for

permittivity and permeability measurements. The problem with coaxial lines, however, is

that due to the discontinuity of the radial electric field, any air gap around the center

conductor degrades the measurements by introducing large measurement uncertainty.

16

2.3.5 Fourier Transform Infrared Spectroscopy (1 to 100 THz) [18]

At infra-red frequencies, Fourier transform infra-red spectroscopy can be used to

extract complex permittivity. Further details can be found in [18].

2.3.6 THz Time Domain Spectroscopy (TDS) (0.1 THz to 10 THz)[18]

Terahertz time domain spectroscopy is another technique which is used to

characterize materials at THz frequencies. Further details can be found in [18]

2.4

Challenge in the Characterization of LCP in the D-band and Proposed

Method

A suitable characterization method needs to be chosen to characterize LCP at the

D-band. The parallel plate method is used for lower frequencies. The free-space method

requires extra components. Fourier Transform infrared spectroscopy and THz time

domain spectroscopy methods are used to characterize materials in THz domain and

require special equipment. Since LCP is a low-loss material, we need a technique which

can help us characterize LCP with enough precision. Therefore, resonant methods are a

better choice in this case. The cavity resonator method has limitations in terms of

extraction of the electrical parameters only at one frequency whereas ring-resonator

method gives us resonances at multiple harmonics.

The main challenge, using the ring resonator method, to extract dielectric

parameters at the D-band is to find accurate radiation loss expressions or to find out a

way where we can de-embed the radiation loss from the total loss. We carried out a new

study and a set of simulations to investigate the main source of radiation. The objective is

to find out if the ring is the primary source of radiation or the main cause of radiation is

17

the open-ended feeding microstrip line. This approach/method is discussed in the next

chapter.

18

CHAPTER III

Characterization of LCP from 110 to 170 GHz

In this chapter we present the characterization of LCP from 110 to 170 GHz. We

used the microstrip ring resonator (MRR) method for the extraction of the dielectric

constant (𝜺r) and the loss tangent. The MRR was designed on 2-mil LCP. The copper

surface roughness was first examined using a Tencor profilometer and its rms value

varied between 0.1 µm and 0.2µm. With these values, the surface roughness would not

approach the skin depth until 170 GHz (0.174 µm @ 170 GHz). The ring resonator

designs produce an S21 with periodic resonant peaks. The extraction of 𝜺r is dependent on

the location of the resonant frequencies for a resonator of a given radius, while the

extraction of the tan δ is a function of the unloaded quality factor (Q) of the peaks [31].

The desired resonant peaks and corresponding ring radii were devised according to (3.1):

𝑓0 =

𝑛𝑐

(3.1)

2𝜋𝑟𝑚 √𝜀𝑒𝑓𝑓

In the above equation, fo, rm, 𝜺eff and c correspond to the nth resonant frequency of the

ring, mean radius of the ring, effective dielectric constant of the substrate, and speed of

light in vacuum respectively. We also designed the conductor-backed CPW to microstrip

transition so that the samples could be probed. For the microstrip line and the MRR, a 70

Ω impedance was chosen for two reasons: (1) to reduce the frequency dispersion effect of

the microstrip line, (2) to ensure that the ratio of the microstrip width and the mean radius

of the ring is << 0.2 so that the radiation from the ring structure can be minimized [32].

19

3.1

Extraction of the Relative Permittivity

The effective permittivity can be calculated using equation (3.1). In equation (3.1),

values of n, c, r m are already known and through measurements we measure the resonant

frequency of the RR structure. Relative permittivity can be extracted using quasi-static

[33-36] or frequency dispersive [37-38] models of effective permittivity. For this work,

we have used quasi-static model used in [36]. We have used this model because it

includes the effect of conductor thickness.

We can obtain the quasi-static effective permittivity using the following equation

(3.2)

ɛ𝑒𝑓𝑓(0)

1

−

2

ɛ𝑟𝑒𝑙(𝑓)+1 ɛ𝑟𝑒𝑙(𝑓)−1

12

(1 +

)

+

𝑊

2

2

ℎ

[

=

−

ɛ𝑟𝑒𝑙(𝑓)+1 ɛ𝑟𝑒𝑙(𝑓)−1

12

(1 +

)

+

𝑊

2

2

{

ℎ

𝑊 2

W

+ 0.04 (1 − ) – C for ≤ 1

ℎ

h

]

(3.2)

1

2

–C

for W/h ≥ 1

where

𝐶=

ɛ𝑟𝑒𝑙(𝑓)−1 𝑡/ℎ

2

(3.3)

√𝑊⁄ℎ

If we solve equation (3.2) for ɛ𝑟𝑒𝑙(𝑓) then we get the following equation (3.4)

ɛ𝑟𝑒𝑙(𝑓)=

2ɛ𝑒𝑓𝑓(0) +𝑀𝑡 −1

(3.4)

𝑀𝑡 +1

20

In equation (3.4), Mt is the term, which represents the effect of thickness of metallization.

Mt is defined in [39] as:

𝑊

2.𝑡/ℎ

ℎ

4.6√𝑊/ℎ

𝑀𝑡 = 𝐹 ( ) −

(3.5)

where

1

(1 +

𝑊

𝐹 (ℎ) =

(1 +

{

12ℎ −2

𝑊

12ℎ

𝑊

)

)

𝑊 2

+ 0.04 (1 − ℎ ) , 𝑓𝑜𝑟

𝑊

, 𝑓𝑜𝑟

𝑊

1

−

2

ℎ

ℎ

≤1

(3.6)

≥1

If we substitute ɛ𝑒𝑓𝑓(0) in equation (3.4) with the value of effective permittivity

obtained from equation (3.1), it would give us a fair estimate of relative permittivity

ɛ𝑟𝑒𝑙(𝑓). However, microstrip does not support a pure TEM mode; a phenomena called

frequency dispersion occurs when the fundamental TEM mode starts coupling to the TM o

and TE1 surface-wave modes. TM0 has a zero-frequency cut-off, the TE1 starts

propagating at the frequency given by [40]:

𝑓𝑇𝐸1 =

𝑐𝑜

(3.7)

4𝐻√ɛ𝑟𝑒𝑙(𝑓)−1

One should make sure that TE1 mode is not excited over the characterization range.

Another way to calculate the frequency above which the dispersion of microstrip line

should be taken into account is given by the following equation:

𝑓𝑑 =

𝑍0𝑚

√

𝐻 √ɛ𝑟𝑒𝑙(𝑓)−1

(3.8)

21

where fd is in GHz and H is in cm.

Several models of frequency-dependent effective permittivity have been proposed and a

review and comparative study has been carried out in [41]. We have used the method

presented by Kirschning and Jansen described in [41] because of its demonstrated

accuracy [41] at mm-wave frequencies. In this method,

ɛ𝑒𝑓𝑓(𝑓) =

ɛ𝑟𝑒𝑙(𝑓)− ɛ𝑒𝑓𝑓(0)

(3.9)

1+𝑃(𝑓)

where

𝑃𝑓 = 𝑃1 𝑃2 [(0.1844 + 𝑃3 𝑃4 )10𝑓ℎ)]1.5763

𝑃1 = 0.27488 + [0.6315 + 0.525/(1 + 0.157𝑓ℎ)20 ]𝑢 − 0.065683exp(−8.7513𝑢)

𝑃2 = 0.33622{ 1 − 𝑒𝑥𝑝[−0.03442. ɛ𝑟𝑒𝑙 (𝑓)]}

𝑃3 = 0.0363𝑒𝑥𝑝(−4.6𝑢) × {1 − exp[−(

20

𝑓ℎ 4.97

) ]}

3.87

𝑃4 = 1 + 2.751 {1 − exp[−ɛ𝑟𝑒𝑙 (𝑓)/15.916)8 ]}

By using numerical techniques such as the secant method [42], which was implemented

for the work presented in Chapter 2 of [43], equations 3.2 and 3.9 are coupled to find the

value of ɛ𝑟𝑒𝑙 (𝑓).

3.2

Extraction of the Loss Tangent and Investigation of the Radiation Loss

The extraction of the loss tangent was done by using equation (3.10) in which the

extracted effective permittivity from the dispersive model of [37] was used.

tan 𝛿 =

𝛼𝑑 𝜆0 √𝜀𝑒𝑓𝑓 (𝜀𝑟 − 1)

(3.10)

𝜋𝜀𝑟 (𝜀𝑒𝑓𝑓 − 1)

22

In equation (3.10), λ0, 𝜺eff, and 𝜺r represent the free space wavelength, the effective

permittivity, and the relative permittivity respectively.

The dielectric loss can be calculated using equation (3.10) introduced in [44]. This

equation gives the result in [Np/unit length]. The ring resonator method gives the total

loss at the frequency locations of each resonant peak and by subtracting the theoretical

values for the conductor loss we obtain the dielectric loss as shown in equation (3.11).

𝛼𝑑 = 𝛼𝑡𝑜𝑡𝑎𝑙 − 𝛼𝑐

[

𝑁𝑒𝑝𝑒𝑟𝑠

]

𝑢𝑛𝑖𝑡 𝑙𝑒𝑛𝑔𝑡ℎ

(3.11)

𝛼𝑡𝑜𝑡𝑎𝑙 is the total loss in the microstrip ring resonator, and 𝛼𝑐 is the microstrip conductor

loss. Then dielectric loss is inserted into equation (3.10) to obtain the loss tangent. The

radiation loss has been neglected in this expression for following reasons:

The ring resonator is designed with careful selection of microstrip widths and

mean radius. The radiation properties of ring resonators are explained in [45]

where it is shown that the radiation loss from the ring is extremely low for

the transverse TM11 mode. This is because the field from the inner and outer

edges of the ring interferes with each other destructively at resonance.

By making W/r m << 0.2, the excitation of the TM11 mode is ensured [46]

We know that oan pen-ended microstrip line radiates. This effect has been

neglected because this effect is de-embedded out because the TRL calibration

was used for measurements. This effect is verified by running a set of

simulations in a 3D simulator HFSS. The results will be presented later in

this chapter.

23

3.2.1 Total Loss Calculation

Total loss 𝛼𝑡𝑜𝑡𝑎𝑙 is calculated from each peak resonance found in the measured

S21 response of the ring resonator by computing the loaded (QL) and unloaded Quality

factor (Qu) [47]. QL and QU are calculated using the following expressions:

𝑄𝐿 =

𝑓𝑛𝑡ℎ

𝐵𝑊3𝑑𝐵

(3.12)

𝑄𝑈 = 𝑄𝐿 /(1 − 10

𝑆21,𝑑𝐵 (𝑓𝑛𝑡ℎ )

20

)

(3.13)

where BW3dB is 3 dB bandwidth of the S21 resonance peak and S21,dB(fnth) is the measured

value of S21 in dB at fnth. Finally the total attenuation is calculated by the following

expression:

𝛼𝑡𝑜𝑡𝑎𝑙 =

𝜋

𝑄𝑢 𝜆𝑔

(3.14)

where

𝑐

𝜆𝑔 = 𝑓

(3.15)

𝑛𝑡ℎ √ɛ𝑒𝑓𝑓 (𝑓𝑛𝑡ℎ )

3.2.2 Conductor Loss Calculation

The conductor loss is calculated by using the following expression, originally proposed

by Schneider in [48]:

𝛼𝑐 =

𝑊 2

ℎ

2

𝜋 ln(10) ℎ.𝑍𝑜𝑚 32+(𝑊)

ℎ

10

{

𝑅𝑠

32−( )

20

𝑅𝑠 𝑍𝑜𝑚 .ɛ𝑒𝑓𝑓 (𝑓)

ln(10)

ℎ.ɳ2

{1 +

{1 +

ℎ

𝑊

(1 +

𝜕𝑊

𝜕𝑡

)} , [dB/unit length]

𝑓𝑜𝑟

𝑊

ℎ

≤1

(3.16)

ℎ

𝑊

(1 +

𝜕𝑊

𝜕𝑡

𝑊

6ℎ

ℎ

𝑊

)} . { +

ℎ 5

𝑊

𝑊

ℎ

[(1 − ) + 0.08]}, [dB/unit length], 𝑓𝑜𝑟

24

≥1

where

𝜕𝑊

1

2𝐵

= ln( )

𝜕𝑡

𝜋

𝑡

and

ℎ,

𝐵={

2𝜋𝑊,

𝑊

ℎ

≥ 2𝜋

𝑊

ℎ

(3.17)

≤ 2𝜋

In equation (3.16) Zom can be found using the following expression:

ɳ

8

ln [

+ 0.25𝑊𝑒𝑓𝑓 ]

𝑊𝑒𝑓𝑓

2𝜋√ɛ𝑒𝑓𝑓

𝑍𝑜𝑚 =

{

ɳ

[𝑊𝑒𝑓𝑓 + 1.393 + 0.667 ln(𝑊𝑒𝑓𝑓 + 1.444)]−1

√ɛ𝑒𝑓𝑓

,

𝑊

≤1

ℎ

(3.18)

𝑊

, ≥1

ℎ

where ɳ = 120 𝜋 ,the free space impedance.

In equation (3.16) Rs can be calculated using the following expression. Rs includes a

correction factor originally introduced by Morgan in [49]

2

𝑅𝑠 = 𝑅𝑠 , {1 + 𝜋 𝑡𝑎𝑛−1 [1.4 (

𝛥𝑟𝑚𝑠 2

𝛿𝑠

) ]}

(3.19)

where

𝑅𝑠 , = √𝜋𝑓µ𝑜 𝜌𝑐

(3.20)

In expression (3.19), 𝛿𝑠 is given by

𝛿𝑠 =

25

𝜌𝑐

𝑅𝑠

where 1/𝜌𝑐 =σc=5.8x107 S/m( the conductivity of the copper), µ𝑜 is the permeability of

the vacuum , and 𝛿𝑠 is the frequency-dependent skin depth.

𝑊𝑒𝑓𝑓 in equation (3.18) can be calculated using the following expression:

𝑡

𝑊𝑒𝑓𝑓

4𝜋𝑊

𝑊 + 𝜋 (1 + 𝑙𝑛 𝑡 ),

={

𝑡

2ℎ

𝑊 + 𝜋 (1 + 𝑙𝑛 𝑡 ),

𝑊

ℎ

𝑊

ℎ

≤ 1/2𝜋

(3.21)

≥ 2𝜋

The radiation loss has been neglected based on the arguments presented earlier and the

proof that the ring does not radiate is presented in this work through simulations of 3D

electromagnetic models, with results presented in Fig. 3.2.

The radiation analysis was carried out at each resonant frequency of the MRR,

using a full-wave electromagnetic solver, for open-gap-MRR-gap-open, open-gap-open

and simple microstip line structures as shown in Fig. 3.1(a-c).

Figure. 3.1. (a) open-gap-MRR-gap-open structure, (b) open-gap-open, (c) simple

microstrip (d) CBCPW cross-section

26

The radiation loss curves for cases 3.1(a) and 3.1(b) closely overlap as shown in Fig. 3.2.

Therefore, it is evident that the main cause of the radiation loss is the feeding microstrip

discontinuities and not the ring itself. Moreover, we designed the ring resonator ensuring

that mrr_w/rm << 0.2 so that only the TM11 mode is excited. r m and mrr_w represent the

radius and the width of the ring resonator respectively.

Figure 3.2. Radiation loss simulation results for microstrip, open-gap-open and open-gapMRR-gap-open structures

3.3

Fabrication and Measurements

To fabricate the designed ring resonator, a 2 mil double copper (9 µm) cladded LCP

substrate was used. The patterning of the designs was carried out using standard

lithography and wet etching processes. The fabricated sample is shown in Fig. 3.3 (b).

The measured dimensions of the various features of the MRR and TRL standard lines are

tabulated in Table 3.1.

27

Table 3.1

Dimensions (mm)

mrr_w

0.0625

strip_w

0.0625

c_g

0.035

d_out

6.0303

s

0.041

d_in

5.9053

w

0.037

thru_TRL

0

w_g

0.235

TRL_L1

500

TRL_L2

850

The measurements were taken using Cascade MicroTech Infinity D-band probes.

The pitch of the probes was 75 µm. To calibrate out the cable, probe and test head losses,

we performed LRRM calibration on Cascade 138-356 ISS. After the LRRM calibration,

the TRL calibration was carried out using the designed TRL standard lines shown in Fig.

3.3 (a). After the TRL calibration, the reference plane moved to aa - and bb- as shown in

Fig. 3.3 (a) and (b).

Measured S21 response of the ring resonator is shown in Fig. 3.4. The

measured/extracted dielectric constant and the loss tangent are shown in Fig. 3.5 and Fig.

3.6 respectively.

Using the frequency dispersive model, the LCP dielectric constant is extracted to

be about 3.17 at 155 GHz and the loss tangent is estimated to be 0.0057. The uncertainty

bars represent the 95% confidence interval calculated using the Monte Carlo uncertainty

analysis as implemented in [43], using a population of 1E6 samples for all measured

quantities.

28

Figure 3.3. (a) TRL line standards, (b) ring resonator, (c) coupling gap between the feed line

and MRR

Figure 3.4. Measured S21 of Ring Resonator

29

Figure 3.5. Measured/extracted relative permittivity using ring resonator dielectric

characterization method

Figure 3.6. Measured/extracted loss tangent using ring resonator dielectric characterization

method

30

SUMMARY OF PART 1

In the first part of the dissertation, we first reviewed advanced packaging

substrates and discussed advantages and disadvantages of organic and ceramic substrates.

We also briefly reviewed various substrate characterization methods. Since LCP was not

characterized in the D-band, for the first time, we presented the characterization of the

dielectric properties of LCP from 110-170 GHz using the ring resonator method. We

carried out a study to show that the main source of radiation is the open-ended microstrip

feeding line and not the ring resonator itself. Therefore, if TRL calibration is used,

radiation loss can be eliminated from the total loss. The ring resonator characterization

results show 𝜺r = 3.17 and tan δ varies from 0.005 to 0.009. These results present the

excellent RF performance of LCP across the entire D-band which paves the way for

system-on-package solutions in the D-band using LCP.

31

PART II

Design and Development of on-chip and Antennain-Package Solutions for mm-wave Applications

32

CHAPTER IV