Get

advertisement

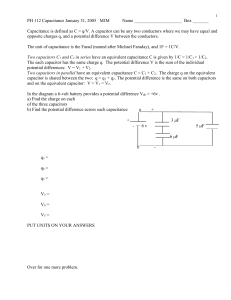

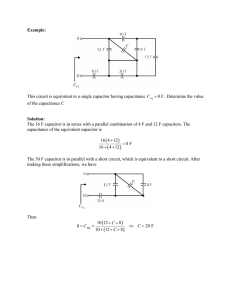

A 16 GHz silicon-based monolithic balanced photodetector with on-chip capacitors for 25 Gbaud front-end receivers Mohammed Shafiqul Hai,1,* Meer Nazmus Sakib,1 and Odile Liboiron-Ladouceur1 1 Department of Electrical and Computer Engineering, McGill University, Montreal, Quebec H3A 2A7, Canada * md.hai@mail.mcgill.ca Abstract: In this paper, a Germanium-on-Silicon balanced photodetector (BPD) with integrated biasing capacitors is demonstrated for highly compact monolithic 100 Gb/s coherent receivers or 25 Gbaud front-end receivers for differential or quadrature phase shift keying. The balanced photodetector has a bandwidth of approximately 16.2 GHz at a reverse bias of −4.5 V. The balanced photodetector exhibits a common mode rejection ratio (CMRR) of 30 dB. For balanced detection of return-to-zero (RZ) differential phase shift keying (DPSK) signal, the photodetector has a sensitivity of −6.95 dBm at the BER of 10−12. For non-return-to-zero (NRZ) on off keying (OOK) signal, the measured BER is 1.0 × 10−12 for a received power of −1.65 dBm at 25 Gb/s and 9.9 × 10−5 for −0.34 dBm at 30 Gb/s. The total footprint area of the monolithic front-end receiver is less than 1 mm2. The BPD is packaged onto a ceramic substrate with two DC and one RF connectors exhibits a bandwidth of 15.9 GHz. ©2013 Optical Society of America OCIS codes: (060.2330) Fiber optics communications; (060.0060) Fiber optics and optical communications; (230.0230) Optical devices. References and links 1. J. Fischer, R. Ludwig, L. Molle, M. Noelle, A. Beling, C. Leonhardt, A. Matiss, A. Umbach, R. Kunkel, H.-G. Bach, and C. Schubert, “Integrated Coherent Receiver Modules for 100G Ethernet and Beyond,” Proceedings ITG Symposium of Photonic Networks, 12, 1–5 (2011). 2. u2t photonics, http://www.u2t.com/products/all-products/item/cprv1220a?category_id=6, coherent receiver module CPRV1220A. 3. Y. Painchaud, M. Pelletier, M. Poulin, F. Pelletier, C. Latrasse, G. Robidoux, S. Savard, J. Gagné, V. Trudel, M. Picard, P. Poulin, P. Sirois, F. D'Amours, D. Asselin, S. Paquet, C. Paquet, M. Cyr, and M. Guy, “Ultra-Compact Coherent Receiver Based on Hybrid Integration on Silicon,” in Proc. Optical Fiber Communication Conference and Exposition (OFC) and The National Fiber Optic Engineers Conference (NFOEC), OMJ.2,1–3 (2013). 4. C. Doerr, P. Winzer, Y. Chen, S. Chandrasekhar, M. Rasras, L. Chen, T. Liow, K. Ang, and G. Lo, “Monolithic polarization and phase diversity coherent receiver in silicon,” J. Lightwave Technol. 28(4), 520–525 (2010). 5. C. Doerr, L. Buhl, Y. Baeyens, R. Aroca, S. Chandrasekhar, X. Liu, L. Chen, and Y. Chen, “Packaged monolithic silicon 112-Gb/s coherent receiver,” IEEE Photon. Technol. Lett. 23(12), 762–764 (2011). 6. u2t photonics, http://www.u2t.com/products/photodetectors/item/bpdv2xx0r?category_id=2, balanced photodetector module BPD2XX0R. 7. T. Liow, K. Ang, Q. Fang, J. Song, Y. Xiong, M. Yu, G. Lo, and D. Kwong, “Silicon Modulators and Germanium Photodetectors on SOI: Monolithic Integration, Compatibility, and Performance Optimization,” IEEE J. Sel. Top. Quantum Electron. 16(1), 307–315 (2010). 8. Optoelectronic Systems Integration in Silicon (OpSIS), http://opsisfoundry.org/ 9. S. J. Koester, J. D. Schaub, G. Dehlinger, and J. O. Chu, “Germanium-on-SOI Infrared Detectors for Integrated Photonic Applications,” IEEE J. Sel. Top. Quantum Electron. 12(6), 1489–1502 (2006). 10. T. Yin, R. Cohen, M. M. Morse, G. Sarid, Y. Chetrit, D. Rubin, and M. J. Paniccia, “31 GHz Ge n-i-p waveguide photodetectors on Silicon-on-Insulator substrate,” Opt. Express 15(21), 13965–13971 (2007). 11. M. Gould, T. Baehr-Jones, R. Ding, and M. Hochberg, “Bandwidth enhancement of waveguide-coupled photodetectors with inductive gain peaking,” Opt. Express 20(7), 7101–7111 (2012). 12. T. Baehr-Jones, R. Ding, A. Ayazi, T. Pinguet, M. Streshinsky, N. Harris, J. Li, L. He, M. Gould, Y. Zhang, A. Lim, T. Liow, S. Teo, G. Lo, and M. Hochberg, “A 25 Gb/s Silicon Photonics Platform,” Preprint at http://arxiv.org/abs/1203.0767 (2012). #199407 - $15.00 USD Received 14 Oct 2013; revised 5 Dec 2013; accepted 7 Dec 2013; published 24 Dec 2013 (C) 2013 OSA 30 December 2013 | Vol. 21, No. 26 | DOI:10.1364/OE.21.032680 | OPTICS EXPRESS 32680 13. K. Onohara, T. Sugihara, Y. Konishi, Y. Miyata, T. Inoue, S. Kametani, K. Sugihara, K. Kubo, H. Yoshida, and T. Mizuochi, “Soft secision-based forward error correction for 100 Gb/s transport systems,” IEEE J. Sel. Top. Quantum Electron. 16(5), 1258–1267 (2010). 14. H. Pan, S. Assefa, W. M. J. Green, D. M. Kuchta, C. L. Schow, A. V. Rylyakov, B. G. Lee, C. W. Baks, S. M. Shank, and Y. A. Vlasov, “High-speed receiver based on waveguide germanium photodetector wire-bonded to 90nm SOI CMOS amplifier,” Opt. Express 20(16), 18145–18155 (2012). 1. Introduction Optical coherent detection is considered as the most favoured solution for optical communication networks beyond 100 Gb/s for its high capacity through polarization division multiplexing and its ability to support complex modulation formats and digital signal processing based impairment mitigation techniques [1–5]. In a coherent receiver, the optical hybrid mixes the signal with a local oscillator with quadrature phases (0, 90, 180 and 270degrees). The output of the hybrid has to be detected and subtracted for the out-of-phase ports to extract the inphase and quadrature signals. This can be achieved either by using a balanced photodetector (BPD) [4] or a differential amplifier [5]. The monolithic integration of a coherent receiver with photodetectors (PDs) and amplifiers attracted a lot of interest in both industry and academia [1–6]. InP based coherent receivers are already available commercially with one package dimension of 40 mm × 40 mm [1, 2]. Silicon-based photonic monolithic integration is a relatively new research topic that has generated a lot of interest due to the possibility of compatibility with well-established low-cost CMOS fabrication processes. The possibilities of integrating both optical and electrical functions within the same fabrication process may lead to overall fabrication cost reduction and enhanced device performance [3–5]. Recently, an ultra-compact silicon-based coherent receiver was demonstrated by Painchaud, et al. with a small footprint of 23 mm × 18 mm [3]. This is almost half the size of the MSA adopted small form-factor pluggable modules (CFP). In [3], the optical hybrid mixer and polarization beam splitter (PBS) are fabricated in silicon-based process with external balanced photodetectors wire-bonded to the photonic chips. Capacitors required for biasing purpose of the photodetectors are also off-chip. In a balanced photodetector, the PDs are in series with the n-contact of one PD connected to the p-contact of the second PD. When detecting a bit (1 or 0) from the optical hybrid, one of the PDs is disabled (in “off” state) while the other PD is enabled (in “on” state). The “off” PD's internal capacitance is in parallel with the “on” PD since the two PDs share the same AC ground and AC signal path. Consequently, the overall capacitance is doubled resulting in a 50% degradation of the bandwidth when compared to a single PD. The balanced PD also needs to be biased through inductors and use capacitors providing high frequency grounds. Note that the biasing capacitors do not affect the bandwidth directly. For biasing purposes onchip capacitors provide several advantages over external capacitors: smaller footprint area and less parasitic capacitance due to wire bonding. However, the design of a BPD with onchip biasing capacitors is limited in current silicon-on-insulator (SOI) processes due to the availability of only a couple of metal layers in the fabrication process. Doerr, et al. published a study about a coherent receiver using on-chip capacitors using 2 metal layers of a CMOS compatible Si-photonics process [4]. The BPDs with biasing capacitors had a bandwidth of only 5 GHz at 25 Ω load and responsivity of ~0.75 A/W. The coherent receiver relied on signal post-processing for 100 Gb/s applications. In following work by Doerr, et al. [5], the signals were individually detected with four single photodetectors for each polarization and relevant channels were subtracted using off-chip differential transimpedance amplifiers (TIAs) to avoid using BPDs. In this paper, a balanced photodetector with on-chip biasing capacitors is demonstrated with detailed explanation about design methodology and experimental verification. The photodetectors subtract the signal on chip and provide a large electrical output swing which eliminates the need for using external wide bandwidth linear TIAs. The BPD has a bandwidth of 16.2 GHz at 50 Ω load and supports 25 Gb/s optical signals without requiring signal post-processing. The BPD has an output voltage signal of 28.5 mVp-p at a received power of −6.95 dBm providing greater margins in designing power efficient receiver. #199407 - $15.00 USD Received 14 Oct 2013; revised 5 Dec 2013; accepted 7 Dec 2013; published 24 Dec 2013 (C) 2013 OSA 30 December 2013 | Vol. 21, No. 26 | DOI:10.1364/OE.21.032680 | OPTICS EXPRESS 32681 2. Design of the BPD with on-chip capacitor In this section, the design of the BPD (Fig. 1) with on-chip capacitors will be discussed in detail through simulation and experimental investigation. The passive optical waveguides are based on 500 nm × 220 nm strip waveguides with 2 µm of silicon oxide as the lower cladding. The process supports Germanium (Ge) implant for photodetectors and 2 metal layers for interconnect. Firstly, the design of the metal insulator metal (MIM) capacitor will be discussed. Later, we will investigate the balanced photodetector and the receiver as a whole. 2.1 Design of the biasing capacitor 709 µm VIA2 (M1-M2) 468 µm VIA1 (M1-Si/Ge) M1 M2 MIM Capacitor M2 V M2 G V Optical waveguide M2 Optical waveguide S G S G 1025 µm -V t1 Al d SiO2 t2 Al MIM Capacitor M2 G M2 -V ε1 M2 M1 915 µm Fig. 1. Photodetector with on-chip capacitor for biasing (G: ground, M1: metal 1, M2: metal 2, MIM: metal-insulator-metal, S: signal. The drawing is not according to the scale). The bottom left inset shows the cross-section of the on-chip capacitor. In this section, the design of the capacitor for biasing both PDs will be discussed. To provide an AC signal ground to the photodetector and isolate the DC bias voltage from the output load, a DC blocking capacitor is used to complete the electrical path of the photodetector circuit. Off-chip capacitors with an external bias tee circuit can be used for this purpose. The design of an off-chip bias tee with DC block capacitor is simpler for single PD. On the other hand for BPD’s design, the off-chip bias circuit becomes complex due to the need of two DC blocking capacitors. Integrating on-chip DC block capacitor with BPD can greatly simplify the integration of the BPD with other building blocks of a circuit such as coherent receiver or phase demodulator for DPSK and DQPSK at the optical input port. The electrical design of the coherent receiver requires a linear front-end and by integrating the photodetectors improved sensitivity and voltage swing can be achieved which simplifies the transimpedance amplifier (TIA) and linear amplifier design at the electrical output port of the BPD. Our simulation result shows that for the designed BPD in this work, the biasing capacitor must have a capacitance of at least 10 pF over the whole frequency band of the photodetector. At lower capacitance, signal distortion at lower frequency is observed. The CMOS compatible fabrication process used has 2 metal layers with a dielectric between them. A metal insulator metal (MIM) capacitor can be formed between these 2 layers as shown in Fig. 1. Metal areas of equal dimensions are used in metal layer 1 (M1) and 2 (M2). Upper metal layer of the MIM capacitor is used as the ground layer. The other end is connected to M1 and the bias supply in M2 through a VIA layer connecting both layers M1 and M2. The capacitor is formed by two parallel plates (M1 and M2). The inset at the bottom #199407 - $15.00 USD Received 14 Oct 2013; revised 5 Dec 2013; accepted 7 Dec 2013; published 24 Dec 2013 (C) 2013 OSA 30 December 2013 | Vol. 21, No. 26 | DOI:10.1364/OE.21.032680 | OPTICS EXPRESS 32682 left of Fig. 1 shows the geometry of the capacitor. The thicknesses of the plates are t1 = 2 µm and t2 = 0.75 µm, and the distance between the two is d = 1.5 µm. The relative permittivity of SiO2 between the two plates is ε1 = 3.9. The required capacitor area is investigated through simulation using the commercial tool ANSYS HFSS taking into account effects including the electric field distribution and the thickness of the plates. The capacitance is taken from the Sparameter. It is observed that a capacitor made of two metal plates of area 709 µm × 468 µm is a good design choice for biasing condition. The resulting capacitance from simulation is presented in Fig. 2. It is observed that over a bandwidth of 20 GHz the capacitance is always above 13.5 pF. 19 Capacitance (pF) 18 17 16 15 14 13 0 5 10 Frequency (GHz) 15 20 Fig. 2. Simulated capacitance as a function of frequency of the MIM capacitor. 2.2 Design of the photodetector In this section, the design of the BPD is investigated. The photodetector (PD) has a vertical Ge-on-silicon p-i-n junction. The details of similar fabrication approach used can be found in [7]. Strain relaxed Ge is grown on top of a SiGe buffer with expected strain of 0.2-0.3% to have better responsivity beyond 1550 nm wavelength. The measured absorption coefficient of Ge used in the photodetector is around 0.2-0.4 dB/μm (460 cm−1 to 921 cm−1) at 1550 nm wavelength [8]. This value matched quite well the value reported in [9] for strain relaxed pure Ge. The n-type Ge area of 8 μm × 26 μm is chosen to provide acceptable responsivity (~0.7 A/W). In addition, it is found that the bandwidth of the photodetector critically depends on the Ge layer area, which will be discussed later in this section. The n-type doping dose in Ge and p-type doping dose in Si are 4 × 1015 cm−2 (dose energy of 10 KeV) and 5 × 1014 cm-2 (dose energy of 20 KeV), respectively [8]. The input silicon waveguide width is 500 nm tapered from 3.5 μm at the input of the PD active region over a tapered length of 120 μm. The area of the silicon passive waveguide over which the actual active section of the PD is built is 19 μm × 30 μm. Thickness of the Ge-layer is 500 nm. As shown in Fig. 1 the internal connection of two single PDs is completed through a via connecting metal layer 1 (M1) to the Germanium layer. The width of the metal layer of the vias is 8 μm. Considering the 0.65 μm thickness of the M1, the resistivity of this layer was calculated to be approximately 0.065 μΩ-m. #199407 - $15.00 USD Received 14 Oct 2013; revised 5 Dec 2013; accepted 7 Dec 2013; published 24 Dec 2013 (C) 2013 OSA 30 December 2013 | Vol. 21, No. 26 | DOI:10.1364/OE.21.032680 | OPTICS EXPRESS 32683 Fig. 3. Equivalent circuit of the BPD with on chip capacitors. To determine the electrical bandwidth of the balanced photodetector, first the parasitic contact resistance and capacitance of a single photodetector are extracted using Sentaurus Device simulation software. The proprietary process model and parameter file of the PD from the process design kit was used [8]. The simulation files containing the device have been modified to accurately model the BPD presented in this paper. Using the extracted parameters of the photodetector, an electrical model is developed in Cadence simulation software. The electrical model for the BPD is presented in Fig. 3 where ISIG is the current though the 50 Ω load (RL) and IPD1 and IPD2 are the current through the complementary photodetectors. In the electrical model, the on-chip capacitors CG1 and CG2 provides a high speed ground to the load. The inductor in the DC supply (LLINE) is used to simulate it as a low speed transmission line. This model is used to estimate the electrical bandwidth of the BPD with the entire testing circuit included. In the analysis, it is assumed that the bandwidth of the PD is not limited by the transit-time of the absorbed photon in the intrinsic Ge-layer, therefore to estimate the electrical bandwidth of the PD, it is necessary to find the RC parasitic parameters of the electrical PD model. Using Sentaurus Device, the change in the parasitic capacitance of the single PD is analyzed under different reverse bias voltage conditions. With an increase in reverse voltage, the magnitude of the electric field across the Ge-silicon junction increases. Consequently, the effective depletion width increases and the capacitance decreases. Figure 4 shows the change in capacitance per unit length versus applied reverse bias voltage. At 0 V reverse bias voltage, the capacitance per unit length is approximately 1.65 fF/μm. The parasitic capacitance is 43 fF (CPD1 = CPD2) for the 26-μm long PD designed. The area of the PD metal pads is 75 μm by 75 μm with a pitch between pads of 100 μm. The corresponding capacitance is determined to be approximately 19 fF (CPAD1 = CPAD2) using the design tool HFSS by ANSYS. As the series DC block capacitor is in the order of tens of picofarads, the total parasitic capacitance in each of the PD is estimated to 62 fF. This value of capacitance is comparable with the value reported in [10], where Ge layer dimension was set at 7.4 μm × 50 μm and the intrinsic Ge thickness was 700 nm. The capacitance of each of the fabricated PD is also measured with a Keithley precision LC meter. The measured capacitance is 75 ± 7.5 fF. It is known that with the increase in Ge-layer area, parasitic capacitance increases, which adversely affects the bandwidth of the PD, whereas longer Ge layer length increases the responsivity of the PD [10]. #199407 - $15.00 USD Received 14 Oct 2013; revised 5 Dec 2013; accepted 7 Dec 2013; published 24 Dec 2013 (C) 2013 OSA 30 December 2013 | Vol. 21, No. 26 | DOI:10.1364/OE.21.032680 | OPTICS EXPRESS 32684 1.8 Capacitance (fF/um) 1.7 1.6 1.5 1.4 1.3 1.2 1.1 1 0 1 2 3 Reverse bias (V) 4 5 Fig. 4. Junction capacitance per unit photodetector length as a function of reverse bias voltage (positive voltage on n-type Ge). The targeted RC parameter for a given bandwidth and the responsivity of PD will determine the Ge and Si active area of the PD. It is difficult to find the parasitic resistance of the PD, RPD [11], as the parasitic resistance is fabrication dependent from doping concentration and area in the active Si and Ge layers. To estimate RPD in simulation, the contact resistance of Si-metal, the Ge-metal layer contact as well as the lateral resistivity of the Ge and Si layers are considered. Contact resistivity of Ge and Si with the metal layer 1 (M1) is 500 Ω-μm2, provided by OpSIS [8]. This contact resistivity and the sheet resistance of Ge and Si are found to estimate the series PD resistance to RPD1 = RPD2 = 57 Ω. From Fig. 2, a fixed value for the DC block capacitance (CG1 = CG2 = 14 pF) is chosen for the entire range of frequency to find the electrical bandwidth of the model. The PDs are replaced by a p-n junction model. As one PD is in the ‘off state’ at a given cycle, its parasitic capacitance appears in parallel with the PD in the ‘on state’. Therefore the bandwidth of the BPD becomes nearly half of that of the single signal PD. However, the on-chip capacitors and parasitic inductors from the low frequency DC line bring the parasitic capacitor from the PD in ‘off’ state to not truely be in parallel with the ‘on’ state PD’s capacitance. Consequently, the resulting bandwidth of the BPD is slightly higher than half the bandwidth of the single PD. Figure 5 shows the normalized frequency response of the BPD circuit with respect to frequency. The 3-dB cutoff frequency of the model circuit is ~18.48 GHz. Normalized resoponse (dB) 0 -2 -3 dB -4 -6 18.48 GHz -8 0.1 1 10 Frequency (GHz) 100 Fig. 5. Normalized frequency response of the BPD. 3. Results and discussion In this section, the experimental response of the BPD is discussed. The signal from the GSG pads of the BPD in Fig. 1 is collected with a 50 Ω probe. The photodetector is designed in a way that the differential signal from the two photodetectors is available at the “S” pad in Fig. 1. All the results presented are for the combined balanced photodetector unless mentioned otherwise. The total dark current in the BPD with a bias of −1 V measured with a #199407 - $15.00 USD Received 14 Oct 2013; revised 5 Dec 2013; accepted 7 Dec 2013; published 24 Dec 2013 (C) 2013 OSA 30 December 2013 | Vol. 21, No. 26 | DOI:10.1364/OE.21.032680 | OPTICS EXPRESS 32685 Keithley high precision picoammeter is ~4.31μA. The responsivity of the photodetector is presented in Fig. 6 as a function of the optical wavelength at −4.5 V bias. To measure the responsivity of the photodetector, the optical power at the input of the photodetector is estimated taking into account the measured grating coupler loss of 8 dB. A test device, a straight waveguide, was designed next to the photodetector to determine the grating coupler loss. After subtracting the dark current, the responsivity of the photodetector is measured at DC for CW optical signal at wavelength from 1525 nm to 1565 nm. The responsivity of each of the photodetectors in the BPD is ~0.7 A/W at 1550 nm, which is higher than 0.59 A/W reported in [12]. The improvement in the responsivity is due to the longer Ge section compared to [12]. 0.8 PD 1 PD 2 Responsivity (A/W) 0.7 0.6 0.5 0.4 0.3 0.2 1525 1530 1535 1540 1545 1550 1555 1560 1565 Wavelength (nm) Fig. 6. Responsivity as a function of wavelength. 50 -4.5 V -4 V -3 V -1 45 -2 -3 40 -4 -5 CMRR (dB) Normalized response (dB) 0 35 -6 CMRR -7 -8 5 10 15 20 25 30 30 Frequency (GHz) Fig. 7. Normalized amplitude response as a function of frequency. The frequency response of the BPD for different reverse biases is presented in Fig. 7. It is observed that with a bias of −4.5 V the balanced photodetector has a 3-dB bandwidth of approximately 16.2 GHz. An increase of the bias voltage beyond −4.5V does not improve the bandwidth. The experimental bandwidth is slightly lower than the simulated bandwidth likely due to differences between the simulated RC parasitic extraction and experimental RC parameters. The common mode rejection ratio (CMRR) is also presented in Fig. 7. The measured value of CMRR is well above 30 dB for all the frequencies. The performance of the of the balanced photodetector is evaluated in a 20 Gb/s return-tozero differential phase shift keying (RZ-DPSK) system using the experimental set up in Fig. 8. A continuous wave (CW) light from a tunable laser source from Yenista Optics has a wavelength of 1550.6 nm and an output power of 10 dBm. The CW light is injected into a 10.7 Gb/s Mach-Zehnder modulator (MZM). The MZM has 7 dB insertion loss. A sinusoidal clock signal at 10 GHz is fed into the first modulator which is biased at the maximum of the transmission curve. The second 40 Gb/s MZM is biased at the minimum of the transmission #199407 - $15.00 USD Received 14 Oct 2013; revised 5 Dec 2013; accepted 7 Dec 2013; published 24 Dec 2013 (C) 2013 OSA 30 December 2013 | Vol. 21, No. 26 | DOI:10.1364/OE.21.032680 | OPTICS EXPRESS 32686 and driven by a 20 Gb/s data to generate the desired DPSK signal. The experiment is performed at 20 Gb/s due to the availability of the 20 Gb/s DPSK demodulator in our laboratory. The pattern generator was loaded with a 231-1 pseudo random bit sequence (PRBS) and drives the second MZM. The optical signal is amplified using an erbium doped fiber amplifier (EDFA). The signal power is controlled using a variable optical attenuator (VOA). A commercial 20 Gb/s DPSK demodulator at 1550.6 nm is used to demodulate the signal. The results of bit error rate (BER) tests with a RZ-DPSK signal over 1 m of single mode fiber (SMF) are presented in Fig. 9. It is observed that with balanced detection and without any electrical amplification the photodetector has a sensitivity of −6.95 dBm with 28.5 mVpp. The results of the measurements at only the constructive (cnstr.) and destructive (destr.) port using single photodetector are also presented in Fig. 9. The sensitivity in this case is −3.84 dBm which is 3.1 dB worse than balanced detection. Fig. 8. Experimental setup for the performance evaluation of the RZ-DPSK signal. Fig. 9. BER as a function of received optical power at the chip (coupling loss of 8 dB deducted). In order to verify the suitability of the photodetector at higher bit rates the results of BER tests with a non-return to zero (NRZ) on off keyed (OOK) signal at 1550 nm at 25 and 30 Gb/s are also presented in Fig. 9. In this case a single 40 Gb/s MZM biased at the maximum transmission bias is used and directly driven by a 231-1 PRBS sequence from the pattern generator. The results show that for 25 Gb/s the BER is 1.01 × 10−12 for a received power of −1.65 dBm. The output voltage swing in this case was about 48 mVpp. For a received power of −3.66 dBm, the BER is degraded to ~10−9. At 25 Gb/s, the photodetector operates over the hard and soft-decision forward error correction (FEC) threshold of 3 × 10−3 and 1.8 × 10-2, respectively [13]. These results confirm that the BPD is suited for a 4 × 25 Gb/s coherent receiver and 25 GBaud differential phase shift keying (DPSK or DQPSK) demodulator applications. At 30 Gb/s the best BER is observed at the received optical power of −1 dBm. The BER of 3.98 × 10−4 is above both hard and soft-decision FEC limit as well. Therefore, the BPD has the possibility of being used at higher bit rates when used with FEC and DSP techniques. At 25 Gb/s neither FEC nor DSP is required for short reach applications. It should #199407 - $15.00 USD Received 14 Oct 2013; revised 5 Dec 2013; accepted 7 Dec 2013; published 24 Dec 2013 (C) 2013 OSA 30 December 2013 | Vol. 21, No. 26 | DOI:10.1364/OE.21.032680 | OPTICS EXPRESS 32687 be noted that the sensitivity of the photodetector would improve if post-amplification is applied after the photodetector before BER testing. Recent results with post amplification show a sensitivity of −7.3 dBm at 28 Gb/s using a Ge on Si photodetector [14]. 4. Packaged balanced photodetector The monolithic chip is packaged into a ceramic substrate as shown in Fig. 10(a) using an alumina-based board with a thickness of 0.254 mm (10 mils), with a dielectric constant εr = 9.9 and loss tangent δ = 0.0003 at10 GHz. The conductor material is silver (Ag) with a thickness of 1 µm. The required transmission line width calculated using Agilent ADS LineCalc is 0.246 mm (9.7 mils) at 30 GHz. The board is then attached to a metal base for support. The chip is attached to the metal base using a silver base epoxy. The GSG pads of the chip are wire bonded to the traces on the ceramic board. The RF connection is made through a 2.92 mm 40 GHz connector. The DC connections are provided using low frequency SMA connectors. (a) (b) Fig. 10. (a) Packaged balanced photodetector and (b) normalized frequency response of the packaged balanced photodetector. The measured frequency response of the package is presented in Fig. 10(b) with a 3-dB bandwidth of 15.9 GHz. The eye diagram of the signals at 25 Gb/s and 31 Gb/s are presented in Figs. 11(a) and 11(b), respectively. The results show a negligible degradation of bandwidth of 300 MHz compared to the unpackaged bandwidth. The results demonstrate the practical use of the BPD monolithic chip in a stable RF package. Fig. 11. Eye diagram of the packaged balanced photodetector for single ended input NRZ OOK signal (a) at 25 Gb/s and (b) 30 Gb/s. #199407 - $15.00 USD Received 14 Oct 2013; revised 5 Dec 2013; accepted 7 Dec 2013; published 24 Dec 2013 (C) 2013 OSA 30 December 2013 | Vol. 21, No. 26 | DOI:10.1364/OE.21.032680 | OPTICS EXPRESS 32688 5. Conclusion In this paper, a balanced photodetector (BPD) with on-chip biasing capacitor is designed and fabricated using CMOS compatible 220 nm Si on 2 µm SiO2 based SOI technology. The photodetector exhibits a bandwidth of 16.2 GHz at −4.5V reverse bias. The photodetector exhibits a CMRR of 30 dB. The performance of the photodetector is evaluated in terms of bit error rate (BER) versus received optical power. For 20 Gb/s DPSK signal the sensitivity of the photodetector is −6.95 dBm with balanced detection. The results show that at 25 Gb/s a BER of 1.01 × 10−12 can be achieved for a received power of −1.65 dBm with a large output swing of 48 mVpp for NRZ-OOK signal. At 30 Gb/s BER of 3.98 × 10−4 is achieved with received optical power of −1 dBm. The on-chip capacitors make the device compact and suitable for monolithic integration. The on-chip bias circuit in silicon photonic greatly facilitates packaging of the BPD alone with insignificant bandwidth degradation. Overall, the photodetector has very good possibility of being used within coherent or DPSK/DQPSK receiver. Acknowledgments This work was supported in part by the Canadian Microelectronics Corporation (CMC), Natural Sciences and Engineering Research Council of Canada (NSERC) Vanier Canada Graduate Scholarship (CGS) and Canada Research Chair (CRC) in Photonic Interconnects program. The balanced photodetector (BPD) described in this paper was fabricated using the OpSIS service through IME-A*STAR in Singapore. The authors would like to thank Lukas Chrostowski, University of British Columbia, Vancouver, BC, Canada, Dan Deptuck, Canadian Microsystems Corporation (CMC), Kingston, ON, Canada, Glenn Cowan, Concordia University, Montreal, QC, Canada, Tom Baehr-Jones, Optoelectronic Systems Integration in Silicon (OpSIS) program, Newark, DE, USA and Michael Hochberg, University of Delaware, Newark, DE, USA for their useful discussions. #199407 - $15.00 USD Received 14 Oct 2013; revised 5 Dec 2013; accepted 7 Dec 2013; published 24 Dec 2013 (C) 2013 OSA 30 December 2013 | Vol. 21, No. 26 | DOI:10.1364/OE.21.032680 | OPTICS EXPRESS 32689