Biasing the CE Amplifier

advertisement

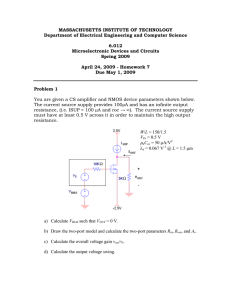

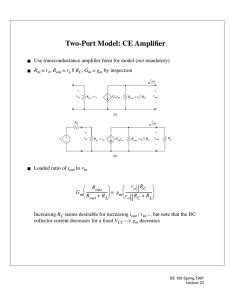

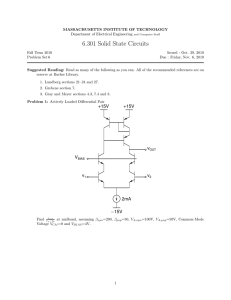

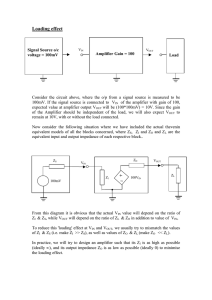

Biasing the CE Amplifier ■ Graphical approach: plot IC as a function of the DC base-emitter voltage VBIAS (note: normally plot vs. base current, so we must return to Ebers-Moll): V BE ⁄ V th V BIAS ⁄ V th = ISe ( forward active ) IC = ISe Load line for RC = 10 kΩ; range of variation for VBIAS is only 600 mV - 660 mV IC (mA) 0.66 1.0 VBIAS (V) 0.5 4 0.64 3 0.62 2 0.6 1 0 1 2 3 4 VCE = VOUT (V) 5 (a) VOUT HighGain Region 5V 1 2 3 4 0.62 V VBIAS (b) EE 105 Spring 1997 Lecture 17 Transfer Curve ■ The load line was plotted, assuming that VCC = 5 V and that the collector resistor RC = 10 kΩ, with the equation: 1 I C = ------- ( V CC – V OUT ) R C The transfer curve is defined by intersections between the load line IC (VOUT) and the family of collector current characteristics IC(VBIAS, VOUT) ■ Where to operate? Maximize potential “swing” in vOUT by placing VOUT halfway between cutoff and saturation ... (5 V + 0.2 V)/2 = 2.5 V (approx.) Solve for the input bias voltage: IS = 10-15 A V CC – V OUT V CC I C = -------------------------------- ≈ ----------- = 0.25 mA 2R C RC I C 250 µA V BIAS = V th ln ----- = ( 26 mV ) ln -------------------- = 682 mV – 15 IS 10 A The operating point is defined by: Q(VBE = 0.682 V, VCE = 2.5 V, IC = 250 µA) EE 105 Spring 1997 Lecture 17 Small-Signal Model of CE Amplifier ■ The small-signal model is evaluated at Q; we assume that the current gain is βo = 100 and the Early voltage is VAn = 25 V: gm = IC / Vth = 10 mS (at room temperature) rπ = βo/ gm = 10 kΩ ro = VAn / IC = 100 kΩ ■ Substitute small-signal model for BJT; VCC and VBIAS are short-circuited for small-signals iout + vπ _ rπ gmvπ ro + vout RC − (a) iout RS + vs + − vπ _ + rπ gmvπ ro RC RL vout _ (b) EE 105 Spring 1997 Lecture 17 Two-Port Model: CE Amplifier ■ Use transconductance amplifier form for model (not mandatory) ■ Rin = rπ, Rout = ro || RC, Gm = gm by inspection iout + vin _ Rin = rπ Gmvin Rout = ro RC + vout − (a) iout RS + vs + − vin _ + Rin = rπ Gmvin Rout = ro RC vout RL − (b) ■ Loaded ratio of iout to vin R out ro RC G m ------------------------ = g m ------------------------------ R out + R L r o R C + R L Increasing RC seems desirable for increasing iout / vin ... but note that the DC collector current decreases for a fixed VCC --> gm decreases EE 105 Spring 1997 Lecture 17 Common-Source Amplifier ■ Configuration is similar to common-emitter VDD VDD RD RD iOUT = IOUT + iout RS vs VBIAS + + − vOUT = VOUT + vout RL − + − (a) ■ VBIAS + VOUT _ + − (b) Bias: remove source and load resistances (b) EE 105 Spring 1997 Lecture 17 Graphical Load-Line Analysis ■ Load line is given by: I D = ( V DD – V OUT ) ⁄ R D ID (mA) 1.0 4 0.9 VBIAS (V) 0.5 4 3 3 0.25 2.5 2 0.10 0 VBIAS ≤ VTn = 1 V 2 1 1 2 3 4 5 VDS = VOUT (V) (a) VOUT HighGain Region 5V 1 2 3 4 2.5 V VBIAS (b) EE 105 Spring 1997 Lecture 17 Small-Signal Model of CS Amplifier ■ Substitute parameters at operating point selected so that V OUT ≈ V DD ⁄ 2 iout + + vgs gmvgs ro RD vout − − (a) iout RS + vs + − vgs gmvgs ro RD RL + vout − − (b) Transconductance is proportional to ID1/2 unlike bipolar transistor EE 105 Spring 1997 Lecture 17 Two-Port Model of Common-Source Amplifier ■ Use transconductance amplifier form for model (most natural choice) Rin = infinty, Rout = ro || RD, Gm = gm by inspection iout + vin + Gmvin Rout = ro RD vout − − (a) iout RS + vs + − vin + Gmvin Rout = ro RD vout − RL − (b) Infinite input resistance is ideal for a voltage input Output resistance increases with RD increasing, but DC drain current ID will decrease and gm will decrease with ID1/2 EE 105 Spring 1997 Lecture 17 Current-Source Supplies ■ A current source to supply current, rather than a resistor, allows a high DC current for the device with a large incremental (small-signal) resistance iSUP + + vSUP vSUP iSUP − roc ISUP − (a) iSUP 1 roc ISUP roc vSUP (b) (c) EE 105 Spring 1997 Lecture 17 Common-Source with Current Source Supply ■ RD is replaced with idealized current source with internal resistance VDD VDD iSUP ISUP iOUT = IOUT + iout + RS vs VBIAS vOUT = VOUT + vout + − − + − (a) ■ + VOUT RL VBIAS + − − (b) For DC bias analysis, the small-signal source (with RS) and the load resistor RL are eliminated, along with the internal resistance roc of the current source EE 105 Spring 1997 Lecture 17 Graphical Analysis of CS Amplifier with Current-Source Supply ID (mA) 1.0 4V 0.9 VBIAS 0.5 3V 0.25 2 3 4 2.5 V 2V 0.10 0 VBIAS ≤ VTn = 1 V 1 1 2 3 4 5 VDS = VOUT (V) (a) HighGain Region VDD 1 2 3 4 0 0 2.5 V VBIAS (b) ■ The region of input bias voltage VBIAS for which the current source and the MOSFET are in their constant-current regions is extremely small .... EE 105 Spring 1997 Lecture 17 Common-Source/Current-Source Supply Models ■ The small-signal model is identical to the resistor supply, except that the current source’s internal resistance roc replaces RD iout + + vgs gmvgs ro roc vout − ■ − Two-port model in both transconductance and voltage amplifier forms (the latter by direct conversion from the former ... by applying procedure for finding Av) iout + vin Gmvin − (a) Rout iout Rout + vin − + − Avvin = −GmRoutvin + vout − (b) EE 105 Spring 1997 Lecture 17 p-Channel Common-Source Amplifier ■ Source of p-channel is tied to positive supply; current supply sinks ISUP to ground or to lower supply VDD VDD RS vs + − VBIAS + − iOUT = IOUT + iout VBIAS + vOUT = VOUT + vout iSUP + − RL _ (a) ■ ISUP + VOUT _ (b) Small-signal model: substitute p-channel model directly EE 105 Spring 1997 Lecture 17 p-Channel CS Small-Signal Model ■ Source is at top, but circuit can be inverted to show correspondence with nchannel common-source amplifier s + vsg gmvsg ro − − roc vout + g d iout (a) iout g d − vsg gmvsg ro + + roc vout − s (b) iout g d + vgs gmvgs − ro + roc vout − s (c) EE 105 Spring 1997 Lecture 17 Common Base / Common Gate Amplifiers ■ Input signal is applied to the emitter, output is taken from the collector ■ Summary: current gain is about unity, input resistance is low, output resistance is high a CB stage is a good current “buffer” ... it takes a current at the input that may have a relatively small Norton resistance and replicates it at the output port, which is a good current source due to the high output resistance. V+ V+ iSUP ISUP iOUT IOUT RL is RS IBIAS V− IBIAS V− (a) (b) Biasing is very easy ... IBIAS = - ISUP, with a small correction factor due to the fact that βF isn’t infinity EE 105 Spring 1997 Lecture 17 Common-Base Current Gain Ai ■ Small-signal circuit, with output shorted (according to the procedure) iout ib + vπ − gmvπ = βoib rπ ve ro roc it i out Analysis: i out = i c ≈ β o i b and i c = – i e – i b = – i t – i b = – i t – --------β o Solving for the short-circuit current gain: i out –βo A i = --------- = --------------- ≅ – 1 it 1 + βo EE 105 Spring 1997 Lecture 17