Lead free - Weichloeten.de

advertisement

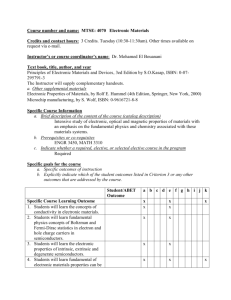

“Lead free” Status in the Semiconductor Industry (E3) and at Philips Semiconductors R. Geppert Philips Semiconductor Marketing and Sales Quality Manager, Area Central 2004-09, Hamburger Lötzirkel, “Leadfree Soldering” Content • • • • • Legislation / RoHS conformity Supply chain J-STD 020 Technology Status at Philips Semiconductors Semiconductors 2 Opening Statement: Main part of this document is based on a joint activity of STM / Philips SC / IFX (E3) on leadfree packaging The E3 initiative was formed in 2001 to push for standards, share workload and to give best support for our customers Recently, Freescale Semiconductor joined to form “E4” Semiconductors 3 Legislation Effect of EU Directive • On 13th of February 2003, directive 2002/95/EC of the European Parliament and of the Council of 27th January 2003 on the Restriction of the use of certain Hazardous Substances in electrical and electronic equipment (RoHS) entered into force. The directive will be applicable throughout EU by 1st July 2006 for the ban on the use of certain substances including lead (Pb) • Considering that semiconductor devices as well as finished electronics can be stored before usage or selling, conversion to lead-free should take place with suitable advance on the 1st July 2006 deadline Semiconductors 4 Leadfree / RoHS Overview and status Philips Semiconductors: Substance banned (not present) Cadmium Mercury Chromium-VI PBB and PBDE Lead 9 9 9 9 “Leadfree” program ==> All products are RoHS compliant after Leadfree conversion! Semiconductors 5 Target / Status: What is “lead free” ? • Phase 1: Lead (Pb) free terminals – Matte Tin (Sn100) or NiPdAu solution for (leaded) packages – Lead free solder spheres (SnAgCu) for BGA packages • Phase 2: Lead (Pb) free board soldering process – higher temperature needed – assess package MSL and reliability of lead free soldering process • Phase 3: Lead (Pb) free inside package (partially exempted) – lead free die attach (alloy) – lead free solder bumps (flip chip) Semiconductors 6 Target / Status Pb-free Programs in the Industry Two Targets: • Compatibility with both SnPb and Pb-free board soldering (with extended temperature range) • Elimination of Pb in package terminals (leads, balls, bumps) Status • Japan consumer market substantially converted to lead-free soldering in 2002 • Ramp up of Pb-free components shipment in volume in 2003 • Philips Semiconductors: – “Discretes”: – “IC packages”: Semiconductors SMD-packages completed Q3/03, others Q4/04 majority of packages finished by Q1/05 7 Supply Pipeline (worst case) Supplier Customer Customer Stock FIFO Stock Lead Leadfree Product age at delivery: max. 12 months ICs max. 24 months Discr. up to 12 months In total: up to 24 / 36 months ! Semiconductors 8 Standardisation IPC/JEDEC J-STD-020B, and upcoming -020C • E3 procedures are conform with the J-STD-020B • Existing results are compliant to J-STD-020B • Enhanced conditions for small packages: STM, Philips and Infineon agree to introduce an additional profile with 260°C -5/+0 °C for testing MSL of small devices at higher temperature. • New J-Std-020C increases temperature stress by setting the limits to -0/+5°C Semiconductors 9 MSL practise, 020C based New Test conditions due to J-STD-020C Source: SNW-FQ-225B 2004-04-02 260°C-Rework compatibility test started in April 2004. Plan : all packages will be re-classified in Q1/05. Semiconductors 10 Convection Solder Flow Requirements, based on JSTD-020C: Tp tp Max Ramp Up Rate = 3oC/s Max Ramp Down Rate = 6oC/s Temperature TL Tsmax Tp - 5oC tL Preheat Area Tsmin ts 25 0 o Time 25 C to Peak Time Reflow Condition Average ramp-up rate (TL to Peak) Preheat - Temperature Min (Tsmin) - Temperature Max (Tsmax) - Time (min to max) (ts) Tsmax to TL - Ramp-up Rate Time maintained above: - Temperature (TL) - Time (tL) Peak Temperature (Tp) Time within 5°C of actual Peak Temperature (tp) Ramp-down Rate Time 25°C to Peak Temperature Semiconductors SnPb Process Pb-Free Process 3°C/second max. 3°C/second max. 100 °C 150 °C 60-120 seconds 150 °C 200 °C 60-180 seconds 3°C/second max. 3°C/second max. 183°C 60-150 seconds See Table 2-1 10-30 seconds 6°C/second max. 180-360 seconds. 217°C 60-150 seconds See Table 2-2 20-40 seconds 6°C/second max. 300-480 seconds Source: Philips Semiconductors, SNW-FQ-225B 11 MSL statements • About 500 different packages tested in the 3 companies according to the agreed profiles, following JEDEC Higher MSL as temporary action, STD-020B for the prequalification of new materials conditioning process and for (ongoing) as short/mid term action failure criteria. 245°C profile applied to large packages (>350mm3) and 260°C applied to small packages (<350mm3) • With present materials and package design, in specific cases an increase in MSL Source Infineon classification may be observed • Plus 10°C means MSL up one level! (020C effect) Semiconductors 12 Technology Consolidated lead free solutions: For lead frame based packages: • Post plate of matte tin (Sn) • Pre plate of NiPdAu For Ball Grid Array packages: • SnAgCu Semiconductors 13 Technology Postplate of matte tin (Sn) Main characteristics: • • • • • Material availability is good Closest to SnPb in cost and process Good solderability with PbSn and Pb free solders Good solderjoint reliability “Whisker free” process available 1) ( 1) See whisker presentation ) Semiconductors 14 Whisker on Cu Whisker Mechanism Whiskers grow because of compressive stress in the plating which is caused by irregular growth of intermetallics Tin Whisker is forced out Cu6Sn5 Sn Deposit Whisker Cu Substrate Cu6Sn5 Semiconductors Source: Philips 15 Whisker on Cu Storage conditions • Test data showed that whiskers grow longest at room temperature • Explanation: irregular intermetallic growth 1,9 µm ambient 250 length of longest whisker in µm 1,9 µm 55 °C / ambient 1,9 µm 85 °C / 85 % r.h. 200 150 longest whisker broken, continued with second longest 100 50 time in days 0 0 Semiconductors 50 100 150 200 250 300 Source: Infineon 16 Whisker on Cu 1,82 µm 3.5 µm 5.35 µm 7.10 µm length of longest whisker in µm 10.10 µm Source: STMicroelectronics 160 Protection by Thickness Thicker Sn layer can absorb more stress. Note: irregular intermetallics still present! Sn-plating @ Room Temperature 120 80 40 0 Semiconductors 0 50 100 150 200 250 time in days 700 750 17 Whisker on Cu Protection by Post bake (1h, 150 oC) Longest Whisker (µm) No whiskers have been detected after postbake of 1 hour at 150 oC for any thickness of Sn plating up to 1 year after plating and storage at ambient temperature and atmosphere. 30 2 µm Sn 5 µm Sn 10 µm Sn 20 10 0 0 100 200 300 400 Time (days) Semiconductors Source: Infineon, STMicroelectronics, Philips 18 Whisker on Cu Protection by Post bake (1h, 150 oC) • Because of higher temperature diffusion will shift from grain boundary to bulk diffusion and thus regular intermetallics • Annealing of stress No whisker! Bulk diffusion Cu6Sn5 Sn Deposit Cu Substrate Semiconductors 19 Technology Preplate NiPdAu Main characteristics: • • • • Good solderability with PbSn and Pb free solders Good solder joint reliability Used in high volume Offered by major lead frame suppliers Semiconductors 20 Technology SnAgCu Spheres in Ball Grid Array Main characteristics: • • • • SnAg3.0-4.0Cu0.5-1.0 is the most applied range Good solderability with Pb free solders Offered by all major suppliers Limited backward compatibility with SnPb solders Semiconductors 21 L/F packages Compatibility customer Pb - solder supplier Pb - solder Increase temp. by 20°C component finish Pb Pb Semiconductors Today Processability: o.k. Experience of some Solderability: o.k. decades of board assembly Reliability: o.k. (NCMS-, IDEALS-report,internal evaluations) Processability: o.k. Processability: o.k. Solderability: o.k. Solderability: o.k. Reliability: o.k. Reliability: o.k. 22 L/F packages Processability Processability in lead containing vs. lead-free process • For reflow soldering: paste application, component placement do not require special measures • For wave soldering: glue application, component placement, glue cure do not require special measures • Differences in soldering process are time and temperature • SnPb plating and Sn plating do not show a different behavior in the soldering processes (more than a decade of experience!) Semiconductors 23 L/F packages Processability Reflow solder joints Lead containing solder Backw ard Com patibility SC SnPb36Ag2 Lead-free solder 300 260 260 250 205 200 150 FQFP208 HVQFN48 VSO56 HTQFP100 SO28 100 50 0 Temperature in degree C Temperature in degree C Backw ard Compatibility SC, reduced dT SnAg3.8Cu0.7 300 250 235 200 150 FQFP208 100 HVQFN48 VSO56 50 HTQFP100 SO28 0 0 100 200 300 400 0 60 120 Tim e in seconds Only slight differences of wetting ( ) , fillet ( Surface: less shiny for lead-free (see inserts) Semiconductors 180 240 300 360 420 Tim e in seconds ) Source Philips 24 L/F packages Processability Wave solder joints Lead containing solder Lead-free solder Process Process speed [m/min] Total soldering time/temp Pre-heat temperature Leaded 1.25 2.75±0.25s / 250°C 120±10°C Lead-free 1.2 3.75±0.25s / 265°C 120±10°C Semiconductors Only difference: somewhat less shiny with lead-free Source Philips 25 L/F packages Reliability Temperature Cycling as reliability test for solder joint • Temperature cycling causes thermo-mechanical solder fatigue • Degradation/failure goes along the following path: – Diffusion and re-crystallization – Crack initiation and growth – Failure by macroscopic solder fracture • Solder fatigue failure is visualized and analyzed according Weibull statistics Semiconductors 26 L/F packages Reliability Weibull analysis of failure in temperature cycle test (-40/125 oC) lead-free and lead-containing reflow solder Sn plated VSO56 (FeNi42-leadframe) VSO56, reflow ln[1/(1-f)] 10 1 SnPb SnAgCu 0,1 0,01 100 1000 10000 N cycles Source Philips Semiconductors 27 BGA packages Compatibility customer Pb - solder supplier Pb - solder Increase temp. by 20°C component finish Pb Pb Today Processability: o.k. Experience of some Reliability: o.k. Processabilty below 230°C critical Processability: o.k. Reliability: o.k. (improved to SnPb) Reliability: o.k. decades of board assembly For low temperatures critical Semiconductors 28 BGA Processability Motivation: For array-package the processability has been tested. Different temperature at the ball result in different mounting height. Conclusion: The combination lead-free BGA/SnPb-paste can be processed with a minimum temperature of 230°C (at the ball). Due to restricted self-alignment, a peak temperature at 220°C should only be chosen in exemptional cases decreasing mounting height Beginning melting Complete melting, final height Peak temperatures over 230°C are recommended mounting height bad joint good solder joint with limited drop good solder joint Source Infineon Semiconductors 29 Conclusion Leadframe packages: • Sn-plating or NiPdAu-plating will be introduced as lead-free technology's • For leadframe packages there is a full compatibility to SnPb- and Pb-free solder process BGA packages: • For BGA packages SnAgCu is the chosen metallurgy • On board reliability is proven • In the case of BGA-packages the soldering temperature must be above 230°C for processability Please note: The major conversion will take place in 2004: Now ! Semiconductors 30 Current Status at Philips Semiconductors Compatibility “Lead” vs. “Lead Free” • Backward Compatibility – Pb free products in Pb-containing soldering process: – Report (.pdf) available • Forward Compatibility – MSL re-assessment done (J-STD-020B !!), check MSL value on label Semiconductors 32 Conversion Status / Roadmaps - 1 Discretes: Semiconductors 33 Semiconductors 34 Pb-free / Green Indicators Semiconductors 35 Pb-free/Green Identification on Packing Semiconductors 36 Pb-free/Green Identification on Component Semiconductors 37 PS approach to logistics control • • No change in part numbers and 12NC when we introduce leadfree products Lead and leadfree products flow will be separated by – – • • • • • One packing quantity (PQ) No mix of PQs in one box Traceability will be by date code Separate stores for lead and leadfree products Leadfree products will be identified by a marking on the product (where space allows) Packaging will be marked by a leadfree sticker on the box The Leadfree symbol will be printed on the label – At Packing Quantity level (box/reel – not tube) Semiconductors 38 Discontinuation of Products ? • No product will be discontinued only because of L/F conversion (see normal DN distribution) • BGA types will get new P/N Semiconductors 39 Please visit our Internet for further details www.semiconductors.philips.com/green_roadmap/ Semiconductors 40 Semiconductors 41 Early Information: Chemical Content SOT612CB3 HLQFP144 Total Product weight: 1.30 g Part Leadframe Material CuCr Cu Cr Details 100 % 99.25 % 0.3 % Weight 0.27 g 0.268 g 0.002 g Leadfinish SnPb15 Sn Pb 100 85 15 0.05 g 0.04 g 0.01 g % % % etc. Proh./ Res. Materials Cadmium < 100 ppm PBB < 100 ppm etc. Semiconductors Packing info Tube packing; Chemical contents Tray packing ; Chemical contents analyses/ reports DISCLAMER STATEMENT 42 Thank you for your attention. Any Question? Semiconductors 43 IMDS . . . . Semiconductors 44 Chemical Content information on Internet • Check following link: http://www.semiconductors.philips.com/ Semiconductors 45 Chemical Content information on Internet /2 • Enter product type, e.g.: 74HC00 • Wait for search results and then select link to “info” page Semiconductors 46 Chemical Content information on Internet /3 • You get all product related info, incl. “ChemCon”, when selecting ‘package’ link Semiconductors 47 Chemical Content information on Internet /4 Semiconductors 48