LOW COST ALTERNATING CURRENT AUTOMATED

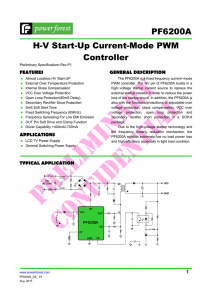

advertisement