Investigations, Developments and Applications in the Field of

advertisement

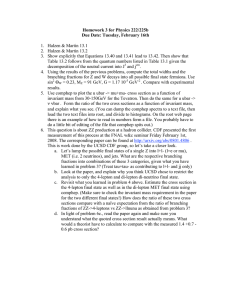

Investigations, Developments and Applications in the Field of Design and Testing of Digital Systems (1998-2002) Governmental Basic Financed Project Coordinator: Raimund Ubar Abstract The goal of the project was to investigate new methods for HW/SW codesign, analysis, simulation, verification and increasing the fault-tolerance of digital systems, low-power design, automated test program generation and fault diagnosis. This list of topics describes in a compact way the research activities of the Computer Engineering Department carried out during the last five years. As the result of the project a new approach was developed for diagnostic modelling of digital systems based on decision diagrams (DD) including traditional Binary DDs (BDD), Structurally Synthesized BDDs and High-Level DDs. New methods and algorithms were developed based on this DD-approach for test generation and fault simulation which allowed to improve the efficiency of fault analysis compared to the known methods. The novelty of the new DD-based model was in creating of a uniform mathematical basis for diagnostic modelling of digital systems which allowed to cope better with the complexity problem and to increase the accuracy of simulation. Research activities of the teaching staff The scientific goals of the Department are closely related to the most actual research trends today in the field of computer engineering, e.g. to the highly recognized guidelines for design and test solutions of “The MEDEA Design Automation Roadmap”. MEDEA (MicroElectronics Development for European Applications) is a part of the pan-European EUREKA network for cooperative R&D in computer-aided design (CAD) and design automation. Information technology (IT) is a key technology today also for Estonia. New IT design companies are continuously entering the market in Estonia. One of the most successful SMEs in this field is Artec Design Group (ADG) who entered recently the USA market with new SOC – MachZ “PC-on-a-Chip”. A close cooperation with ADG is one of the driving goals of the Department to make the research results useful for Estonian industry in general. The methodology of the research carried out is strongly based on experimental investigations and proofs to show the adequacy of mathematical models and efficiency of algorithms. To be effective and efficient in research the laboratory environment has been created which supports diverse experimental scenarios involving various professional CAD (computer aided design) and CAT (computer aided test) SW tools or prototypes. Extending the laboratory environment by developing new prototype tools to enable efficient research and research oriented teaching is one of the main targets of the R&D activities of the Department. The most important scientific results have been achieved by the staff of the Department in the following directions: diagnostic modeling fof digital systems, test generation and fault simulation in digital systems, design error diagnosis, defect oriented fault analysis, decompositional design of digital systems, analysis and partitioning methods for hardware/software codesign, and unified representation of systems for control and memory intensive applications. In the following a summary of recent theoretical results of the Department is presented with references to the most important publications and to the main contributors (staff members or students). Summary of recent theoretical results of the staff (1998-2002) : In the field of digital test: 1. A novel diagnostic model for digital systems based on decision diagrams (DD) has been developed [21,26,31]. The model affords generalization of testing problems allowing uniform formal handling of sytems on logic, procedural, functional as well as behavioral levels (R.Ubar, J.Raik, A.Jutman). 2. A new hierarchical approach to test generation for digital systems was proposed [9,21,22, 32,34,36]. Combining the high-level efficiency of solving complex deterministic search problems and medium-level acuracy of fault analysis with low-level exact fault activation allowed to reach high efficiency and quality in test generation (R.Ubar, J.Raik, E.Ivask, M.Brik). 3. A uniform approach for solving logic tasks of digital test was developed [6,8,24]. The basis of the approach is the diagnostic model in form of structurally synthesized binary decision diagrams (SSBDD) which contrary to the known BDDs preserve structural features of circuits and allow to solve a lot of tasks from the test field not solvable by BDDs (R.Ubar, J.Raik, A.Jutman). 4. New methods for optimization of hybrid BIST for testing systems-on-chips are developed [3,10,13,27]. Two algorithms were created and compared to find the optimal balance between pseudorandom and stored test patterns to perform core test with minimum time and memory, without losing test quality. To speed up the optimization procedure, a Tabu search based method is proposed for finding the global cost minimum without calculating the full cost curve (R.Ubar, E.Orasson, H.Kruus, R.Raidma). 5. A novel hierarchical method for design error diagnosis [20,35] in combinational circuits was developed which is based on the stuck-at fault model and assumes the case of single logic gate errors. Using the stuck at fault model allows to exploit standard gate-level automated test pattern generators (ATPG) for design error diagnosis. Experimental data on international benchmark circuits showed the advantage of the proposed method compared to the known algorithms of design error diagnosis (R.Ubar, A.Jutman). 6. A new approach to increase the speed of high-level simulation of synchronous digital systems was developed based on using High-Level DD-s [1,25,26,33]. In order to fully exploit the advantages of DDs, new simulation algorithms which are combinations of forward event-driven and recursive back-tracing techniques were proposed (R.Ubar, J.Raik, E.Ivask, M.Brik). 7. A new method for defect oriented fault analysis [7,12] in VLSI has been developed. The method allows the first time to handle in test generation the defects which increase the number of states in the circuit. Experimental data of simulating defects showed that classical stuck-at fault methods lead to significant overestimation of test quality (R.Ubar, J.Raik). In the field of digital design: 8. New analysis and partitioning methods for implementation of arithmetic operations with very long number were developed [42]. The methods were used in the designing of a cryptographic processor where such operations play the key roles. The main result of the research was a reconfigurable modular multiplier in field programmable logic (FPL) technology (K.Tammemäe, J.Põldre, M.Mandre). 9. A new method to implement low power state machines have been developed in cooperation with Mid Sweden University [16]. This method combines decompositional synthesis of finite state machines with gated clock implementation. It allows a significant reduce in power consumption by partitioning state machines into component machines that are selectively turned off (K.Tammemäe, M.Kruus, A.Liiver). 10. A part of memory architecture organization methodology has been developed in cooperation with IMEC (Belgium) and Royal Institute of Technology (Sweden) [15,30,38]. This method analyses accesses to memories and guides memory architecture synthesis with the overall goal to reduce power consumption in memories. The above mentioned sub-task takes into account interdependencies of memory accesses and distributes variables into memory words (P.Ellervee). 11. Fast and simple heuristic optimization algorithms have been developed [19,30]. The algorithms allow a significant speedup in arhitecture exploration when it is more important to find a good enough estimate but not the optimal solution itself. Experiments have been made to validate the use of such sub-optimal solutions in allocation and binding tasks of high-level synthesis, as well as in memory architecture organization (P.Ellervee, T.Klaar). 12. A new unified internal representation for control and memory intensive applications was developed [30]. The internal representation allows the analysis and synthesis tools to exchange information without loss of specification details. The first version of a prototype tool, which uses this internal representation, was implemented at KTH (Sweden). The new methods, i.e., state machine partitioning, memory organization synthesis, and fast optimization heuristics, are being added to the tool currently at TTU (P. Ellervee, K. Tammemäe, E.Ivask, A.Sudnitsõn). 13. A new conceptual design methods and a new software environment for mechanical engineering CAD have been developed. These methods includes AI and visual programming principles. Experiments are here supported by special specifications languages and problem solvers (prof. A.Kalja). 14. Software process improvement related research projects on a regional basis have been initiated and supported by EU V Framework program. A comparison of software process assessment and improvement programs in Finland and Estonia has been performed. The prerequisites in a multi-organizational environment for successful software process assessment and improvement have been described (prof. A.Kalja). 15. A virtual laboratory has been created to support international cooperation in research and distance learning in topics which are teached at the Department (R.Ubar, T.Evartson, E.Ivask, J.Raik, A.Jutman, E.Orasson, S.Devadze) [2,4,5,11,23]. International scientific cooperation: Part of the listed results have been achieved in a very close cooperation with universities from West: in design error diagnosis with TIMA Laboratory in Grenoble [35], in high-level simulation with Institute National Polytechnique de Grenoble and Josepf Fourier University de Grenoble [25,26,30,33], in timing simulation of circuits and Built-in Self-Test synthesis with Linköping University [3,13,27], in defect-oriented testing with researches from Poland and Slovak Republic [2,7,12], in HW/SW codesign and high-level synthesis with TU Darmstadt and Royal University of Technology Stockholm [9,30], Mid Sweden University [16] and IMEC [15,28,37], in test generation with Fraunhofer Institute of Integrated Circuits in Dresden [2], and in development of teaching software with TU Ilmenau [5,11,23]. Applications: 1. Based on the new diagnostic model in form of DDs, a new automated test program generator (ATPG) called DECIDER for testing digital systems was developed [21,22,32,34]. In cooperation with German and Swedish researchers, a uniform SW system based on the DECIDER was developed for integrating design and test, which does not have an analog in the commercial market. Experimental results proved the high efficiency of DECIDER, and allow to conclude that it is faster than other known counterparts (R.Ubar, J.Raik). 2. A new toolbox TURBO-TESTER (TT) for solving different test synthesis and analysis tasks for digital circuits was developed [2,6,20,24]. Differently from other similar software, all tools in TT are based on a single universal model library to give the software the features like openness, simplicity and low-cost. TT has been used at universities in Finland and Sweden, in teaching the students of Michigan State University (USA), in continuous teaching of engineers in Sweden and elsewhere in Europe (R.Ubar, J.Raik, A.Jutman, P.Paomets, E.Ivask). 3. The first Estonian VLSI, a cryptographic processor was developed at the Department [42]: ECPD 1,0 micron CMOS technology, 107 mm2, 202 000 transistors. The prototype of the chip was manufactured in the silicon foundary ES2 by the support of European program EUROPRACTICE. The activities of the institute in the field of design has found an output in the cooperation with companies National Semiconductor and ZFMicro in USA and ARTEC Design Group in Estonia. A system on chip (SOC) has been designed, which implements the mainboard of the PC 486, and is currently marketed by ZF Linux Devices in USA (J.Põldre). Description of the doctoral study: In the recent three years 5 PhD thesis (K.Tammemäe, H. Krupnova, J.Dushina, P. Ellervee and J. Raik) have been supervised at the department. Currently, 8 PhD thesis are in progress (M.Brik, E.Ivask, P.Paomets, A.Jutman, J.Fomina, R.Vaarandi, I.Astrova, M.Lepasaar). All the research the students are running is closely related to the scientific goals of the Department. PhD students are presenting actively papers at international conferences, for example in 2000 and 2001 the listed 6 PhD students have been coauthors 42 times in 32 from total of 44 papers. MSc students have participated as co-authors in 4 papers. J. Raik and A.Jutman have been several times awarded for the best student work. From all the students currently involved in the MSc study, at least seven of them (J.Heinlaid, A.Liiver, M.Mandre, L.Raun, H.Kruus, T.Robal, V.Kostin) have planned to continue the research towards PhD degree. The level of the PhD research at the department is highly recognized on international hightech markets. Several former PhD students of the department are working now in top-level companies: H. Krupnova in STMicroelectronics in Grenoble (France), S. Storozhev is with US company MINC, J. Dushina in STMicroelectronics in Bristol (UK), Gert Jervan is continuing his PhD study in the topic taken from the department at Linköping University in Sweden etc. References: 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. 20. 21. R.Ubar, J.Raik, E.Ivask, M.Brik. Multi-Level Fault Simulation of Digital Systems on Decision Diagrams. IEEE Workshop on Electronic Design, Test and Applications – DELTA’02, Christchurch, New Zealand, 2931 January 2002, pp.86-91. A.Schneider, E.Ivask, P.Mikloš, J.Raik, K.H.Diener, R.Ubar, T.Cibáková, E.Gramatová. Internet-based Collaborative Test Generation with MOSCITO. IEEE Proc. of Design Automation and Test in Europe – DATE’02. Paris, March 4-8, 2002, pp. 221-226. G.Jervan, H.Kruus, Z.Peng, R.Ubar. About Cost Optimization of Hybrid BIST in Digital Systems. 3rd Int. Symp. on Quality of Electronic Design, San Jose, California, March 18-20, 2002, pp.273-279. R. Ubar, E. Orasson, T. Evartson. Java Applet for Self-Learning of Digital Test Issues. 13th EAEEIE Conference, York, Great Britannia, April 8-10, 2002. R.Ubar, A.Jutman, E.Orasson, J.Raik, T.Evartson, H.-D.Wuttke. Internet-Based Software for Teaching Test of Digital Circuits. 4th European Workshop on Microelectronics Education – EWME’02. Parador de Baiona, Spain, May 23-24, 2002. A.Jutman, R.Ubar, Z.Peng. Algorithms for Speeding-Up Timing Simulation of Digital Circuits. IEEE Proc. of Design Automation and Test in Europe – DATE, Munich, March 13-16, 2001, pp.460-465. R.Ubar, W.Kuzmicz, W.Pleskacz, J.Raik. Defect-Oriented Fault Simulation and Test Generation in Digital Circuits. 2nd Int. Symp. on Quality of Electronic Design, San Jose, CA, March 26-28, 2001, pp.365-371. J.Raik, A.Jutman, R.Ubar. Fast Static Compaction of Test Sequences Using Implications and greedy Search. Digest of European Test Workshop, Stockholm, May 29 – June 1, 20001, pp. 207-210. T.Hollstein, Z.Peng, R.Ubar, M.Glesner. Challenges for Future System-on-Chip Design. Proceedings of European Conf. on Circuit Theory and Design. Part III. Espoo, Finland, August 28-31, 2001, pp.173-176. R. Ubar, G.Jervan, Z.Peng, E.Orasson, R.Raidma. Fast Test Cost Calculation for Hybrid BIST in Digital Systems. Proc. of EUROMICRO Symposium on Digital Systems Design, Warsaw, September 4-6, 2001, pp.318-325. R.Ubar, H.-D.Wuttke. The DILDIS-Project – Using Applets for More Demonstrative Lectures in Digital Systems Design and Test. Proceedings of the 31st ASEE/IEEE Frontiers in Education Conference, FIE’2001, Oct. 10-13, 2001, Reno, NV, USA, pp.SIE-2-7. M.Blyzniuk, I.Kazymyra, W.Kuzmicz, W.A.Pleskacz, J.Raik, R.Ubar. Probabilistic Analysis of CMOS Physical Defects in VLSI Circuits for Test Coverage Improvements. Journal of Microelectronics Reliability. Pergamon Press. Vol 41/12, Dec. 2001, pp 2023-2040. H.Kruus, R.Ubar, G.Jervan, Z.Peng. Using Tabu Search Method for Optimizing the Cost of Hybrid BIST. XVI Conf. on Design of Circuits and Integrated Systems, Porto, Portugal, Nov. 20-23, 2001, pp.445-450. A. Jantsch, S. Kumar, I. Sander, B. Svantesson, J. Öberg, A. Hemani, P.Ellervee, and M. O'Nils, "A comparison of six languages for system level description of telecom applications." In Jean Mermet, editor, Electronic Chips & System Design Languages, chapter 15, pp.181-192. Kluwer Academic Publisher, 2001. P. Ellervee, M. Miranda, F. Catthoor, A. Hemani, "System-level Data-Format Exploration for Dynamically Allocated Data Structures." IEEE Transactions on CAD, Vol. 20, No. 12, pp.1469-1472, Dec. 2001. B. Oelmann, K. Tammemäe, M. Kruus, M. O’Nils, "Automatic FSM Synthesis for Low-Power Mixed Synchronous/Asynchronous Implementation." Special issue on Low Power System Design Issues of the VLSI Design Journal, Gordon and Beach Science Publishers, Vol. 12, No. 2, pp. 167-186, 2001. A.Kalja, V.Kotkas and T.Tiidemann. CAD Problem Solving and Technical Systems Modelling Using the AI Programming Environments. In: Information modelling and Knowledge Bases XII. H. Jaakkola et al. (Eds.) IOS Press, Amsterdam, 2001, pp. 284-290. M.Lepasaar, A.Kalja, T.Varkoi, H.Jaakkola. Key success factors of a regional Software Process Improvement Program. In: Proceedings Vol-1: PICMET'01 Book of Summaries. Portland, Oregon USA, July 29 - August 2, 2001, p. 432. P. Ellervee, T. Klaar, "Using Weighted Graph Coloring Heuristics for Architecture Exploration." The 19th NORCHIP Conference, pp.161-166, Stockholm, Sweden, Nov. 2001. A.Jutman, R.Ubar. Design Error Diagnosis in Digital Circuits with Stuck-at Fault Model. Journal of Microelectronics Reliability. Pergamon Press, Vol. 40, No 2, 2000, pp.307-320. J.Raik, R.Ubar. Fast Test Pattern Generation for Sequential Circuits Using Decision Diagram Representations. Journal of Electronic Testing: Theory and Applications. Kluwer Academic Publishers. Vol. 16, No. 3, pp. 213-226, 2000. 22. R.Ubar, J.Raik. Efficient Hierarchical Approach to Test Generation for Digital Systems. 1st Int. Symp. on Quality of Electronic Design, San Jose, California, March 20-22, 2000, pp. 189-195. 23. R.Ubar, H.-D.Wuttke. Action Based Learning System for Teaching Digital Electronics and Test. In “Microelectronics Education”, Kluwer Acad. Publishers, Dordrecht/ Boston/London, 2000, pp. 107-110. 24. E.Ivask, J.Raik, R.Ubar. Fault Oriented Test Pattern Generation for Sequential Circuits Using Genetic Algorithms. IEEE European Test Workshop, Cascais, Portugal, Mai 23-26, 2000, pp. 319-320. 25. R.Ubar, A.Morawiec, J.Raik. Back-Tracing and Event-Driven Techniques in High-Level Simulation with Decision Diagrams. Proc. of the IEEE ISCAS’2000 Conf., Geneva, May 28-31, 2000, Vol.1, pp.208-211. 26. R.Ubar, A.Morawiec, J.Raik. High-Level Decision Diagrams for Simulation Performance. Proc. of the World Multiconference on Systemics, Cybernetics and Informatics, SCI- 2000. Orlando, Florida, USA, July 23-26, 2000. Vol. IX Industrial Systems, pp.62-67. 27. G.Jervan, Z.Peng, R.Ubar. Test Cost Minimization for Hybrid BIST. IEEE Int. Symp. on Defect and Fault Tolerance in VLSI Systems. Tokio, October 25-28, 2000, pp.283-291. 28. P. Ellervee, M. Miranda, F. Catthoor, A. Hemani. System-level Data Format Exploration for Dynamically Allocated Data Structures. The 37th Design Automation Conference, pp.556-559, Los Angeles, USA, June 2000. 29. E. Dubrova, P. Ellervee, J. Muzio, M. Miller, "TOP: An Algorithm for Three-Level Optimization of PLDs." Design and Test in Europe (D.A.T.E.), pp.751, Paris, France, March 2000. 30. P. Ellervee, "High-Level Synthesis of Control and Memory Intensive Applications." Ph.D. Thesis ISRN KTH/ESD/AVH--2000/1--SE, Stockholm, 2000. 31. R.Leveugle, R.Ubar. Modeling VHDL Clock-Driven Multi-Processes by Decision Diagrams. J. of Electron Technology, Vol. 32, (1999) No.3, pp.282-287. 32. J.Raik, R. Ubar. Sequential Circuit Test Generation Using Decision Diagram Models. IEEE Proc. of Design Automation and Test in Europe - DATE. Munich, March 9-12, 1999, pp. 736-740. 33. R.Ubar, A.Moraviec, J.Raik. Cycle-based Simulation with Decision Diagrams. IEEE Proc. of Design Automation and Test in Europe - DATE. Munich, March 9-12, 1999, pp.454-458. 34. R.Ubar, J.Raik. Hierarchical Test Generation for Complex Digital Systems with Control and Data Processing Parts. In “Test, Assembly and Packaging”, SEMICON Technical Symposium, Singapur May 36, 1999, pp.43-52. 35. R.Ubar, D.Borrione. Design Error Diagnosis in Digital Circuits without Error Model. 10th IFIP Int. Conf. on VLSI’99. Lisboa, Dec. 1-4, 1999, pp.281-292. 36. J.Raik, R.Ubar. High-Level Path Activation Technique to Speed Up Sequential Circuit Test Generation. Proc. of IEEE European Test Workshop, Constance, May 25-28, 1999, pp.84-89. 37. P.Ellervee, M.Miranda, F.Catthoor, A.Hemani. Exploiting Data Transfer Locality in Memory Mapping. Proc. of the 25th Euromicro Conference, pp.14-21, Milan, Italy, Sept.1999. 38. T. Meincke, A. Hemani, S. Kumar, P. Ellervee, J. Öberg, T. Olsson, P. Nilsson, D. Lindqvist, H. Tenhunen, "Globally Asynchronous Locally Synchronous VLSI Architecture for large high-performance ASICs." International Symposium on Circuits and Systems (ISCAS'99), vol.II, pp.512-515, Orlando, Florida, USA, May 1999. 39. A. Hemani, T. Meincke, S. Kumar, A. Postula, T. Olsson, P. Nilsson, J. Öberg, P. Ellervee, D. Lundqvist, "Lowering Power Consumption in Clock by Using Globally Asynchronous Locally Synchronous Design Style." The 36th Design Automation Conference (DAC'99), pp.873-878, New Orleans, LA, USA, June 1999. 40. J.Sanko, M.Tiidemann, T.Tiidemann, A. Kalja. Calculation of Gear Drive by Using AI Methods in Conceptual Design. In: Proceedings of OST-99 SYMPOSIUM on Machine Design, KTH, Stockholm, 1999, pp 21-27. 41. A.Kalja, J.Oruaas. Overview of SPI activities in Estonia. In: Proceedings of the EuroSPI'99 conference, Series A - Pori School of Technology and Economics, No A 25, 1999, pp 8.41-8.47. 42. J. Põldre, K. Tammemäe, "Reconfigurable Multiplier for Virtex FPGA Family." The 9th Int. Conf on Field Programmable Logic and Applications (FPL'99), pp.369-364, Glasgow, UK, Sept. 1999.