B6 Bridge FET Driver with LIN/PWM Interface E523.01C, 02C, 11C

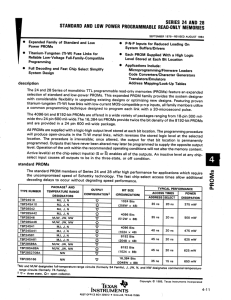

advertisement