a

800 MHz, 50 mW

Current Feedback Amplifier

AD8001

FEATURES

Excellent Video Specifications (RL = 150 , G = +2)

Gain Flatness 0.1 dB to 100 MHz

0.01% Differential Gain Error

0.025 Differential Phase Error

Low Power

5.5 mA Max Power Supply Current (55 mW)

High Speed and Fast Settling

880 MHz, –3 dB Bandwidth (G = +1)

440 MHz, –3 dB Bandwidth (G = +2)

1200 V/s Slew Rate

10 ns Settling Time to 0.1%

Low Distortion

–65 dBc THD, fC = 5 MHz

33 dBm Third Order Intercept, F1 = 10 MHz

–66 dB SFDR, f = 5 MHz

High Output Drive

70 mA Output Current

Drives Up to 4 Back-Terminated Loads (75 Each)

While Maintaining Good Differential Gain/Phase

Performance (0.05%/0.25)

APPLICATIONS

A-to-D Drivers

Video Line Drivers

Professional Cameras

Video Switchers

Special Effects

RF Receivers

FUNCTIONAL BLOCK DIAGRAMS

8-Lead PDIP (N-8),

CERDIP (Q-8) and SOIC (R-8)

NC 1

8

–IN

2

7

V+

+IN 3

6

OUT

5

NC

V– 4

5-Lead SOT-23-5

(RT-5)

AD8001

NC

VOUT 1

AD8001

5

+VS

4

–IN

–VS 2

+IN 3

NC = NO CONNECT

transimpedance linearization circuitry. This allows it to drive

video loads with excellent differential gain and phase performance on only 50 mW of power. The AD8001 is a current

feedback amplifier and features gain flatness of 0.1 dB to 100 MHz

while offering differential gain and phase error of 0.01% and

0.025°. This makes the AD8001 ideal for professional video

electronics such as cameras and video switchers. Additionally,

the AD8001’s low distortion and fast settling make it ideal for

buffer high speed A-to-D converters.

The AD8001 offers low power of 5.5 mA max (VS = ± 5 V) and

can run on a single +12 V power supply, while being capable of

delivering over 70 mA of load current. These features make this

amplifier ideal for portable and battery-powered applications

where size and power are critical.

GENERAL DESCRIPTION

The AD8001 is a low power, high speed amplifier designed

to operate on ± 5 V supplies. The AD8001 features unique

The outstanding bandwidth of 800 MHz along with 1200 V/µs

of slew rate make the AD8001 useful in many general-purpose

high speed applications where dual power supplies of up to ± 6 V

and single supplies from 6 V to 12 V are needed. The AD8001 is

available in the industrial temperature range of –40°C to +85°C.

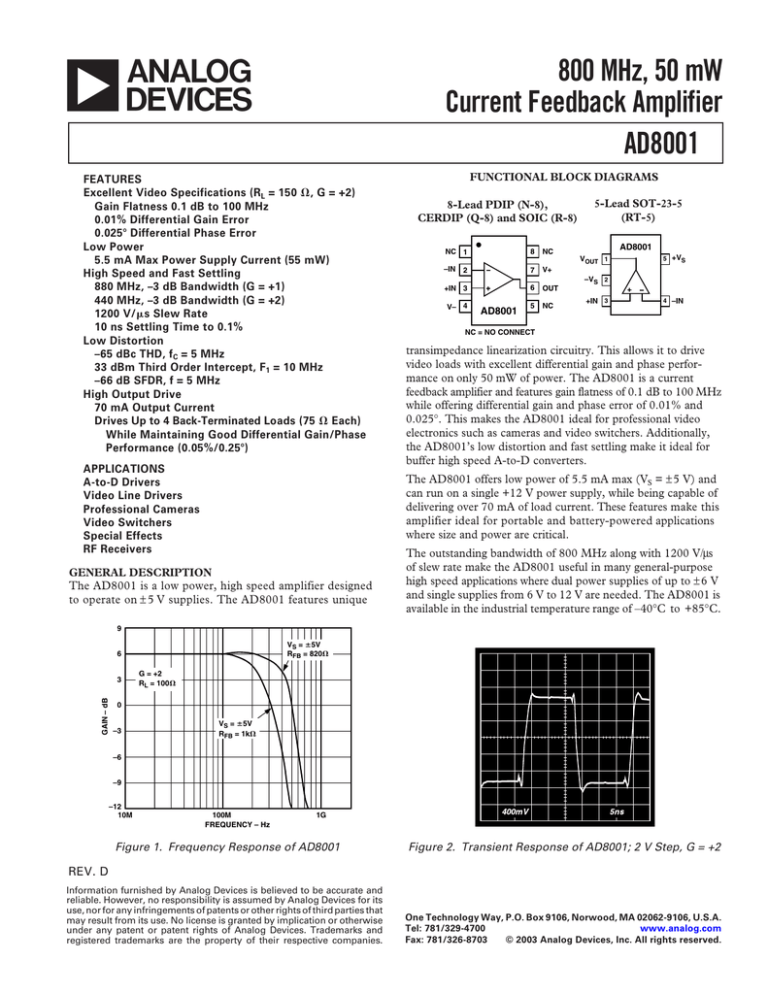

9

VS = 5V

RFB = 820

6

GAIN – dB

3

G = +2

RL = 100

0

–3

VS = 5V

RFB = 1k

–6

–9

–12

10M

100M

FREQUENCY – Hz

1G

Figure 1. Frequency Response of AD8001

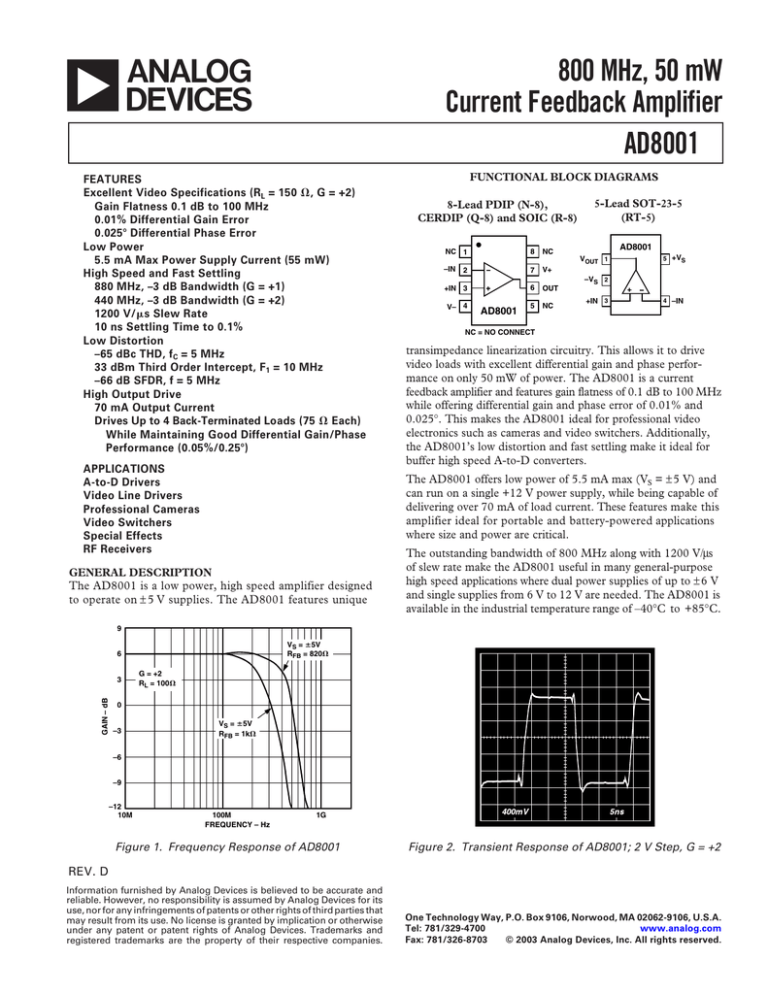

Figure 2. Transient Response of AD8001; 2 V Step, G = +2

REV. D

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.analog.com

Fax: 781/326-8703

© 2003 Analog Devices, Inc. All rights reserved.

AD8001–SPECIFICATIONS (@ T = + 25C, V = 5 V, R = 100 , unless otherwise noted.)

A

Model

DYNAMIC PERFORMANCE

–3 dB Small Signal Bandwidth,

N Package

R Package

RT Package

S

L

AD8001A

Typ

Max

Conditions

Min

Unit

G = +2, < 0.1 dB Peaking, R F = 750 Ω

G = +1, < 1 dB Peaking, RF = 1 kΩ

G = +2, < 0.1 dB Peaking, R F = 681 Ω

G = +1, < 0.1 dB Peaking, R F = 845 Ω

G = +2, < 0.1 dB Peaking, R F = 768 Ω

G = +1, < 0.1 dB Peaking, RF = 1 kΩ

350

650

350

575

300

575

440

880

440

715

380

795

MHz

MHz

MHz

MHz

MHz

MHz

G = +2, R F = 750 Ω

G = +2, R F = 681 Ω

G = +2, R F = 768 Ω

G = +2, VO = 2 V Step

G = –1, VO = 2 V Step

G = –1, VO = 2 V Step

G = +2, VO = 2 V Step, RF = 649 Ω

85

100

120

800

960

110

125

145

1000

1200

10

1.4

MHz

MHz

MHz

V/µs

V/µs

ns

ns

–65

dBc

2.0

2.0

18

0.01

0.025

33

14

–66

nV/√Hz

pA/√Hz

pA/√Hz

%

Degree

dBm

dBm

dB

Bandwidth for 0.1 dB Flatness

N Package

R Package

RT Package

Slew Rate

Settling Time to 0.1%

Rise and Fall Time

NOISE/HARMONIC PERFORMANCE

Total Harmonic Distortion

Input Voltage Noise

Input Current Noise

Differential Gain Error

Differential Phase Error

Third Order Intercept

1 dB Gain Compression

SFDR

fC = 5 MHz, VO = 2 V p-p

G = +2, RL = 100 Ω

f = 10 kHz

f = 10 kHz, +In

–In

NTSC, G = +2, R L = 150 Ω

NTSC, G = +2, R L = 150 Ω

f = 10 MHz

f = 10 MHz

f = 5 MHz

DC PERFORMANCE

Input Offset Voltage

2.0

2.0

10

5.0

TMIN –TMAX

Offset Drift

–Input Bias Current

TMIN –TMAX

+Input Bias Current

Open-Loop Transresistance

INPUT CHARACTERISTICS

Input Resistance

Input Capacitance

Input Common-Mode Voltage Range

Common-Mode Rejection Ratio

Offset Voltage

–Input Current

+Input Current

OUTPUT CHARACTERISTICS

Output Voltage Swing

Output Current

Short Circuit Current

POWER SUPPLY

Operating Range

Quiescent Current

Power Supply Rejection Ratio

–Input Current

+Input Current

3.0

TMIN –TMAX

VO = ± 2.5 V

TMIN –TMAX

250

175

+Input

–Input

+Input

0.025

0.04

5.5

9.0

25

35

6.0

10

900

10

50

1.5

3.2

VCM = ± 2.5 V

VCM = ± 2.5 V, TMIN –TMAX

VCM = ± 2.5 V, TMIN –TMAX

50

R L = 150 Ω

R L = 37.5 Ω

2.7

50

85

54

0.3

0.2

60

50

MΩ

Ω

pF

±V

1.0

0.7

5.0

75

56

0.5

0.1

dB

µA/V

µA/V

±V

mA

mA

3.1

70

110

± 3.0

TMIN –TMAX

+VS = +4 V to +6 V, –VS = –5 V

–VS = – 4 V to – 6 V, +VS = +5 V

TMIN –TMAX

TMIN –TMAX

mV

mV

µV/°C

±µA

±µA

±µA

±µA

kΩ

kΩ

± 6.0

5.5

2.5

0.5

V

mA

dB

dB

µA/V

µA/V

Specifications subject to change without notice.

–2–

REV. D

AD8001

ABSOLUTE MAXIMUM RATINGS 1

MAXIMUM POWER DISSIPATION

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12.6 V

Internal Power Dissipation @ 25°C2

PDIP Package (N) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.3 W

SOIC (R) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.8 W

8-Lead CERDIP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.1 W

SOT-23-5 Package (RT) . . . . . . . . . . . . . . . . . . . . . . . 0.5 W

Input Voltage (Common Mode) . . . . . . . . . . . . . . . . . . . . ± VS

Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . ± 1.2 V

Output Short Circuit Duration

. . . . . . . . . . . . . . . . . . . . . . Observe Power Derating Curves

Storage Temperature Range N, R . . . . . . . . . –65°C to +125°C

Operating Temperature Range (A Grade) . . . –40°C to +85°C

Lead Temperature Range (Soldering 10 sec) . . . . . . . . . 300°C

The maximum power that can be safely dissipated by the

AD8001 is limited by the associated rise in junction temperature. The maximum safe junction temperature for plastic

encapsulated devices is determined by the glass transition temperature of the plastic, approximately 150°C. Exceeding this

limit temporarily may cause a shift in parametric performance

due to a change in the stresses exerted on the die by the package.

Exceeding a junction temperature of 175°C for an extended

period can result in device failure.

2.0

MAXIMUM POWER DISSIPATION – W

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

Specification is for device in free air:

8-Lead PDIP Package: θJA = 90°C/W

8-Lead SOIC Package: θJA = 155°C/W

8-Lead CERDIP Package: θJA = 110°C/W

5-Lead SOT-23-5 Package: θJA = 260°C/W

While the AD8001 is internally short circuit protected, this

may not be sufficient to guarantee that the maximum junction

temperature (150°C) is not exceeded under all conditions. To

ensure proper operation, it is necessary to observe the maximum

power derating curves.

8-LEAD

PDIP PACKAGE

TJ = +150C

8-LEAD

CERDIP PACKAGE

1.5

8-LEAD

SOIC PACKAGE

1.0

0.5

5-LEAD

SOT-23-5 PACKAGE

0

–50 –40 –30 –20 –10 0 10 20 30 40 50 60

AMBIENT TEMPERATURE – C

70

80

90

Figure 3. Plot of Maximum Power Dissipation vs.

Temperature

ORDERING GUIDE

Model

Temperature

Range

Package

Description

Package

Option

Branding

AD8001AN

AD8001AQ

AD8001AR

AD8001AR-REEL

AD8001AR-REEL7

AD8001ART-REEL

AD8001ART-REEL7

AD8001ACHIPS

5962-9459301MPA*

–40°C to +85°C

–55°C to +125°C

–40°C to +85°C

–40°C to +85°C

–40°C to +85°C

–40°C to +85°C

–40°C to +85°C

–40°C to +85°C

–55°C to +125°C

8-Lead PDIP

8-Lead CERDIP

8-Lead SOIC

13" Tape and REEL

7" Tape and REEL

13" Tape and REEL

7" Tape and REEL

Die Form

8-Lead CERDIP

N-8

Q-8

R-8

R-8

R-8

RT-5

RT-5

HEA

HEA

*

Q-8

Standard Military Drawing Device.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD8001 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

REV. D

–3–

WARNING!

ESD SENSITIVE DEVICE

AD8001–Typical Performance Characteristics

806

0.001F

+VS

VOUT TO

TEKTRONIX

CSA 404 COMM.

SIGNAL

ANALYZER

0.1F

806

AD8001

0.1F

VIN

HP8133A

PULSE

GENERATOR

50

RL = 100

0.001F

TR/TF = 50ps

–VS

400mV

5ns

TPC 4. 2 V Step Response, G = +2

TPC 1. Test Circuit , Gain = +2

909

0.001F

+VS

0.1F

VOUT TO

TEKTRONIX

CSA 404 COMM.

SIGNAL

ANALYZER

AD8001

0.1F

VIN

LeCROY 9210

PULSE

GENERATOR

TR/TF = 350ps

TPC 2. 1 V Step Response, G = +2

0.5V

50

RL = 100

0.001F

–VS

TPC 5. Test Circuit, Gain = +1

5ns

TPC 3. 2 V Step Response, G = +1

TPC 6. 100 mV Step Response, G = +1

–4–

REV. D

AD8001

1000

9

VS = 5V

RFB = 820

G = +2

RL = 100

GAIN – dB

3

0

VS = 5V

RFB = 1k

–3

VS = 5V

RL = 100

G = +2

800

–3dB BANDWIDTH – MHz

6

–6

600

N

PACKAGE

400

R

PACKAGE

200

–9

–12

10M

100M

FREQUENCY – Hz

0

500

1G

TPC 7. Frequency Response, G = +2

0.1

0

HARMONIC DISTORTION – dBc

OUTPUT – dB

–0.5

900

1000

5V SUPPLIES

RF = 750

–0.3

–0.4

800

–50

RF = 698

–0.2

700

TPC 10. –3 dB Bandwidth vs. RF

RF =

649

–0.1

600

VALUE OF FEEDBACK RESISTOR (RF) – G = +2

RL = 100

VIN = 50mV

–0.6

–0.7

–60

VOUT = 2V p-p

RL = 100

G = +2

–70

SECOND HARMONIC

–80

THIRD HARMONIC

–90

–0.8

–0.9

1M

10M

FREQUENCY – Hz

–100

10k

100M

DIFF PHASE – Degrees

–50

5V SUPPLIES

VOUT = 2V p-p

RL = 1k

G = +2

–70

SECOND HARMONIC

10M

100M

0.08

0.06

G = +2

RF = 806

2 BACK TERMINATED

LOADS (75)

0.04

0.02

0.00

1 BACK TERMINATED

LOAD (150)

–80

0.02

–90

DIFF GAIN – %

HARMONIC DISTORTION – dBc

1M

FREQUENCY – Hz

TPC 11. Distortion vs. Frequency, RL = 100 Ω

TPC 8. 0.1 dB Flatness, R Package (for N Package Add

50 Ω to RF)

–60

100k

THIRD HARMONIC

–100

–110

10k

0.00

–0.01

–0.02

100k

1M

FREQUENCY – Hz

10M

0

100M

IRE

100

TPC 12. Differential Gain and Differential Phase

TPC 9. Distortion vs. Frequency, RL = 1 kΩ

REV. D

1 AND 2 BACK TERMINATED

LOADS (150 AND 75)

0.01

–5–

AD8001

5

1000

0

N PACKAGE

900

VIN = –26dBm

–10

GAIN – dB

–3dB BANDWIDTH – MHz

–5

RF = 909

–15

–20

–25

800

R PACKAGE

700

VIN = 50mV

RL = 100

G = +1

600

–30

–35

100M

1G

500

600

3G

FREQUENCY – Hz

TPC 13. Frequency Response, G = +1

–40

0

RF = 649

–50

–1

DISTORTION – dBc

RF = 953

–2

OUTPUT – dB

1100

TPC 16. –3 dB Bandwidth vs. RF, G = +1

1

–3

–4

–5

900

700

800

1000

VALUE OF FEEDBACK RESISTOR (RF) – G = +1

RL = 100

VIN = 50mV

–6

RL = 100

G = +1

VOUT = 2V p-p

–60

SECOND HARMONIC

–70

–80

THIRD HARMONIC

–7

–90

–8

–9

2M

10M

100M

FREQUENCY – Hz

–100

10k

1G

100M

0

G = +1

RL = 1k

VOUT = 2V p-p

–3

–60

–6

OUTPUT – dBV

DISTORTION – dBc

10M

3

–40

–70

SECOND HARMONIC

–80

THIRD HARMONIC

–90

–9

–12

–15

–18

–21

–100

–110

10k

1M

FREQUENCY – Hz

TPC 17. Distortion vs. Frequency, RL = 100 Ω

TPC 14. Flatness, R Package, G = +1 (for N Package Add

100 Ω to RF)

–50

100k

RL = 100

G = +1

–24

100k

1M

FREQUENCY – Hz

10M

–27

1M

100M

TPC 15. Distortion vs. Frequency, RL = 1 kΩ

10M

FREQUENCY – Hz

100M

TPC 18. Large Signal Frequency Response, G = +1

–6–

REV. D

AD8001

45

2.2

40

2.0

30

INPUT OFFSET VOLTAGE – mV

G = +100

35

RF = 1000

25

GAIN – dB

20

G = +10

15

RF = 470

10

5

0

–5

RL = 100

–10

–15

DEVICE NO. 1

1.8

1.6

DEVICE NO. 2

1.4

1.2

1.0

DEVICE NO. 3

0.8

0.6

–20

–25

1M

10M

100M

FREQUENCY – Hz

0.4

–60

1G

3.35

5.8

3.25

5.6

3.15

+VOUT

RL = 150

VS = 5V

3.05

| –VOUT |

2.95

2.93

2.85

+VOUT

RL = 50

VS = 5V

2.75

80

100

5.4

5.2

VS = 5V

5.0

4.8

4.6

| –VOUT |

2.65

–20

0

20

40

60

JUNCTION TEMPERATURE – C

TPC 22. Input Offset vs. Temperature

SUPPLY CURRENT – mA

OUTPUT SWING – Volts

TPC 19. Frequency Response, G = +10, G = +100

–40

2.61

2.55

–60

–40

–20

0

20

40

60

JUNCTION TEMPERATURE – C

80

4.4

–60

100

125

4

120

SHORT CIRCUIT CURRENT – mA

INPUT BIAS CURRENT – A

5

3

–IN

2

1

0

–1

+IN

–2

0

20

40

60

80

100

JUNCTION TEMPERATURE – C

120

140

SOURCE ISC

115

110

| SINK ISC |

105

100

95

90

–3

–40

–20

0

20

40

60

80

100

120

85

–60

140

JUNCTION TEMPERATURE – C

–40

–20

0

20

40

60

JUNCTION TEMPERATURE – C

80

100

TPC 24. Short Circuit Current vs. Temperature

TPC 21. Input Bias Current vs. Temperature

REV. D

–20

TPC 23. Supply Current vs. Temperature

TPC 20. Output Swing vs. Temperature

–4

–60

–40

–7–

AD8001

6

1k

100

VS = 5V

RL = 150

VOUT = 2.5V

4

ROUT – TRANSRESISTANCE – k

5

3

–TZ

2

1

0

–60

1

G = +2

RF = 909

0.1

+TZ

–40

10

–20

0

20

40

60

80

100

JUNCTION TEMPERATURE – C

120

0.01

10k

140

TPC 25. Transresistance vs. Temperature

100

100k

1M

FREQUENCY – Hz

10M

TPC 28. Output Resistance vs. Frequency

100

1

RF = 576

0

–1

10

10

NONINVERTING CURRENT VS = 5V

RF = 649

–2

OUTPUT – dB

INVERTING CURRENT VS = 5V

NOISE CURRENT – pA/√Hz

NOISE VOLTAGE – nV/√Hz

100M

–3

–4

G = –1

RL = 100

VIN = 50mV

RF = 750

–5

–6

–7

–8

VOLTAGE NOISE VS = 5V

1

10

100

1k

FREQUENCY – Hz

1

100k

10k

–9

1M

10M

100M

FREQUENCY – Hz

1G

TPC 29. –3 dB Bandwidth vs. Frequency, G = –1

TPC 26. Noise vs. Frequency

–48

–52.5

–55.0

–49

–CMRR

–PSRR

–57.5

–50

PSRR – dB

CMRR – dB

–60.0

–51

+CMRR

–52

–53

2.5V SPAN

3V SPAN

–62.5

CURVES ARE FOR WORSTCASE CONDITION WHERE

ONE SUPPLY IS VARIED

WHILE THE OTHER IS

HELD CONSTANT.

–65.0

–67.5

–70.0

–54

–72.5

+PSRR

–55

–56

–60

–75.0

–40

–20

0

20

40

60

80

100

JUNCTION TEMPERATURE – C

120

–77.5

–60

140

TPC 27. CMRR vs. Temperature

–40

–20

0

20

40

60

JUNCTION TEMPERATURE – C

80

100

TPC 30. PSRR vs. Temperature

–8–

REV. D

AD8001

30

–10

10

51

150

–20

VOUT

62

0

150

PSRR – dB

CMRR – dB

910

CURVES ARE FOR WORSTCASE CONDITION WHERE

ONE SUPPLY IS VARIED

WHILE THE OTHER IS

HELD CONSTANT.

20

910

VIN

–30

–10

–PSRR

–20

–30

–40

+PSRR

–PSRR

+PSRR

–40

RF = 909

G = +2

–50

–50

–60

300k

1M

10M

FREQUENCY – Hz

100M

1M

1G

TPC 31. CMRR vs. Frequency

1G

10M

100M

FREQUENCY – Hz

TPC 34. PSRR vs. Frequency

1

RF = 549

0

–1

RF = 649

OUTPUT – dB

–2

–3

G = –2

RL = 100

VIN = 50mVrms

–4

–5

RF = 750

–6

–7

–8

10M

100M

FREQUENCY – Hz

1G

TPC 35. 2 V Step Response, G = –1

TPC 32. –3 dB Bandwidth vs. Frequency, G = –2

100

100

3 WAFER LOTS

COUNT = 895

MEAN = 1.37

STD DEV = 1.13

MIN = –2.45

MAX = +4.69

90

80

70

90

80

CUMULATIVE

70

COUNT

60

50

FREQ DIST

40

40

30

30

20

20

10

10

0

–5

–4

–3

–2

–1

0

1

2

3

INPUT OFFSET VOLTAGE – mV

4

5

TPC 36. Input Offset Voltage Distribution

TPC 33. 100 mV Step Response, G = –1

REV. D

60

50

–9–

0

PERCENT

–9

1M

AD8001

THEORY OF OPERATION

A very simple analysis can put the operation of the AD8001, a

current feedback amplifier, in familiar terms. Being a current

feedback amplifier, the AD8001’s open-loop behavior is expressed

as transimpedance, ∆VO/∆I–IN, or TZ. The open-loop transimpedance behaves just as the open-loop voltage gain of a voltage

feedback amplifier, that is, it has a large dc value and decreases

at roughly 6 dB/octave in frequency.

Since the RIN is proportional to 1/gM, the equivalent voltage

gain is just TZ × gM, where the gM in question is the transconductance of the input stage. This results in a low open-loop

input impedance at the inverting input, a now familiar result.

Using this amplifier as a follower with gain, Figure 4, basic

analysis yields the following result.

Considering that additional poles contribute excess phase at

high frequencies, there is a minimum feedback resistance below

which peaking or oscillation may result. This fact is used to

determine the optimum feedback resistance, R F. In practice,

parasitic capacitance at Pin 2 will also add phase in the feedback

loop, so picking an optimum value for R F can be difficult.

Figure 6 illustrates this problem. Here the fine scale (0.1 dB/

div) flatness is plotted versus feedback resistance. These plots

were taken using an evaluation card which is available to customers so that these results may readily be duplicated.

Achieving and maintaining gain flatness of better than 0.1 dB at

frequencies above 10 MHz requires careful consideration of

several issues.

0.1

TZ (S )

VO

=G×

VIN

TZ (S ) + G × RIN + R1

R1

R2

RF = 698

–0.1

RIN = 1 / g M ≈ 50 Ω

–0.2

OUTPUT – dB

G = 1+

RF =

649

0

R1

G = +2

–0.3

RF = 750

–0.4

–0.5

R2

–0.6

RIN

–0.7

VOUT

–0.8

VIN

–0.9

1M

10M

FREQUENCY – Hz

100M

Figure 6. 0.1 dB Flatness vs. Frequency

Figure 4. Follower with Gain

Recognizing that G × RIN << R1 for low gains, it can be seen to

the first order that bandwidth for this amplifier is independent

of gain (G). This simple analysis in conjunction with Figure 5

can, in fact, predict the behavior of the AD8001 over a wide

range of conditions.

1M

100k

Choice of Feedback and Gain Resistors

Because of the above-mentioned relationship between the bandwidth and feedback resistor, the fine scale gain flatness will, to

some extent, vary with feedback resistance. It, therefore, is

recommended that once optimum resistor values have been

determined, 1% tolerance values should be used if it is desired to

maintain flatness over a wide range of production lots. In addition,

resistors of different construction have different associated parasitic

capacitance and inductance. Surface-mount resistors were used

for the bulk of the characterization for this data sheet. It is not

recommended that leaded components be used with the AD8001.

TZ – 10k

1k

100

10

100k

1M

10M

FREQUENCY – Hz

100M

1G

Figure 5. Transimpedance vs. Frequency

–10–

REV. D

AD8001

Printed Circuit Board Layout Considerations

Driving Capacitive Loads

As to be expected for a wideband amplifier, PC board parasitics

can affect the overall closed-loop performance. Of concern are

stray capacitances at the output and the inverting input nodes. If

a ground plane is to be used on the same side of the board as

the signal traces, a space (5 mm min) should be left around the

signal lines to minimize coupling. Additionally, signal lines

connecting the feedback and gain resistors should be short

enough so that their associated inductance does not cause high

frequency gain errors. Line lengths on the order of less than

5 mm are recommended. If long runs of coaxial cable are being

driven, dispersion and loss must be considered.

The AD8001 was designed primarily to drive nonreactive loads.

If driving loads with a capacitive component is desired, best

frequency response is obtained by the addition of a small series

resistance, as shown in Figure 8. The accompanying graph

shows the optimum value for RSERIES versus capacitive load. It is

worth noting that the frequency response of the circuit when

driving large capacitive loads will be dominated by the passive

roll-off of RSERIES and CL.

909

Power Supply Bypassing

RSERIES

Adequate power supply bypassing can be critical when optimizing the performance of a high frequency circuit. Inductance in

the power supply leads can form resonant circuits that produce

peaking in the amplifier’s response. In addition, if large current

transients must be delivered to the load, then bypass capacitors

(typically greater than 1 µF) will be required to provide the best

settling time and lowest distortion. A parallel combination of

4.7 µF and 0.1 µF is recommended. Some brands of electrolytic

capacitors will require a small series damping resistor ≈4.7 Ω for

optimum results.

IN

RL

500

CL

Figure 8. Driving Capacitive Loads

40

G = +1

DC Errors and Noise

R

R

VOUT = VIO × 1 + F ± I BN × RN × 1 + F ± I BI × RF

RI

RI

RF

RI

RN

IBI

IBN

VOUT

Figure 7. Output Offset Voltage

REV. D

–11–

30

RSERIES – There are three major noise and offset terms to consider in a

current feedback amplifier. For offset errors, refer to the equation

below. For noise error the terms are root-sum-squared to give a

net output error. In the circuit in Figure 7 they are input offset

(VIO), which appears at the output multiplied by the noise gain

of the circuit (1 + RF/RI), noninverting input current (IBN × RN)

also multiplied by the noise gain, and the inverting input current,

which when divided between RF and RI and subsequently

multiplied by the noise gain always appears at the output as

IBN × RF. The input voltage noise of the AD8001 is a low 2 nV/

√Hz. At low gains though the inverting input current noise times

RF is the dominant noise source. Careful layout and device

matching contribute to better offset and drift specifications for

the AD8001 compared to many other current feedback amplifiers. The typical performance curves in conjunction with the

following equations can be used to predict the performance of

the AD8001 in any application.

20

10

0

0

5

10

15

20

25

CL – pF

Figure 9. Recommended RSERIES vs. Capacitive Load

AD8001

Communications

Operation as a Video Line Driver

Distortion is a key specification in communications applications.

Intermodulation distortion (IMD) is a measure of the ability of

an amplifier to pass complex signals without the generation of

spurious harmonics. The third order products are usually the

most problematic since several of them fall near the fundamentals

and do not lend themselves to filtering. Theory predicts that the

third order harmonic distortion components increase in power at

three times the rate of the fundamental tones. The specification

of third order intercept as the virtual point where fundamental and

harmonic power are equal is one standard measure of distortion

performance. Op amps used in closed-loop applications do not

always obey this simple theory. At a gain of +2, the AD8001

has performance summarized in Figure 10. Here the worst third

order products are plotted versus input power. The third order

intercept of the AD8001 is +33 dBm at 10 MHz.

The AD8001 has been designed to offer outstanding performance as a video line driver. The important specifications of

differential gain (0.01%) and differential phase (0.025°) meet

the most exacting HDTV demands for driving one video load.

The AD8001 also drives up to two back terminated loads as

shown in Figure 11, with equally impressive performance (0.01%,

0.07°). Another important consideration is isolation between

loads in a multiple load application. The AD8001 has more

than 40 dB of isolation at 5 MHz when driving two 75 Ω back

terminated loads.

909

75

75 CABLE

909

+VS

VOUT NO. 1

75

0.001F

+

0.1F

–45

THIRD ORDER IMD – dBc

–50

G = +2

F1 = 10MHz

75

CABLE

F2 = 12MHz

AD8001

VIN

2F2 – F1

–55

75

75 CABLE

0.1F

VOUT NO. 2

75

75

–60

0.001F

2F1 – F2

–65

–VS

Figure 11. Video Line Driver

–70

–75

–80

–8 –7

–6

–5

–4

–3 –2 –1 0

1

INPUT POWER – dBm

2

3

4

5

6

Figure 10. Third Order IMD; F1 = 10 MHz, F2 = 12 MHz

–12–

REV. D

AD8001

ADC. Using the AD9058’s internal +2 V reference connected

to both ADCs as shown in Figure 12 reduces the number of

external components required to create a complete data

acquisition system. The 20 Ω resistors in series with ADC inputs

are used to help the AD8001s drive the 10 pF ADC input

capacitance. The AD8001 only adds 100 mW to the power

consumption while not limiting the performance of the circuit.

Driving A-to-D Converters

The AD8001 is well suited for driving high speed analog-todigital converters such as the AD9058. The AD9058 is a dual

8-bit 50 MSPS ADC. In the circuit below, the AD8001 is

shown driving the inputs of the AD9058, which are configured

for 0 V to 2 V ranges. Bipolar input signals are buffered, amplified

(–2×), and offset (by +1.0 V) into the proper input range of the

1k

ENCODE

74ACT04

10

ENCODE A

8

649

38

ANALOG

IN A

0.5V

324

10pF

50

36

ENCODE B

–VREF A

+VS

–VREF B

5, 9, 22,

24, 37, 41

AD9058

20

AD8001

6

RZ1

(J-LEAD)

AIN A

1.3k

+5V

0.1F

D0A (LSB)

18

17

AD707

0.1F

20k

20k

3

0.1F

43

15

+VINT

14

+VREF A

13

+VREF B

12

D7A (MSB)

1.3k

649

D0B (LSB)

324

28

RZ2

29

30

20

AD8001

40

31

AIN B

32

33

1

D7B (MSB)

–VS

RZ1, RZ2 = 2,000 SIP (8-PKG)

35

7, 20,

26, 39

0.1F

4,19, 21

25, 27, 42

Figure 12. AD8001 Driving a Dual A-to-D Converter

REV. D

–13–

8

34

COMP

0.1F

8

11

74ACT 273

ANALOG

IN B

0.5V

74ACT 273

16

2

–2V

–5V

1N4001

CLOCK

AD8001

(4.7 µF–10 µF) tantalum electrolytic capacitor should be connected in parallel, but not necessarily so close, to supply current

for fast, large-signal changes at the output.

Layout Considerations

The specified high speed performance of the AD8001 requires

careful attention to board layout and component selection. Proper

RF design techniques and low parasitic component selection

are mandatory.

The feedback resistor should be located close to the inverting

input pin in order to keep the stray capacitance at this node to a

minimum. Capacitance variations of less than 1 pF at the inverting input will significantly affect high speed performance.

The PCB should have a ground plane covering all unused portions

of the component side of the board to provide a low impedance

ground path. The ground plane should be removed from the area

near the input pins to reduce stray capacitance.

Stripline design techniques should be used for long signal traces

(greater than about 1 inch). These should be designed with a

characteristic impedance of 50 Ω or 75 Ω and be properly terminated at each end.

Chip capacitors should be used for supply bypassing (see Figure 13).

One end should be connected to the ground plane and the other

within 1/8 inch of each power pin. An additional large

RF

RF

+VS

+VS

+VS

C1

0.1F

RG

IN

RO

RT

RG

C3

10F

RO

OUT

OUT

C2

0.1F

RS

–VS

IN

C4

10F

RT

–VS

Inverting Configuration

Supply Bypassing

–VS

Noninverting Configuration

Figure 13. Inverting and Noninverting Configurations for Evaluation Boards

Table I. Recommended Component Values

AD8001AN (PDIP)

Gain

AD8001AR (SOIC)

Gain

AD8001ART (SOT-23-5)

Gain

Component

–1

+1

+2

+10

+100

–1

+1

+2

+10

+100

–1

+1

RF (Ω)

RG (Ω)

RO (Nominal) (Ω)

RS (Ω)

RT (Nominal) (Ω)

Small Signal

BW (MHz)

0.1 dB Flatness

(MHz)

649

649

49.9

0

54.9

340

1050

470

51

49.9

1000

10

49.9

49.9

681

681

49.9

470

51

49.9

1000

10

49.9

49.9

880

49.9

460

49.9

260

49.9

20

604

604

49.9

0

54.9

370

953

49.9

750

750

49.9

49.9

710

49.9

440

49.9

260

49.9

20

845

845

49.9

0

54.9

240

70

105

130

100

120

110

105

–14–

+2

+10

+100

1000 768

768

49.9 49.9

470

51

49.9

1000

10

49.9

49.9

795

49.9

380

49.9

260

49.9

20

300

145

REV. D

AD8001

OUTLINE DIMENSIONS

8-Lead Plastic Dual In-Line Package [PDIP]

(N-8)

8-Lead Ceramic Dual In-Line Package [CERDIP]

(Q-8)

Dimensions shown in inches and (millimeters)

Dimensions shown in inches and (millimeters)

0.375 (9.53)

0.365 (9.27)

0.355 (9.02)

0.005 (0.13)

MIN

0.055 (1.40)

MAX

8

8

5

0.295 (7.49)

0.285 (7.24)

0.275 (6.98)

4

1

1

0.100 (2.54)

BSC

0.015

(0.38)

MIN

0.150 (3.81)

0.130 (3.30)

0.110 (2.79)

0.022 (0.56)

0.018 (0.46)

0.014 (0.36)

0.310 (7.87)

0.220 (5.59)

PIN 1

0.325 (8.26)

0.310 (7.87)

0.300 (7.62)

0.180

(4.57)

MAX

5

0.100 (2.54) BSC

0.150 (3.81)

0.135 (3.43)

0.120 (3.05)

0.320 (8.13)

0.290 (7.37)

0.405 (10.29) MAX

0.060 (1.52)

0.015 (0.38)

0.200 (5.08)

MAX

0.150 (3.81)

MIN

0.200 (5.08)

0.125 (3.18)

0.015 (0.38)

0.010 (0.25)

0.008 (0.20)

SEATING

PLANE

0.060 (1.52)

0.050 (1.27)

0.045 (1.14)

4

SEATING

0.070 (1.78) PLANE

0.030 (0.76)

0.023 (0.58)

0.014 (0.36)

0.015 (0.38)

0.008 (0.20)

15

0

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETERS DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

COMPLIANT TO JEDEC STANDARDS MO-095AA

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

8-Lead Standard Small Outline Package [SOIC]

(R-8)

5-Lead Small Outline Transistor Package [SOT-23]

(RT-5)

Dimensions shown in millimeters and (inches)

Dimensions shown in millimeters

5.00 (0.1968)

4.80 (0.1890)

4.00 (0.1574)

3.80 (0.1497)

8

5

1

4

2.90 BSC

5

6.20 (0.2440)

5.80 (0.2284)

2.80 BSC

1.60 BSC

1

1.27 (0.0500)

BSC

0.25 (0.0098)

0.10 (0.0040)

COPLANARITY

SEATING

0.10

PLANE

1.75 (0.0688)

1.35 (0.0532)

0.51 (0.0201)

0.31 (0.0122)

4

0.50 (0.0196)

ⴛ 45ⴗ

0.25 (0.0099)

2

3

PIN 1

0.95 BSC

1.30

1.15

0.90

8ⴗ

0.25 (0.0098) 0ⴗ 1.27 (0.0500)

0.40 (0.0157)

0.17 (0.0067)

1.90

BSC

1.45 MAX

COMPLIANT TO JEDEC STANDARDS MS-012AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

0.15 MAX

0.50

0.30

SEATING

PLANE

0.22

0.08

10ⴗ

5ⴗ

0ⴗ

COMPLIANT TO JEDEC STANDARDS MO-178AA

REV. D

–15–

0.60

0.45

0.30

AD8001

Location

Page

7/03—Data Sheet changed from REV. C to REV. D

Renumbered figures and TPCs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Universal

Changes to ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Updated OUTLINE DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

–16–

REV. D

C01043–0–7/03(D)

Revision History

CD4051BMS, CD4052BMS

CD4053BMS

CMOS Analog

Multiplexers/Demultiplexers*

December 1992

Features

Description

• Logic Level Conversion

CD4051BMS, CD4052BMS and CD4053BMS analog multiplexers/demultiplexers are digitally controlled analog

switches having low ON impedance and very low OFF leakage current. Control of analog signals up to 20V peak-topeak can be achieved by digital signal amplitudes of 4.5V to

20V (if VDD-VSS = 3V, a VDD-VEE of up to 13V can be controlled; for VDD-VEE level differences above 13V, a VDDVSS of at least 4.5V is required). For example, if VDD =

+4.5V, VSS = 0, and VEE = -13.5V, analog signals from 13.5V to +4.5V can be controlled by digital inputs of 0 to 5V.

These multiplexer circuits dissipate extremely low quiescent

power over the full VDD-VSS and VDD-VEE supply voltage

ranges, independent of the logic state of the control signals.

When a logic “1” is present at the inhibit input terminal all

channels are off.

• High-Voltage Types (20V Rating)

• CD4051BMS Signal 8-Channel

• CD4052BMS Differential 4-Channel

• CD4053BMS Triple 2-Channel

• Wide Range of Digital and Analog Signal Levels:

- Digital 3V to 20V

- Analog to 20Vp-p

• Low ON Resistance: 125Ω (typ) Over 15Vp-p Signal

Input Range for VDD - VEE = 15V

• High OFF Resistance: Channel Leakage of ±100pA

(typ) at VDD - VEE = 18V

• Logic Level Conversion:

- Digital Addressing Signals of 3V to 20V (VDD - VSS

= 3V to 20V)

- Switch Analog Signals to 20Vp-p (VDD - VEE = 20V);

See Introductory Text

• Matched Switch Characteristics: RON = 5Ω (typ) for

VDD - VEE = 15V

• Very Low Quiescent Power Dissipation Under All Digital Control Input and Supply Conditions: 0.2µW (typ)

at VDD - VSS = VDD - VEE = 10V

• Binary Address Decoding on Chip

• 5V, 10V and 15V Parametric Ratings

The CD4051BMS is a single 8 channel multiplexer having

three binary control inputs, A, B, and C, and an inhibit input.

The three binary signals select 1 of 8 channels to be turned

on, and connect one of the 8 inputs to the output.

The CD4052BMS is a differential 4 channel multiplexer having two binary control inputs, A and B, and an inhibit input.

The two binary input signals select 1 of 4 pairs of channels

to be turned on and connect the analog inputs to the outputs.

The CD4053BMS is a triple 2 channel multiplexer having

three separate digital control inputs, A, B, and C, and an

inhibit input. Each control input selects one of a pair of channels which are connected in a single pole double-throw configuration.

The CD4051BMS, CD4052BMS and CD4053BMS are supplied

in these 16 lead outline packages:

• 100% Tested for Quiescent Current at 20V

• Maximum Input Current of 1µA at 18V Over Full Package Temperature Range; 100nA at 18V and +25oC

Braze Seal DIP

*H4X

• Break-Before-Making Switching Eliminates Channel

Overlap

Frit Seal DIP

H1E

Ceramic Flatpack

H6W

Applications

*CD4051B Only

†H4T

†CD4052B, CD4053 Only

• Analog and Digital Multiplexing and Demultiplexing

• A/D and D/A Conversion

• Signal Gating

* When these devices are used as demultiplexers the “CHANNEL

IN/OUT” terminals are the outputs and the “COMMON OUT/IN” terminals are the inputs.

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

7-937

File Number

3316

CD4051BMS, CD4052BMS, CD4053BMS

Pinouts

CD4051BM

TOP VIEW

CHANNELS

IN/OUT

CD4052BMS

TOP VIEW

4

1

16 VDD

6

2

15 2

COM OUT/IN 3

14 1

7

4

13 0

5

5

12 3

INH 6

CHANNELS

IN/OUT

0

1

16 VDD

2

2

15 2

COMMON “Y” OUT/IN 3

14 1

Y CHANNELS

IN/OUT

CHANNELS

IN/OUT

X CHANNELS

IN/OUT

3

4

13 COMMON “X” OUT/IN

1

5

12 0

11 A

INH 6

11 3

VEE 7

10 B

VEE 7

10 A

VSS 8

9 C

VSS 8

9 B

Y CHANNELS

IN/OUT

X CHANNELS

IN/OUT

CD4053BMS

TOP VIEW

IN/OUT

by

1

16 VDD

bx

2

15 OUT/IN bx or by

cy

3

14 OUT/IN ax or ay

OUT/IN CX or CY

4

13 ay

IN/OUT CX

5

12 ax

IN/OUT

INH 6

11 A

VEE 7

10 B

VSS 8

9 C

Functional Diagrams

CHANNEL IN/OUT

16

VDD

7

6

5

4

3

2

1

0

4

2

5

1

12

15

14

13

TG

TG

*

A

11

TG

*

B

10

LOGIC

LEVEL

CONVERSION

BINARY

TO

1 OF 8

DECODER

WITH

INHIBIT

*

C

9

INH

6

TG

3

TG

COMMON

OUT/IN

TG

TG

*

TG

VDD

8

VSS

7

* ALL INPUTS PROTECTED BY

STANDARD CMOS PROTECTION

NETWORK

VEE

VSS

CD4051BMS

7-938

CD4051BMS, CD4052BMS, CD4053BMS

Functional Diagrams

(Continued)

X CHANNELS IN/OUT

3

2

1

0

11

15

14

12

TG

16

VDD

TG

TG

*

A

TG

10

LOGIC

LEVEL

CONVERSION

BINARY

TO

1 OF 4

DECODER

WITH

INHIBIT

*

B

9

INH

6

COMMON X

OUT/IN

13

TG

3

COMMON Y

OUT/IN

TG

TG

*

TG

8

VSS

7

1

5

2

4

0

1

2

3

Y CHANNELS IN/OUT

VEE

CD4052BMS

VDD

* ALL INPUTS PROTECTED BY

STANDARD CMOS PROTECTION

NETWORK

VSS

BINARY TO 1 OF 2

DECODERS WITH

INHIBIT

LOGIC

LEVEL

CONVERSION

16

VDD

IN/OUT

cy

cx

by

bx

ay

ax

3

5

1

2

13

12

TG

14

*

A

B

OUT/IN

ax or ay

11

TG

*

TG

OUT/IN

bx or by

15

10

TG

*

C

TG

9

OUT/IN

cx or cy

4

*

INH

TG

6

8

VSS

7

VEE

CD4053BMS

7-939

Specifications CD4051BMS, CD4052BMS, CD4053BMS

Absolute Maximum Ratings

Reliability Information

DC Supply Voltage Range, (VDD) . . . . . . . . . . . . . . . -0.5V to +20V

(Voltage Referenced to VSS Terminals)

Input Voltage Range, All Inputs . . . . . . . . . . . . .-0.5V to VDD +0.5V

DC Input Current, Any One Input . . . . . . . . . . . . . . . . . . . . . . . .±10mA

Operating Temperature Range . . . . . . . . . . . . . . . . -55oC to +125oC

Package Types D, F, K, H

Storage Temperature Range (TSTG) . . . . . . . . . . . -65oC to +150oC

Lead Temperature (During Soldering) . . . . . . . . . . . . . . . . . +265oC

At Distance 1/16 ± 1/32 Inch (1.59mm ± 0.79mm) from case for

10s Maximum

Thermal Resistance . . . . . . . . . . . . . . . .

θja

θjc

Ceramic DIP and FRIT Package . . . . . 80oC/W

20oC/W

Flatpack Package . . . . . . . . . . . . . . . . 70oC/W

20oC/W

o

Maximum Package Power Dissipation (PD) at +125 C

For TA = -55oC to +100oC (Package Type D, F, K) . . . . . . 500mW

For TA = +100oC to +125oC (Package Type D, F, K) . . . . . Derate

Linearity at 12mW/oC to 200mW

Device Dissipation per Output Transistor . . . . . . . . . . . . . . . 100mW

For TA = Full Package Temperature Range (All Package Types)

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +175oC

TABLE 1. DC ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER

Supply Current

Input Leakage Current

Input Leakage Current

SYMBOL

IDD

IIL

IIH

CONDITIONS (NOTE 1)

VDD = 20V, VIN = VDD or GND

RON

TEMPERATURE

MIN

MAX

UNITS

1

+25oC

-

10

µA

2

+125 C

-

1000

µA

VDD = 18V, VIN = VDD or GND

3

-55oC

-

10

µA

VIN = VDD or GND

1

+25oC

-100

-

nA

2

+125oC

-1000

-

nA

VDD = 18V

3

-55oC

-100

-

nA

VDD = 20

1

+25oC

-

100

nA

2

+125oC

-

1000

nA

3

-55oC

-

100

nA

1

+25oC

-

1050

Ω

2

+125oC

-

1300

Ω

3

-55oC

-

800

Ω

1

+25oC

-

400

Ω

2

+125oC

-

550

Ω

3

-55oC

-

310

Ω

1

+25oC

-

240

Ω

2

+125oC

-

320

Ω

Ω

VIN = VDD or GND

VDD = 20

VDD = 18V

On-State Resistance

RL = 10K Returned to

VDD - VSS/2

LIMITS

GROUP A

SUBGROUPS

VDD = 5V

VIS = VSS to VDD

VDD = 10V

VIS = VSS to VDD

VDD = 15V

VIS = VSS to VDD

o

3

-55oC

-

220

N Threshold Voltage

VNTH

VDD = 10V, ISS = -10µA

1

+25oC

-2.8

-0.7

V

P Threshold Voltage

VPTH

VSS = 0V, IDD = 10µA

1

+25oC

0.7

2.8

V

VDD = 2.8V, VIN = VDD or GND

7

+25oC

VDD = 20V, VIN = VDD or GND

7

+25oC

VDD = 18V, VIN = VDD or GND

8A

+125oC

VDD = 3V, VIN = VDD or GND

8B

-55oC

VDD = 5V = VIS thru 1k,

VEE = VSS

RL = 1k to VSS, |IIS| < 2µA

OFF Channels

1, 2, 3

+25oC, +125oC, -55oC

-

1.5

V

1, 2, 3

+25oC, +125oC, -55oC

3.5

-

V

VDD = 15V = VIS thru 1K

VEE = VSS

RL = 1K to VSS, |ISS|, <2µA

On All OFF Channels

1, 2, 3

+25oC, +125oC, -55oC

-

4

V

1, 2, 3

+25oC, +125oC, -55oC

11

-

V

1

+25oC

-0.1

-

µA

Functional

(Note 4)

F

Input Voltage Low

(Note 2)

VIL

Input Voltage High

(Note 2)

VIH

Input Voltage Low

(Note 2)

VIL

Input Voltage High

(Note 2)

VIH

Off Channel Leakage

Any Channel OFF

Or

All Channels Off

(Common Out/In)

IOZL

IOZH

VIN = VDD or GND

VOUT = 0V

VIN = VDD or GND

VOUT = VDD

VDD = 20V

VOH > VOL <

VDD/2 VDD/2

V

2

+125oC

-1.0

-

µA

VDD = 18V

3

-55oC

-0.1

-

µA

VDD = 20V

1

+25oC

-

0.1

µA

2

+125oC

-

1.0

µA

3

-55oC

-

0.1

µA

VDD = 18V

NOTES: 1. All voltages referenced to device GND, 100% testing being

implemented.

2. Go/No Go test with limits applied to inputs.

7-940

3. For accuracy, voltage is measured differentially to VDD. Limit

is 0.050V max.

4. VDD = 2.8V/3.0V, RL = 200k to VDD

VDD = 20V/18V, RL = 10k to VDD

Specifications CD4051BMS, CD4052BMS, CD4053BMS

TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER

SYMBOL

CONDITIONS (Notes 1, 2)

Propagation Delay

(Note 1)

Address to Signal Out

Channels On or Off

TPHL

TPLH

VDD = 5V, VIN = VDD or GND

VEE = VSS = 0V

Propagation Delay

(Note 1)

Inhibit to Signal Out

(Channel Turning On)

TPZH

TPZL

VDD = 5V, VIN = VDD or GND

VEE = VSS = 0V

Propagation Delay

(Note 1)

Inhibit to Signal Out

(Channel Turning Off)

TPHZ

TPLZ

VDD = 5V, VIN = VDD or GND

VEE = VSS = 0V

GROUP A

SUBGROUPS TEMPERATURE

9

10, 11

+25oC

+125oC,

-55oC

LIMITS

MIN

MAX

UNITS

-

720

ns

-

972

ns

9

+25oC

-

720

ns

10, 11

+125oC, -55oC

-

972

ns

9

+25oC

-

450

ns

-

608

ns

10, 11

+125oC,

-55oC

NOTES:

1. -55oC and +125oC limits guaranteed, 100% testing being implemented.

2. CL = 50pF, RL = 10KΩ, Input TR, TF < 20ns.

TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS

LIMITS

PARAMETER

Supply Current

SYMBOL

CONDITIONS

NOTES

TEMPERATURE

MIN

MAX

UNITS

IDD

VDD = 5V, VIN = VDD or GND

1, 2

-55oC, +25oC

-

5

µA

+125oC

-

150

µA

VDD = 10V, VIN = VDD or GND

VDD = 15V, VIN = VDD or GND

Input Voltage Low

Input Voltage High

Propagation Delay

Address to Signal Out

(Channels On or Off)

VIL

VIH

TPHL

TPLH

VDD = VIS = 10V, VEE = VSS

RL = 1K to VSS

|IIS|, 2µA On/Off Channel

Propagation Delay

Inhibit to Signal Out

(Channel Turning Off)

TPZH

TPZL

TPHZ

TPLZ

CIN

1, 2

-

10

µA

+125oC

-

300

µA

-

10

µA

+125oC

-

600

µA

+25oC, +125oC,

-

3

V

-55oC,

+25oC

-55oC

+25oC, +125oC,

-55oC

+7

-

V

1, 2, 3

+25oC

-

320

ns

1, 2, 3

+25oC

-

240

ns

1, 2, 3

+25

oC

-

450

ns

1, 2, 3

+25oC

-

320

ns

VDD = 15V

1, 2, 3

+25oC

-

240

ns

VDD = 5V

VEE = -10V

1, 2, 3

+25oC

-

400

ns

1, 2, 3

+25oC

-

210

ns

1, 2, 3

+25oC

-

160

ns

1, 2, 3

+25oC

-

300

ns

1, 2

+25oC

-

7.5

pF

VDD = 10V

VEE = VSS = 0V

VDD = 15V

VDD = 10V

VDD = 10V

VEE = VSS = 0V

VEE = VSS = 0V

VDD = 15V

VDD = 5V

VEE = -15V

Input Capacitance

1, 2

-55 C, +25 C

o

1, 2

VDD = 5V

VEE = -5V

Propagation Delay

Inhibit to Signal Out

(Channel Turning On)

1, 2

o

Any Address or Inhibit Input

NOTES:

1. All voltages referenced to device GND.

2. The parameters listed on Table 3 are controlled via design or process and are not directly tested. These parameters are characterized on initial design release and upon design changes which would affect these characteristics.

3. CL = 50pF, RL = 10K, Input TR, TF < 20ns.

7-941

Specifications CD4051BMS, CD4052BMS, CD4053BMS

TABLE 4. POST IRRADIATION ELECTRICAL PERFORMANCE CHARACTERISTICS

LIMITS

PARAMETER

SYMBOL

CONDITIONS

NOTES

TEMPERATURE

MIN

MAX

UNITS

IDD

VDD = 20V, VIN = VDD or GND

1, 4

+25oC

-

25

µA

1, 4

+25oC

-2.8

-0.2

V

VDD = 10V, ISS = -10µA

1, 4

+25oC

-

±1

V

VSS = 0V, IDD = 10µA

1, 4

+25oC

0.2

2.8

V

1, 4

+25oC

-

±1

V

1

+25oC

VOH >

VDD/2

VOL <

VDD/2

V

1, 2, 3, 4

+25oC

-

1.35 x

+25oC

Limit

ns

Supply Current

N Threshold Voltage

VNTH

N Threshold Voltage

Delta

∆VTN

P Threshold Voltage

VTP

P Threshold Voltage

Delta

∆VTP

Functional

F

VDD = 10V, ISS = -10µA

VSS = 0V, IDD = 10µA

VDD = 18V, VIN = VDD or GND

VDD = 3V, VIN = VDD or GND

Propagation Delay Time

TPHL

TPLH

VDD = 5V

3. See Table 2 for +25oC limit.

NOTES: 1. All voltages referenced to device GND.

2. CL = 50pF, RL = 200K, Input TR, TF < 20ns.

4. Read and Record

TABLE 5. BURN-IN AND LIFE TEST DELTA PARAMETERS +25OC

PARAMETER

Supply Current - MSI-2

ON Resistance

SYMBOL

DELTA LIMIT

± 1.0µA

IDD

RONDEL10

± 20% x Pre-Test Reading

TABLE 6. APPLICABLE SUBGROUPS

MIL-STD-883

METHOD

GROUP A SUBGROUPS

Initial Test (Pre Burn-In)

100% 5004

1, 7, 9

IDD, IOL5, IOH5A, RONDEL10

Interim Test 1 (Post Burn-In)

100% 5004

1, 7, 9

IDD, IOL5, IOH5A, RONDEL10

Interim Test 2 (Post Burn-In)

100% 5004

1, 7, 9

IDD, IOL5, IOH5A, RONDEL10

100% 5004

1, 7, 9, Deltas

100% 5004

1, 7, 9

CONFORMANCE GROUP

PDA (Note 1)

Interim Test 3 (Post Burn-In)

PDA (Note 1)

Final Test

Group A

Group B

Subgroup B-5

Subgroup B-6

Group D

READ AND RECORD

IDD, IOL5, IOH5A, RONDEL10

100% 5004

1, 7, 9, Deltas

100% 5004

2, 3, 8A, 8B, 10, 11

Sample 5005

1, 2, 3, 7, 8A, 8B, 9, 10, 11

Sample 5005

1, 2, 3, 7, 8A, 8B, 9, 10, 11, Deltas

Sample 5005

1, 7, 9

Sample 5005

1, 2, 3, 8A, 8B, 9

Subgroups 1, 2, 3, 9, 10, 11

Subgroups 1, 2 3

NOTE: 1. 5% Parameteric, 3% Functional; Cumulative for Static 1 and 2.

TABLE 7. TOTAL DOSE IRRADIATION

CONFORMANCE GROUPS

Group E Subgroup 2

TEST

READ AND RECORD

MIL-STD-883

METHOD

PRE-IRRAD

POST-IRRAD

PRE-IRRAD

POST-IRRAD

5005

1, 7, 9

Table 4

1, 9

Table 4

TABLE 8. BURN-IN AND IRRADIATION TEST CONNECTIONS

OSCILLATOR

FUNCTION

OPEN

GROUND

VDD

PART NUMBER CD4051BMS

7-942

9V ± -0.5V

50kHz

25kHz

Specifications CD4051BMS, CD4052BMS, CD4053BMS

TABLE 8. BURN-IN AND IRRADIATION TEST CONNECTIONS

OSCILLATOR

FUNCTION

OPEN

GROUND

VDD

Static Burn-In 1

Note 1

3

1, 2, 4 - 6, 7, 8,

9 - 15

16

Static Burn-In 2

Note 1

3

7, 8

1, 2, 4 - 6, 9 - 16

Dynamic BurnIn Note 1

-

4 - 6, 7, 8, 9, 12, 14

1, 2, 13, 15, 16

Irradiation

Note 2

3

7, 8

1, 2, 4 - 6, 9 - 16

9V ± -0.5V

50kHz

25kHz

3

11

10

3, 13

10

9

4, 14, 15

9 - 11

PART NUMBER CD4052BMS

Static Burn-In 1

Note 1

3, 13

1, 2, 4 - 6, 7, 8,

9 - 12, 14, 15

16

Static Burn-In 2

Note 1

3, 13

7, 8

1, 2, 4 - 6, 9 - 12,

14 - 16

Dynamic BurnIn Note 1

-

4 - 6, 7, 8, 12, 15

1, 2, 11, 14, 16

3, 13

7, 8

1, 2, 4 - 6, 9 - 12,

14 - 16

Irradiation

Note 2

PART NUMBER CD4053BMS

Static Burn-In 1

Note 1

4, 14, 15

1 - 3, 5 - 8, 9 - 13

16

Static Burn-In 2

Note 1

4, 14, 15

7, 8

1 - 3, 5, 6, 9 - 13,

16

Dynamic BurnIn Note 1

-

1, 5 - 8, 12

2, 3, 13, 16

4, 14, 15

7, 8

1 - 3, 5, 6, 9 - 13,

16

Irradiation

Note 2

NOTE:

1. Each pin except pin 7 VDD and GND will have a series resistor of 10K ± 5%, VDD = 18V ± 0.5V

2. Each pin except pin 7 VDD and GND will have a series resistor of 47K ± 5%; Group E, Subgroup 2, sample size is 4 dice/wafer, 0 failures,

VDD = 10V ± 0.5V

Typical Performance Characteristics

SUPPLY VOLTAGE (VDD - VEE) = 10V

600

CHANNEL ON RESISTANCE (RON) (Ω)

CHANNEL ON RESISTANCE (RON) (Ω)

SUPPLY VOLTAGE (VDD - VEE) = 5V

AMBIENT TEMPERATURE

(TA) = +125oC

500

400

300

+25oC

200

-55oC

100

-3

-2

-1

0

1

2

3

4

AMBIENT TEMPERATURE

(TA) = +125oC

250

200

+25oC

150

-55oC

100

50

0

-10.0 -7.5

0

-4

300

-5.0

-2.5

0

2.5

5.0

7.5

10.0

INPUT SIGNAL VOLTAGE (VIS) (V)

INPUT SIGNAL VOLTAGE (VIS) (V)

FIGURE 1. TYPICAL CHANNEL ON RESISTANCE vs INPUT

SIGNAL VOLTAGE (ALL TYPES)

FIGURE 2. TYPICAL CHANNEL ON RESISTANCE vs INPUT

SIGNAL VOLTAGE (ALL TYPES)

7-943

CD4051BMS, CD4052BMS, CD4053BMS

600

(Continued)

AMBIENT TEMPERATURE

(TA) = +25oC

CHANNEL ON RESISTANCE (RON) (Ω)

CHANNEL ON RESISTANCE (RON) (Ω)

Typical Performance Characteristics

SUPPLY VOLTAGE (VDD - VEE) = 5V

500

400

300

200

10V

100

15V

SUPPLY VOLTAGE (VDD - VEE) = 15V

300

250

200

AMBIENT TEMPERATURE

(TA) = +125oC

150

100

+25oC

50

-55oC

0

0

-10.0 -7.5

-5.0

-2.5

0

2.5

5.0

7.5

10.0

-10.0 -7.5

INPUT SIGNAL VOLTAGE (VIS) (V)

105

POWER DISSIPATION/PACKAGE (PD) (µW)

OUTPUT SIGNAL VOLTAGE (VOS) (V)

LOAD RESISTANCE

(RL) = 100kΩ, 10kΩ

1kΩ

1500Ω

oC

= +25

100Ω

2

0

-2

-4

-6

-4

-2

0

2

4

INPUT SIGNAL VOLTAGE (VIS) (V)

AMBIENT TEMPERATURE (TA)

= +25oC

ALTERNATING “O” AND

“I” PATTERN

LOAD CAPICATANCE (CL)

= 50pF

103

VDD

10V

102

10V

5V

CD4029

B/D

A B

100Ω 10 9

100Ω

3 CL

13

1

5

12

2

4 CD4051 14

1

15

6

11

7

8

CL = 15pF

Ι

10

10

10.0

TEST CIRCUIT

VDD

B/D

f

VDD

13

14

15

CD4051

12

1

5

2

4 8 7 6

10V

10V

5V

CL = 15pF

103

104

102

SWITCHING FREQUENCY (f) (kHz)

10

CD4029

A B C

11 10 9

100Ω

102

105

VDD

f

7.5

3

Ι CL

100Ω

103

104

102

SWITCHING FREQUENCY (f) (kHz)

105

FIGURE 6. TYPICAL DYNAMIC POWER DISSIPATION vs

SWITCHING FREQUENCY (CD4051BMS)

TEST CIRCUIT

SUPPLY VOLTAGE

(VDD) (15V)

1

5.0

SUPPLY VOLTAGE

(VDD) (15V)

1

POWER DISSIPATION/PACKAGE (PD) (µW)

POWER DISSIPATION/PACKAGE (PD) (µW)

103

AMBIENT TEMPERATURE (TA)

= +25oC

ALTERNATING “O” AND

“I” PATTERN

LOAD CAPICATANCE (CL)

= 50pF

104

6

FIGURE 5. TYPICAL ON CHARACTERISTICS FOR 1 OF 8

CHANNELS (CD4051BMS)

104

2.5

10

-6

105

0

FIGURE 4. TYPICAL CHANNEL ON RESISTANCE vs INPUT

SIGNAL VOLTAGE (ALL TYPES)

6

4

-2.5

INPUT SIGNAL VOLTAGE (VIS) (V)

FIGURE 3. TYPICAL CHANNEL ON RESISTANCE vs INPUT

SIGNAL VOLATGE (ALL TYPES)

SUPPLY VOLTAGE (VDD) = 5V

VSS = 0V VEE = -5V

AMBIENT TEMPERATURE (TA)

-5.0

AMBIENT TEMPERATURE (TA)

= +25oC

ALTERNATING “O” AND

“I” PATTERN

LOAD CAPICATANCE (CL)

= 50pF

104

103

FIGURE 7. TYPICAL DYNAMIC POWER DISSIPATION vs

SWITCHING FREQUENCY (CD4052BMS)

9

100

Ω

SUPPLY VOLTAGE

(VDD) (15V)

10V

5V

CL = 15pF

1

10

13

CD4051

10V

102

4 CL

12

3

5

100Ω

10

105

TEST CIRCUIT

VDD

f

Ι

2

10

1

11

15

6

7

14

8

103

104

102

SWITCHING FREQUENCY (f) (kHz)

FIGURE 8. TYPICAL DYNAMIC POWER DISSIPATION vs

SWITCHING FREQUENCY (CD4053BMS)

7-944

105

CD4051BMS, CD4052BMS, CD4053BMS

VDD = +15V

VDD = +7.5V

16

VDD = +5V

VDD = +5V

16

16

5V

16

5V

7.5V

VSS = 0V

VSS = 0V

VSS = 0V

VEE = 0V

7

8

VSS = 0V

(a)

7

VEE = -7.5V

8

7

VEE = -10V

(b)

8

(c)

The ADDRESS (digital-control inputs) and INHIBIT logic levels are:

“0” = VSS and “1” = VDD. The analog signal (through the TG) may

swing from VEE to VDD

FIGURE 9. TYPICAL BIAS VOLTAGES

7-945

7

VEE = -5V

8

(d)

CD4051BMS, CD4052BMS, CD4053BMS

TRUTH TABLE

INPUT STATES

tf = 20ns

tr = 20ns

“ON” CHANNEL(S)

90%

CD4051BMS

INHIBIT

90%

50%

C

B

A

0

0

0

0

0

0

0

0

1

1

0

0

1

0

2

0

0

1

1

3

0

1

0

0

4

0

1

0

1

5

0

1

1

0

6

0

1

1

1

7

1

X

X

X

NONE

50%

10%

10%

TURN-ON

TIME

tPZL

90%

50%

10%

10%

tPLZ

TURN-OFF TIME

FIGURE 10. WAVEFORM, CHANNEL BEING TURNED ON, OFF

(RL = 1kΩ)

CD4052BMS

tr = 20ns

INHIBIT

B

A

0

0

0

0x, 0y

0

0

1

1x, 1y

0

1

0

2x, 2y

0

1

1

3x, 3y

1

x

x

NONE

tf = 20ns

90%

90%

50%

50%

10%

10%

90%

10%

CD4053BMS

TURN-ON

TIME

tPZH

TURN-OFF TIME

INHIBIT

A OR B OR C

0

0

ax or bx or cx

0

1

ay or by or cy

1

X

NONE

tPHZ

FIGURE 11. WAVEFORM, CHANNEL BEING TURNED OFF, ON

(RL = 1kΩ)

X = Don’t Care

VDD

OUTPUT

OUTPUT

1

VDD

2

15

3

14

4

13

5

VEE

16

6

RL

CL

CL

RL

VDD

VEE

VEE

12

VDD

11

7

10

8

9

VSS

VEE

CLOCK

IN

1

16

2

15

3

14

4

13

5

12

6

11

VDD

7

10

VSS

8

9

VDD

VSS

VSS

VSS

VSS

CD4051

CD4052

VDD

OUTPUT

VEE

1

16

2

15

3

14

4

13

5

12

6

11

7

10

8

9

RL

CL

VEE

VDD

VSS

CLOCK

IN

VSS

VSS

CD4053

FIGURE 12. PROPAGATION DELAY - ADDRESS INPUT TO SIGNAL OUTPUT

7-946

CLOCK

IN

CD4051BMS, CD4052BMS, CD4053BMS

VDD

VDD

OUTPUT

OUTPUT

16

1

RL

50pF

VDD

VDD

VSS

CLOCK

IN

15

2

VEE

RL

50pF

1

16

2

15

3

14

3

14

4

13

4

13

5

12

5

12

6

11

6

11

7

10

7

10

8

9

8

9

VEE

VDD

VDD

VSS

VEE

CLOCK

IN

VEE

VSS

VSS

VSS

VSS

tPHL AND tPLH

tPHL AND tPLH

CD4051

CD4052

OUTPUT

RL

50pF

VEE

VDD

VDD

VSS

CLOCK

IN

1

16

2

15

3

14

4

13

5

12

6

11

7

10

8

9

VDD

VEE

VSS

VSS

tPHL AND tPLH

CD4053

FIGURE 13. PROPAGATION DELAY - INHIBIT INPUT TO SIGNAL OUTPUT

DIFFERENTIAL

SIGNALS

CD4052

CD4052

COMMUNICATIONS

LINK

DIFF

AMPLIFIER/

LINE DRIVER

DIFF

RECEIVER

DIFF

MULTIPLEXING

DEMULTIPLEXING

FIGURE 14. TYPICAL TIME-DIVISION APPLICATION OF THE CD4052BMS

7-947

CD4051BMS, CD4052BMS, CD4053BMS

Chip Dimensions and Pad Layouts

CD4051BMSH

CD4052BMSH

CD4053BMSH

Dimensions in parentheses are in millimeters and are

derived from the basic inch dimensions as indicated.

Grid graduations are in mils (10-3 inch)

METALLIZATION:

PASSIVATION:

Thickness: 11kÅ − 14kÅ,

AL.

10.4kÅ - 15.6kÅ, Silane

BOND PADS: 0.004 inches X 0.004 inches MIN

DIE THICKNESS: 0.0198 inches - 0.0218 inches

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without

notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate

and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which

may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

948

LM6172QML

www.ti.com

SNOSAR4A – DECEMBER 2010 – REVISED OCTOBER 2011

LM6172QML Dual High Speed, Low Power, Low Distortion, Voltage Feedback Amplifiers

Check for Samples: LM6172QML

FEATURES

APPLICATIONS

• Available with Radiation Guarantee

– High Dose Rate 300 krad(Si)

– ELDRS Free 100 krad(Si)

• Easy to Use Voltage Feedback Topology

• High Slew Rate 3000V/μs

• Wide Unity-Gain Bandwidth 100MHz

• Low Supply Current 2.3mA / Amplifier

• High Output Current 50mA / Amplifier

• Specified for ±15V and ±5V operation

•

•

•

•

•

•

•

1

234

Scanner I- to -V Converters

ADSL/HDSL Drivers

Multimedia Broadcast Systems

Video Amplifiers

NTSC, PAL® and SECAM Systems

ADC/DAC Buffers

Pulse Amplifiers and Peak Detectors

DESCRIPTION

The LM6172 is a dual high speed voltage feedback amplifier. It is unity-gain stable and provides excellent DC

and AC performance. With 100MHz unity-gain bandwidth, 3000V/μs slew rate and 50mA of output current per

channel, the LM6172 offers high performance in dual amplifiers; yet it only consumes 2.3mA of supply current

each channel.

The LM6172 operates on ±15V power supply for systems requiring large voltage swings, such as ADSL,

scanners and ultrasound equipment. It is also specified at ±5V power supply for low voltage applications such as

portable video systems.

The LM6172 is built with National's advanced VIP™ III (Vertically Integrated PNP) complementary bipolar

process.

Connection Diagram

8-Pin DIP

Figure 1. Top View

1

2

3

4

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

VIP is a trademark of Texas Instruments.

PAL is a registered trademark of and used under lisence from Advanced Micro Devices, Inc..

All other trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2010–2011, Texas Instruments Incorporated

LM6172QML

SNOSAR4A – DECEMBER 2010 – REVISED OCTOBER 2011

www.ti.com

16LD Ceramic SOIC

N/C

1

16

N/C

OUT A

2

15

N/C

IN- A

3

14

V+

IN+ A

4

13

N/C

N/C

5

12

OUT B

V-

6

11

IN- B

N/C

7

10

IN+ B

N/C

8

9

N/C

Figure 2. Top View

LM6172 Driving Capacitive Load

2

Submit Documentation Feedback

Copyright © 2010–2011, Texas Instruments Incorporated

Product Folder Links: LM6172QML

LM6172QML

www.ti.com

SNOSAR4A – DECEMBER 2010 – REVISED OCTOBER 2011

LM6172 Simplified Schematic (Each Amplifier)

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

Submit Documentation Feedback

Copyright © 2010–2011, Texas Instruments Incorporated

Product Folder Links: LM6172QML

3

LM6172QML

SNOSAR4A – DECEMBER 2010 – REVISED OCTOBER 2011

Absolute Maximum Ratings

www.ti.com

(1)

Supply Voltage (V+ − V−)

Differential Input Voltage

36V

(2)

±10V

Maximum Junction Temperature

Power Dissipation

150°C

(3) (4)

,

Output Short Circuit to Ground

1.03W

(5)

Continuous

Storage Temperature Range

−65°C ≤ TA ≤ +150°C

Common Mode Voltage Range

V+ +0.3V to V− −0.3V

Input Current

±10mA

Thermal Resistance

(6)

θJA

8LD Ceramic Dip (Still Air)

100°C/W

8LD Ceramic Dip (500LF/Min Air Flow)

46°C/W

16LD Ceramic SOIC (Still Air) “WG”

124°C/W

16LD Ceramic SOIC (500LF/Min Air Flow) “WG”

74°C/W

16LD Ceramic SOIC (Still Air) “GW”

135°C/W

16LD Ceramic SOIC (500LF/Min Air Flow) “GW”

85°C/W

θJC

8LD Ceramic Dip

(4)

2°C/W

16LD Ceramic SOIC “WG” (4)

6°C/W

16LD Ceramic SOIC “GW”

7°C/W

Package Weight

8LD Ceramic Dip

980mg

16LD Ceramic SOIC “WG”

365mg

16LD Ceramic SOIC “GW”

410mg

ESD Tolerance

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(7)

4KV

Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for

which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see

the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics

may degrade when the device is not operated under the listed test conditions.

Differential Input Voltage is measured at VS = ±15V.

The maximum power dissipation must be derated at elevated temperatures and is dictated by TJmax (maximum junction temperature),

θJA (package junction to ambient thermal resistance), and TA (ambient temperature). The maximum allowable power dissipation at any