Analysis of Rectifier Topologies for Automotive HV to LV Phase Shift

advertisement

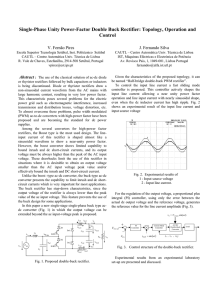

15th International Power Electronics and Motion Control Conference, EPE-PEMC 2012 ECCE Europe, Novi Sad, Serbia Analysis of Rectifier Topologies for Automotive HV to LV Phase Shift ZVT DC/DC Converter Sandra Zeljkovic1, Tomas Reiter1, Dieter Gerling2; 1 2 Infineon Technologies AG, Munich, Germany, sandra.zeljkovic@infineon.com Universiteat der Bundeswehr Muenchen, Neubiberg, Germany, dieter.gerling@unibw.de Abstract — Full bridge phase shift zero voltage transition (ZVT) converter is a standard topology for the automotive high voltage (HV) to low voltage (LV) DC/DC converter. One of the major issues due to the required wide input and output voltage range is the voltage overshoot during the turn-off process of rectifier MOSFET switches. This paper presents a model to simulate turn-off voltage waveforms of switches for different rectifier topologies. Experimental verification on a 3kW converter prototype shows that the model is accurate regarding voltage overshoot value and the oscillation frequency, and that reverse recovery of body diodes has no significant effect on the overshoot. In comparison to two other rectifier topologies, the bridge rectifier has the lowest requirements regarding the switch breakdown voltage, resulting in decreased power losses and eliminating the need for complex clamping/snubber circuits in this specific application. Keywords —Hybrid and electrical vehicles, HV to LV DC/DC converter, phase shift ZVT DC/DC converter, full wave rectifier, bridge rectifier, current doubler, voltage overshoot, RC snubber I. INTRODUCTION Hybrid electric (HEV) and electric vehicles’ (EV) power net architectures are still using the conventional 14V power net to supply low power loads (infotainment, lighting…) with a power demand in range of 1-3kW. As the belt driven alternator is no more part of this system architecture, a DC/DC converter takes over the role to supply the LV power net from the HV power net. The typical set of requirements is given by the automotive industry and one example is presented in Table I. Several converter topologies are in general suitable to meet these requirements. The phase shift ZVT DC/DC converter (Fig. 1) is a commonly used topology in this application and therefore selected for the investigation in this paper. Fig. 1 Phase shift ZVT DC/DC converter topology The principle of operation is explained in [1], [2], [3] and [4]. The lossless turn-on of switches on the primary 978-1-4673-1972-0/12/$31.00 ©2012 IEEE side of the converter is achieved with fixed frequency operation thanks to the phase shift control and using parasitic elements in the circuit (transformer leakage , switches’ output capacitance, ). inductance, In case of the phase shift control, switches in the same leg (S1 and S3, or S2 and S4) are always turned on during 50% of the switching period T. The switching patterns of the diagonal switches (S1 and S4, or S2 and S3) are phase shifted one over another (Fig. 2), determining in that way the duty cycle D. During the freewheeling period, the primary winding of the transformer is shorted by a switch and an antiparallel diode. The circulating transformer current during the freewheeling enables the lossless turn on of the switches (ZVT) by charging/discharging the parasitic capacitances. On the rectifier side (Fig. 1), during the power transfer period, diagonal switches (SR1 and SR4, or SR2 and SR3) are on, while in the freewheeling, all switches are simultaneously on. Waveforms of primary winding current, synchronous rectifier (SR) voltages and switching patterns are presented in Fig. 2. The design considerations for ZVT DC/DC converters, which are reported in the literature, are mostly oriented to applications with a “tight” input voltage range. In [5], the converter is used after a power factor correction (PFC) stage which regulates the input voltage between 370 to 410V. Such a design gives the opportunity to optimize the circuit parameters and control in order to get a high efficiency over the complete range of operating points. If the factor of input voltage range is defined , 1, the considered automotive with , 200 and , 400 has application with , more than 9 times higher input voltage range compared to the one after the PFC stage in [5]. Thus, some design considerations of the converter for such an application differ slightly from those mostly given in the literature. An often reported problem of the phase shift ZVT DC/DC converter is the high voltage overshoot during the turn off process of rectifier switches [1], [3], [6] and [7]. In [6] and [7] this phenomenon is partially assigned to the reverse recovery charge of the rectifier diodes. However, the model in this paper neglects the reverse recovery, what is explained in Section IV.C. After design considerations for the converter (Section II), the model that describes the turn off process for different rectifier topologies is presented in Section III. The model is used for the components selection and DS1b.4-1 further comparison of different rectifier topologies in Section IV. The experimental validation of the introduced model is given in Section V. c) Fig. 3 Investigated rectifier topologies a) Full wave rectifier b) Current doubler c) Bridge rectifier Fig. 2 Primary winding current, synchronous rectifiers (SR) voltages and switching patterns for primary and secondary switches TABLE I TYPICAL REQ. FOR HV TO LV DC/DC CONVERTER FOR (H)EV min typical max Input voltage 200V 300V 400V Output voltage 8V 14V 16-18V Output current 0A 200A Output power 0.4 – 0.8kW Switching frequency 100kHz Efficiency > 90% 3kW B. Transformer voltage turn ratio The required turn ratio of the transformer is determined by the maximum steady state duty cycle needed at minimum input voltage and maximum load and are voltage drops on the current. , , primary and secondary side respectively (over active components, resistances of the transformer, leads etc.). The value of voltage drop on the primary side is of the IGBT estimated taking into account , switches used at the primary side (1.5V at 25A), [4], and a margin of 1V for the voltage drop over the parasitic resistances in the circuit. The voltage drop on the secondary side is estimated considering the MOSFET´s (two switches in parallel) and the maximum load , current. Again some margin for voltage drops over the parasitic resistances of the setup is taken into account. Such a simplified estimation for voltage drops is accurate enough considering that in a real implementation the transformer turn ratio can only be an integer number. The required turn ratio in case of the full wave and bridge rectifier can be calculated using (1) and in case of current doubler with (2): , · , , II. DESIGN CONSIDERATIONS , A. Design targets The motivation for the investigation in this paper is to choose the most suitable of three mainly used rectifier topologies presented in Fig. 3, taking into account the wide input voltage range. The main goals should be the lowest steady state blocking voltage of applied rectifier switching components (thus lower , ), the lowest conduction losses as well as decreased voltage overshoot on the rectifier side. The possibility to use only RC snubber instead of solutions with RCD snubbers or different clamping circuits is also desired. a) b) · , · , , (1) . (2) The steady state turn ratio of current doubler is , (3) leading always to lower transformer ratio required compared to other two topologies in the same operating conditions. TABLE II TRANSFORMER VOLTAGE TURN RATIO CALCULATION Full wave Current Bridge rectifier doubler rectifier 200 V V , 0.8 p.u. D 14.4 V V 200 A I , 4V V , 1V 0.5V 0.5V V , Transformer turn 10:1:1 5:1 10:1 ratio Input Steady voltage state blocking 200V 40V 40V 20V voltage 400V 80V 80V 40V of rec. switches DS1b.4-2 III. THE PROBLEM OF THE RECTIFIER VOLTAGE OVERSHOOT A. Root causes of the rectifier voltage overshoot Each switching cycle of the converter operation consists of period of energy transfer from the primary to the secondary side, the freewheeling period and the transition between them (Fig. 2). Due to the phase shift control, freewheeling period is characterized by voltage close to zero across the primary side of the transformer, and thus all rectifier switches are conducting simultaneously. During the transition to power transfer, two diagonal rectifier switches are turned off. Now, the voltage over the rectifier switch has to be increased from the value in conducting state to the value in blocking has to be charged to the state. Its output capacitance value of the blocking voltage. The parasitic inductance in the circuit forms a series resonant circuit with the output capacitances of the switches that turn off. The is a sum of the leakage inductance of the inductance and parasitic transformer secondary winding , inductances in the circuit on the current path. The resonance effect is damped by resistance present in the circuit ( ) that consists of the resistance of secondary transformer winding, resistance of leads, resistance of the conducting MOSFETs etc. Differences among investigated rectifier topologies result in both different steady state blocking voltage and overshoot values of rectifier switches. When the full wave rectifier is used, a center tapped transformer is of both secondary windings are required. Now , contributing to the overvoltage peak values, but only of a single switch contributes to the voltage overshoot (Fig. 4). Fig. 4 Functional and equivalent circuit of full wave rectifier during the turn off transition of one switch In case of the current doubler, the secondary winding form the resonant circuit (Fig. 5). and Fig. 6 Functional and equivalent circuit of bridge rectifier during the turn off transition of one leg In case of the full bridge rectifier (Fig. 6), the resonant circuit is formed by as well as ,1 and ,2 of the diagonal turning off. During the transition of the rectifier switch from conducting to blocking state, the current of the filter inductor can be considered constant. Figure 7 shows the mathematical description of the equivalent resonating circuit during the turn off transition, generalized in order to describe all three topologies with a single model. Due to the order of (tens of ) and , and magnitude of , in the circuit, the damping is the parasitic resistance rather low. Thus, a RC snubber for rectifier switches is required. With such a snubber, the system is described with a third order differential equation. The rate of change / and the steady state value of input voltage in Fig. 7 are determined by primary side of the converter. and the capacitances of RC Both MOSFET’s are voltage snubber are charged. The MOSFET’s dependent and can be approximated with (4) from [8]: (4) 1 The value of the voltage overshoot as well as frequency of oscillations will be estimated using this model for three different rectifier topologies. The ⁄ of the voltage applied to the resonating circuit is the factor that should not be neglected in this analysis. This value depends on the technology of switches on the primary side, gate driving circuit, load current as well as other parameters. A typical value of 5 ⁄μ (based on the dynamic characteristic of Infineon’s high speed IGBT3) is used in the simulation. The coefficient to the voltage overshoot shows the effect of , shows the effect of of the waveform, while switches. In case of full wave rectifier with center-tapped of both windings would affect the transformer, , 2. In voltage overshoot. Thus, for full wave rectifier the other two topologies, due to the single secondary 1. In the same manner, in the bridge winding, is twice as high as rectifier, the effect of MOSFETs’ in case of the other two topologies. Two switches are in parallel to secondary winding and each switch consists of in the two MOSFETs. Thus, multiplying factor of 4. model in Fig. 7 is Fig. 5 Functional and equivalent circuit of current doubler during the turn off transition of one switch DS1b.4-3 R par vin ∑ 1 k1 ⋅ Ll , s + Lpar 1 s isec ∑ IL iCoss k 2 ⋅ C oss ⋅ isnub vCoss 1 s V meas V C oss k2 Rs 1 k2 ⋅ Cs 1 s a) input voltage of 200V b) input voltage of 400V Fig. 7 Mathematical description of rectifier switch transition from conducting to non-conducting state TABLE III CIRCUIT PARAMETERS AND OPERATING CONDITIONS Bridge Full wave Current rectifier rectifier doubler Circuit parameters EPCOS Transforme From table II T9673 r turn ratio 0.014µH 0.014µH 0.028µH , (1.4µH/100) IPB025N10N3 G (0.7µH/25) Fig. 8 Simulation of voltage overshoots waveforms for three different rectifier topologies ~0.05µH ~ 1mΩ 2 Number of component s in parallel Input voltage (1.4µH/100) IV. Based on the simulation results from Section III, the secondary side switches are dimensioned in this section. A comparison of the rectifier conduction losses also follows. 2.58nF 2.5mΩ 50V 10Ω 2nF Operational point a) 200V Load current Output voltage (regulated) 1 4 b) 20A 14V 2 2 SELECTION OF RECTIFIER SWITCHES AND COMPARISON OF CONDUCTION LOSSES 400V 1 2 The leakage inductance for different transformer turn ratios in Table III is calculated based on values for the EPCOS transformer T6973 with turn ratio 8:1, assuming the same coupling factor for all transformers in the same technology (Appendix). Voltage waveforms across the rectifier switch during the transition from on to off state are simulated for an input voltage of 200V (Fig. 8a) and input voltage 400V (Fig. 8b). The waveforms are obtained using the model from Fig. 7 and parameters listed in Table III. From Fig. 9a it can be seen that either by increasing or the the transformer leakage inductance , voltage overshoot MOSFETs’ output capacitance values are increasing. Due to orders of magnitude of and in the application, overshoot values are . The trend of the more significantly affected by change in oscillation frequency is presented in Fig. 9b. As and should be minimized to get a result, both lowest voltage overshoot and reduce losses in the system. A. Blocking voltage and on-resistance of rectifier components Considering the maximum input voltage (400V) and calculated transformer turn ratio (Table II), the voltage overshoot and thus the required blocking voltage of the rectifier switches are estimated (Fig. 12). The expected blocking voltage in steady state in case of full wave rectifier will be 80V, but the voltage overshoot will be higher than 150V, which unavoidably leads to the choice =200V. In case of components with blocking voltage of current doubler, blocking voltage of rectifier switches is also 80V, but voltage overshoot is over 160V. Again, =200V would be required. Full components with of bridge rectifier allows the use of components with 80V. DS1b.4-4 Fig. 10 Lowest Rds,on = f(Vbr) for Infineon’s OptiMOS™ in a D2PAK package (source : www.infineon.com, released product, October 2011) a) b) Trend of Trend of , dependency on the dependency on the and C. Effect of the load current on the voltage overshoot In the model (Fig. 7), voltage overshoot is neither nor by affected by transformer secondary current , of the converter. This fact is justified the load current both when channel or body diode of secondary side MOSFET is conducting prior to the turn off. The voltage of the MOSFET that turns off can start rising only when the current through the switch naturally falls to zero. Otherwise, the body diode will conduct the current and will clamp the switch voltage to the value equal to diode voltage drop. The turn off process starts when . Although the current through the secondary , is not zero at the moment of turning off winding , is taken over by the switch, the complete load current the opposite, conducting switch in the same leg, and the of the resonating circuits from Fig. 4, initial current Fig. 5 and Fig. 6 is zero. and Fig. 9 Dependency of voltage overshoot on and B. Rectifier conduction loss comparison Because of the lightly doped region needed to , power MOSFETs with higher achieve higher have also the higher on-resistance [8]. As an example, the on is shown in Fig. 10 for dependence of the , Infineon’s low voltage MOSFET family OptiMOS™. The bridge rectifier topology requires twice a higher number of components. Therefore, higher conduction losses than in the other two topologies are expected. A fair comparison of conduction losses, on the other hand, has to be applied with equal die size. In this example, the loss comparison is based on 8 times the lowest , MOSFETs in D2Pak package (Fig. 10). The conduction ), current doubler losses of the bridge rectifier , and full wave rectifier ( are: , , 4 ·0.5·1.9mΩ· (100A) ² = 38W, ( 80 ), , 2·0.25·11mΩ· (100A) ² = 55W, ( 200 ), , 2·0.25·11mΩ· (100A) ² = 55W, ( , 200 ). The results show the lowest conduction losses in case of bridge rectifier topology despite twice a higher number of components compared to other two topologies (Fig. 11). DS1b.4-5 Fig. 11 Comparison of conduction losses V. EXPERIMENTAL RESULTS Three different rectifier topologies for the phase shift ZVT DC/DC converter were used in the laboratory to verify the model from Fig. 7. Based on the component parameters from the setup, taking into account the value of RC snubber, values of voltage overshoot predicted by simulations are compared to measured values. The parameters of the circuit are given in Table II, except for the transformer turn ratio, and consequently the leakage inductance of the windings. The transformer turn ratio was chosen differently because of components availability and parameters are shown in Table IV. In the presented design, because of low values of output capacitances of applied switches on the primary side (Infineon’s High Speed IGBT 3), only relatively low leakage inductance of the transformer is enough to achieve the ZVT on the leading leg over the complete operating range. Furthermore, due to the low value of the transformer leakage inductance, the parasitic inductance . in the secondary circuit becomes dominant over , The parasitic inductance in experimental setup was slightly higher than estimated value in Table III (~65nF). Comparisons of voltage overshoot values for three different topologies in the same operating point obtained by simulation and measurement are presented in Fig. 12. TABLE IV CHARACTERISTICS OF TRANSFORMERS USED IN EXPERIMENTAL SETUP Full wave Current rectifier doubler Circuit parameters EPCOS Transformer 8:1:1 7:1 T9673 turn ratio 0.8µH/64 0.8µH/49 , Operational point 200 200 Input voltage (V) 20 10 Load current (A) a) Full wave rectifier (200V, 8:1:1) Full bridge 8:1 0.8µH/64 400 b) Current doubler (200V, 7:1) c) Bridge rectifier (400V, 8:1) Fig. 12 Comparison of voltage overshoot values for three different topologies in the same operating point obtained by both simulation and measurement Measurements on the prototype confirmed the analysis from Section IV.C that voltage overshoot is independent of the load current and transformer winding current in the moment of turning off (Fig. 13). Experimental verification is done with optimized snubber 3.3 ; 13.6 . values 20 Fig. 13 Voltage overshoot values for different load currents: experimental (markers) and simulation results (solid lines) in case of bridge rectifier DS1b.4-6 VI. CONCLUSION The discussed automotive application requires wide input and output voltage ranges of the converter. The converter has to be designed for the minimal required value of input voltage and thus cannot be optimized for all operating conditions. One of the consequences is the excessive voltage overshoot over the rectifier side switches when higher input voltages are applied. The simulation model of the rectifier turn-off process showed that the transformer leakage inductance together with the output capacitance of the switches is the major contributor to the voltage overshoot. Both additional on the resonating inductance and switches with high primary side only intensify the overshoot problem. will also contribute MOSFET switches with higher to overshoots. The investigations showed that the bridge rectifier can significantly reduce the steady state blocking voltage as well as the voltage overshoot of the rectifier switches. Despite the higher number of switching components, this topology not only helps avoiding additional efforts for RCD or active snubbers but is also characterized by the lowest conduction power losses. The effect of the rectifier stage on the total converter efficiency will be focus of the future work. APPENDIX Knowing the primary (secondary) winding inductance ( ) and coupling factor of the transformer k, the leakage inductance of the primary (secondary) winding ( ) can be approximated using: , , 1 · (5) , 1 · (6) , DS1b.4-7 REFERENCES [1] [2] [3] [4] [5] [6] [7] [8] L.H.Mweene, C.A.Wright, M.F.Schlecht, “A 1 kW, 500 kHz front-end converter for a distributed power supply system”, Applied Power Electronics Conference and Exposition, 1989. APEC' 89. Conference Proceedings 1989., Fourth Annual, pp.423-432, 13-17 March 1989 J.A.Sabate, V.Vlatkovic, R.B.Ridley, F.C.Lee, B.H.Cho, “Design considerations for high-voltage high-power fullbridge zero-voltage-switched PWM converter”, Applied Power Electronics Conference and Exposition, 1990. APEC '90, Conference Proceedings 1990., Fifth Annual , pp.275284, 11-16 March 1990 J.A.Sabate, V.Vlatkovic, R.B.Ridley, F.C.Lee, “Highvoltage, high-power, ZVS, full-bridge PWM converter employing an active snubber” Applied Power Electronics Conference and Exposition, 1991. APEC '91. Conference Proceedings, 1991., Sixth Annual , pp.158-163, 10-15 March 1991 T.Reiter, S.Zeljkovic, “Design of an automotive 2.5kW HV to LV DC/DC converter using HighSpeed IGBTs“, Elektrik/Elektronik in Hybrid und Elektrofahrzeugen und elektrisches Energiemanagement, Miesbach 2012 Texas Instruments, “UCC28950 600-W, Phase-Shifted, FullBridge”, Application Report, 2010 N.H.Kutkut, D.M.Divan, R.W.Gascoigne, “An improved full-bridge zero-voltage switching PWM converter using a two-inductor rectifier”, IEEE Transactions on Industry Applications, vol.31, no.1, pp.119-126, Jan./Feb. 1995 R.Redl, N.O.Sokal, L.Balogh, “A novel soft-switching fullbridge DC/DC converter: analysis, design considerations, and experimental results at 1.5 kW, 100 kHz”, IEEE Transactions on Power Electronics, vol.6, no.3, pp.408-418, July 1991 R.Erickson, D.Maksimović, “Fundamentals of Power Electronics”, University of Colorado Boulder, Second Edition, 2001