A Simple CMOS-Based Membership Function Circuit | SpringerLink

advertisement

Analog Integrated Circuits and Signal Processing, 32, 83–88, 2002

C 2002 Kluwer Academic Publishers. Manufactured in The Netherlands.

A Simple CMOS-Based Membership Function Circuit

MAHMUT TOKMAKÇI∗ , MUSTAFA ALÇI AND RECAI KILIÇ

Erciyes University, Department of Electronic Engineering, 38039, Kayseri, Turkey

E-mail: tokmakci@erciyes.edu.tr

Abstract. In this study, design and analysis of a voltage-input current-output simple CMOS-based Membership

Function Circuit (MFC) is presented. The proposed MFC is based on simple OTA structure and current-mode

maximum circuits. This MFC implements basic four membership functions (trapezoidal, triangle, Z-shape and

S-shape). The characteristics (width, height, slope and position) of the implemented membership functions are

easily adjustable and it is suitable for current-mode fuzzy hardware. While the circuit’s membership function

characteristics have been confirmed by PSPICE-DC simulations, the circuit’s transient response has been analyzed

applying up to 10 MHz input signals in continuous time by PSPICE Transient simulations.

Key Words: membership function circuit, current-mode fuzzy hardware

I.

Introduction

Recently, fuzzy theory has been applied extensively

to control and expert systems [1–10]. In addition to

the theoretical studies, there have been many hardware implementations of fuzzy systems. These implementations of fuzzy systems include analog [1–3],

digital [4–6], and mixed-signal [7–12] building circuit

blocks. Analog circuits present several advantages in

front of digital ones, especially regarding speed of processing, power dissipation and functional density. They

can moreover perform continuous-time processing and

have the particularity to be well compatible with sensors, actuators and all other analog signals. On the other

hand, digital circuits are superior to analog circuits in

accuracy, extendibility, and easy of design automation.

The mixed-signal Fuzzy Logic Controllers (FLC) have

essentially analog circuit structures. However, control

and coordinating signals are generated with digital circuits and/or systems for fuzzy inference while fuzzy

processing is analog form. Such a mixed-signal fuzzy

hardware system offers the advantages of both analog

and digital circuit structures.

In mixed-signal and analog implementations, it is

most preferable the CMOS-based designs and currentmode circuit building blocks, due to the requirements

∗ Corresponding

author.

of high speed, low power and reduced system chip size

[7–10]. So in this study, a current-mode MFC which

is voltage-input current-output is proposed. This MFC

has capability of generation of basic four membership

functions.

II.

Circuit Description

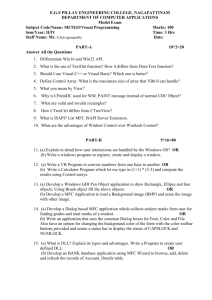

The building block of proposed Membership Function

Circuit (MFC) is shown in Fig. 1. This MFC is composed of two simple OTA structures, two current-mode

maximum circuits (C-Max), a N-MOS current mirror

(CM), and two current sources (Ipeak , Ilevel ). OTA circuit

structure used in Fig. 1 for designing MFC is shown in

Fig. 2.

OTA circuit has simple and basic hardware. Output

current of OTA is defined as follows:

Iout =

√

KI b (Vin+ − Vin− )

(1)

where K is technological parameter which depends on

device geometry and process.

The circuit diagram of each maximum circuit [13]

used in MFC and its DC response are shown in Fig. 3(a)

and 3(b), respectively. As shown in Fig. 3(b), maximum circuits used in proposed MFC structure operate according to positive input currents. For providing

84

Tokmakçı, Alçı and Kılıç

Imfc

VL1 VL2

Ipeak

Ib1

Ilevel

VL2

gm1

Imax1

Vin

C-Max1

VL1

Imax2

Ipeak

CM

Imfc

1:1

C-Max2

gm2

Vin

VL1 VL2

IR

IL

Ilevel

VL1 VL2

Ib2

Fig. 1. The building block of the proposed MFC.

VDD

M1

M2

M3

M5

M6

Iout

Vin

Vin

M7

M4

Ib

(I R , I L ), respectively. When bias currents are equal, the

transconductances of two OTAs will be equal. In this

case, triangular or trapezoidal functions in symmetric

form can be obtained.

First current-mode maximum circuit (C-Max1 )

maximizes the piecewise linear output characteristics

of two OTAs. The output currents of two OTAs (I L , I R )

are defined equations (2) and (3).

I L = gm2 (VL1 − Vin )

where gm2 =

I R = gm1 (Vin − VL2 )

where gm1 =

√

√

KI b2

(2)

KI b1

(3)

M8

The output current of C-Max1 circuit is expressed by:

Imax1 = max{I L , I R }

VSS

Fig. 2. Simple OTA circuit structure.

more linear response, C-Max1 circuit eliminates the

nonlinear characteristics in negative region of OTAs.

This behavior of C-Max1 also determines central points

of membership function as VL1 and VL2 which are

zero-crossing points of OTAs. For linearization of the

nonlinear characteristics of OTAs in positive region,

a current mirror, which inverts the output of C-Max1 ,

and second maximum circuit C-Max2 are used in MFC

structure.

Bias currents, Ib1 and Ib2 are adjustable to determine the slopes of left and right OTA output currents

(4)

In order to provide that MFC operates in linear range

of output membership function, second current-mode

maximum circuit (C-Max2 ) is used as a normalization

part of MFC. Here, while Ipeak current source is used to

determine the peak level of the output signal Imfc , Ilevel

current source is used to determine the base level of

the output signal Imfc . In our study, the base level of the

output signal is fixed to zero level. The output current

of C-Max2 circuit which constitutes the current output

of the proposed MFC is given by

Imfc = max{(Ipeak − Imax1 ), Ilevel }

(5)

where Imax1 current is equivalent to −I max2 due to

current mirror CM.

A Simple CMOS-Based Membership Function Circuit

85

VDD

M9

M8

I2

I1

I1

Imax

M7

M6 M5

M3

M2

Imax

M4

I2

C-MAX

M1

VSS

(a)

50 A

0 A

–10 A

–50 A

–50A –40A

I2

I1

–20A

0A

I2

20A

40A 50A

Inputs of MAX circuit

50A

0A

–50A

–50A –40A

Imax

–20A

0A

I2

20A

40 uA 50A

output of MAX circuit

(b)

Fig. 3. (a) Current-mode maximum circuit and its block diagram. (b) DC response of current-mode maximum circuit (I1 = −10 µA,

−50 µA < I2 < 50 µA).

III.

Simulation Results

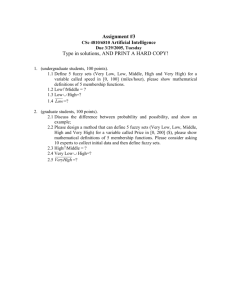

The simulation results of basic four membership functions implemented by proposed MFC are

shown in Fig. 4. In our simulation experiments,

the circuit parameter values are determined as follows: Ib1 = Ib2 = 25 µA, Ipeak = 25 µA, Ilevel = 0 µA

and supply voltages, VDD = 5 V and VSS = −5 V.

While triangular function is obtained on condition

that VL1 = VL2 , trapezoidal function is obtained on

86

Tokmakçı, Alçı and Kılıç

30A

30A

20A

20A

Imfc

10A

Imfc

10A

0A

0V

1.0V

2.0V

3.0V

4.0V

5.0V

Vin

0A

0V

0.5V

1.0V

(a)

30A

20A

20A

Imfc

10A

Imfc

10A

1.0V

2.0V

2.5V

3.0V

(a)

30A

0A

0V

1.5V

Vin

2.0V

3.0V

4.0V

5.0V

Vin

0A

0V

1.0V

2.0V

Vin

(b)

3.0V

4.0V

5.0V

(b)

30A

Fig. 5. MFC position tunability (a) for triangular form, and (b) for

trapezoidal form.

20A

Imfc

10A

0A

0V

1.0V

2.0V

3.0V

4.0V

5.0V

3.0V

4.0V

5.0V

Vin

(c)

30A

20A

Imfc

10A

0A

0V

1.0V

2.0V

cuit [14]. Whereas, the proposed MFC in this study

has capability of generating four standard membership

functions without extra devices.

The position tunability of MFC is shown in Fig. 5(a)

and (b) for triangular and trapezoidal functions, respectively. The position tunability is realized by adjusting

both VL1 and VL2 voltages.

Figure 6(a) and (b) show the width tunability of

MFC towards right and left, respectively. The width

Vin

(d)

30A

Fig. 4. The basic membership function output graphs of proposed

MFC (Ib1 = Ib2 ). (a) Triangle (VL1 = VL2 = 2.0 V), (b) Trapezoidal

(VL1 = 1.0 V, VL2 = 1.5 V), (c) Z-shape (VL1 = 0 V, VL2 = 2.0 V),

and (d) S-shape (VL1 = 3.0 V, VL2 = VDD ).

20A

Imfc

10A

0A

0V

condition that VL2 > VL1 (Fig. 4(a) and (b)). If the position adjusting voltages are determined as VL1 = 0 V and

0 < VL2 < VDD (5 V), output function of MFC will be

Z-shape form depending on VL2 (Fig. 4(c)). If these

voltages are determined as VL2 = VDD and 0 <

VL1 < VDD , output function of MFC will be S-shape

form depending on VL1 (Fig. 4(d)). Most of the membership function circuits in literature [10–11] have

been designed to provide two membership functions

as triangle and trapezoidal shapes in general. In addition to triangle and trapezoidal functions, for generating Z-shape and S-shape membership functions extra

devices are required in original membership cir-

0.5V

1.0V

1.5V

2.0V

Vin

2.5V

3.0V

3.5V

4.0V

4.5V

5.0V

(a)

30A

20A

Imfc

10A

0A

1.5V

2.0V

2.5V

3.0V

3.5V

Vin

(b)

Fig. 6. Width tunability of proposed MFC (a) Right directions, and

(b) Left directions.

A Simple CMOS-Based Membership Function Circuit

30A

87

1.0V

0.5V

20A

Imfc

10A

0V V

in

40A

20A

0A

1.5V

2.0V

2.5V

Vin

3.0V

3.5V

0A

0s

Imfc

2s

4s

6s

Time

8s

10s

12s

2.0s

2.5s

3.0s

Frequency of Input Signal = 250 khz

(a)

(a)

30A

1.0V

20A

0.5V

Imfc

10A

0A

1.5V

0V V

in

40A

2.0V

2.5V

Vin

3.0V

3.5V

20A

0A

0s

(b)

Imfc

0.5s

1.0s

Frequency of Input Signal = 1 Mhz

1.5s

Time

(b)

Fig. 7. MFC slope tunability (a) Right side, and (b) Left side.

1.0V

0.5V

tunability of MFC is realized by fixing one of the voltages VL1 and VL2 , and the other changing.

In Fig. 7(a) and (b), the slope tunability of MFC

with triangular form is shown. These figures have been

obtained by fixing one of the bias currents, Ib1 and Ib2 ,

and the other changing.

The transient response of MFC with 250 kHz,

1 MHz, 2 MHz, and 8 MHz input signals as triangle

form is shown in Fig. 8(a), (b), (c), and (d), respectively. As shown in Fig. 8, the output waveform of

proposed circuit is able to preserve approximately the

original form when applying input signals up to frequency 8 MHz. Here, maximum delay time is less

than 70 ns.

IV.

Conclusion

A CMOS-based MFC with voltage-input currentoutput has been designed and analyzed. Its behavior was confirmed by Pspice simulation experiments.

Due to simplicity of OTA circuits, this MFC has a

simple hardware. Basic four membership functions

(trapezoidal, triangle, Z-shape and S-shape) can be implemented by this MFC. The characteristics (width,

height, slope and position) of the implemented membership functions are easily adjustable and it is suitable

for current-mode fuzzy hardware.

0V V

in

40A

20A

0A

0s

Imfc

0.5s

1.0s

1.5s

Time

Frequency of Input Signal = 2 Mhz

(c)

1.0V

0.5V

0V V

in

40A

20A

0A

0s

Imfc

100ns

Frequency of Input Signal = 8 Mhz

200ns

Time

300ns

375ns

(d)

Fig. 8. The transient response of the proposed MFC with

(a) 250 kHz, (b) 1 MHz, (c) 2 MHz, (d) 8 MHz triangular input signals. In figures, while upper trace shows input signal, lower trace

shows output of MFC.

References

1. Ascia, G. and Catania, V., “A high performance processor for

applications based on fuzzy logic.” FUZZ-IEEE ’99 IEEE V.

Fuzzy Systems International Conference Proc. 3, pp. 1685–1690,

1999.

2. Khoei, A., Hadidi, K. and Peyravi, H., “Analog realization

of fuzzifier and defuzzifier interfaces for fuzzy chips.” Fuzzy

Information Processing Society—NAFIPS ’98 Conference of

the North American, pp. 72–76, 1998.

88

Tokmakçı, Alçı and Kılıç

3. Wilamowski, B. M., “Analog VLSI hardware for fuzzy systems.”

IEEE Industrial Electronics Society IECON ’98 Proceedings of

the 24th Annual Conference 1, pp. 52–55, 1998.

4. Sultan, L., “FDSP: a VLSI core for adaptive fuzzy and digital

signal processing applications.” ISCAS ’98 IEEE International

Symposium on Circuits and Systems Proc. 3, pp. 123–126, 1998.

5. Sánchez-Solano, S., Barriga, Á., Jimenez, C. J. and Huertas,

J. L., “Design and application of digital fuzzy controllers.” IEEE

the Sixth International Conference on Fuzzy Systems Proc. 2,

pp. 869–874, 1997.

6. Patyra, M. J., Grantner, J. L. and Koster, K., “Digital fuzzy logic

controller: design and implementation.” IEEE Trans. on Fuzzy

Systems 4(4), pp. 439–459, 1996.

7. Alarcón, E., Iannazzo, M., Madrenas, J., Moreno, J. M.,

Gombriz, S., Guinjoan, F. and Poveda, A., “Implementation of an application-specific fuzzy controller by means

of a mixed-signal sequential architecture.” IEEE Midwest

Symposium on Circuits and Systems Proc. pp. 430–433,

1998.

8. Bouras, S., Suyama, K. and Tsividis, Y., “Integrated fuzzy logic

controller with continuous processing.” IEEE the Fifth International Conference on Fuzzy Systems Proc. 3, pp. 1951–1957,

1996.

9. Çilingiroğlu, U., Pamir, B., Günay, Z. S. and Dülger, F.,

“Sampled-analog implementation of application-specific fuzzy

controllers.” IEEE Trans. on Fuzzy Systems 5(3), pp. 431–442,

1997.

10. Baturone, I., Sánchez-Solano, S., Barriga, Á. and Huertas,

J. L., “Implementation of CMOS fuzzy controllers as mixedsignal integrated circuits.” IEEE Trans. on Fuzzy Systems 5(1),

pp. 1–19, 1997.

11. Bouras, S., Kontronakis, M., Suyama, K. and Tsividis, Y.,

“Mixed analog-digital fuzzy logic controller with continuousamplitude fuzzy inferences and defuzzification.” IEEE Trans.

on Fuzzy Systems 6(2), pp. 205–215, 1998.

12. Rodrı́guez-Vázques, A., Navas, R., Delgado-Restituto, M. and

Vidal-Verdú, F., “A modular programmable CMOS analog fuzzy

controller chip.” IEEE Trans. on Circuits and Systems-II 46(3),

pp. 251–265, 1999.

13. Baturone, I., Huertas, J. L., Barriga, Á. and Sánchez-Solano, S.,

“Current-mode multi-input max circuit.” IEE Electronics Letters

30(9), pp. 678–680, 1994.

14. Carvajal, R. G., Torralba, A., Colodro, F. and Franquela, L. G.,

“Mixed-signal CMOS fuzzifier with emphasis in power consumption.” IEEE 42nd Midwest Symp. on Circuits and Systems

2, pp. 929–933, 2000.