Design for Manufacturing: IPC Webinar August 3rd, 2011

advertisement

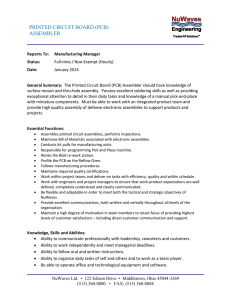

Design for Manufacturing: IPC Webinar rd August 3 , 2011 Cheryl Tulkoff Senior Member of the Technical Staff ctulkoff@dfrsolutions.com 1 Instructor Biography Cheryl Tulkoff has over 20 years of experience in electronics manufacturing with an emphasis on failure analysis and reliability. She has worked throughout the electronics manufacturing life cycle beginning with semiconductor fabrication processes, into printed circuit board fabrication and assembly, through functional and reliability testing, and culminating in the analysis and evaluation of field returns. She has also managed no clean and RoHS-compliant conversion programs and has developed and managed comprehensive reliability programs. o Cheryl earned her Bachelor of Mechanical Engineering degree from Georgia Tech. She is a published author, experienced public speaker and trainer and a Senior member of both ASQ and IEEE. She holds leadership positions in the IEEE Central Texas Chapter, IEEE WIE (Women In Engineering), and IEEE ASTR (Accelerated Stress Testing and Reliability) sections. She chaired the annual IEEE ASTR workshop for four years and is also an ASQ Certified Reliability Engineer. o She has a strong passion for pre-college STEM (Science, Technology, Engineering, and Math) outreach and volunteers with several organizations that specialize in encouraging pre-college students to pursue careers in these fields. o 2 Webinar Outline o o 3 Design for manufacturability (DFM) best practices ensure that manufacturing capability is taken into consideration during the design and layout of a product. By understanding the potential effects of — and how to avoid — overtaxing their manufacturer, engineers can be confident in the execution of their design. Attendees will come away with a greater comprehension of the potential manufacturability hazards to avoid during the design process, and an understanding of the benefits of DFM. What You Will Learn o M.S.L, handling, process optimization and control strategies, repair and rework o Matching PCB complexity to supplier capabilities o Influences of PCB thickness, cut-outs, and depanelization techniques on reliability o Printed board design and process material selection o Equipment process controls and reliability testing Design for Manufacturing o Definition o o Requirements o o 4 The process of ensuring a design can be consistently manufactured by the designated supply chain with a minimum number of defects An understanding of best practices (what fails during manufacturing?) An understanding of the limitations of the supply chain (you can’t make a silk purse out of a sow’s ear) DfM Failures o DfM is often overlooked in the design process for some of the following reasons: o o o o 5 Design team often has poor insight into supply chain (reverse auction, anyone?) OEM requests no feedback on DfM from supply chain DfM feedback consists of standard rule checks (no insight) DfM activities at the OEM are not standardized or distributed Why DfM? o o DfM is a proven, cost-effective strategic methodology. Early effective cross functional involvement: o o o o o 6 Reduces overall product development time (less changes, spins, problem solving) Results in a smoother production launch. Speeds time to market. Reduces overall costs. o Designed right the first time. o Optimizes # of parts o Optimizes # of process steps and use of correct, efficient steps o Reduces labor costs to repair and resolve issues o Improves overall production efficiency. o Build right the first time = less rework, scrap, and warranty costs. Improved quality and reliability results in: o Higher customer satisfaction. o Reduced warranty costs. A Basic DfM Checklist o Baseline o o o Bare Board o o o o o o o Trace width and spacings Laminate material Symmetry of stackup Complexity of via connections Incorporation of new materials (embedded passives) Single-sided vs. double-sided System o o 7 Your design matches their capabilities (75% ‘sweet spot’) Design is transferable Blind connections Z dimension limitations o Assembly o o o o o o o o o o Elimination of hand soldering or wave soldering when possible Proximity of components to flex points Component spacing Size of components and complexity of packaging Orientation of components to wave solder Shadowing during wave solder Appropriate dimensions and spacings for PTHs and bond pads Attachment methods Moisture sensitivity level (MSL) Cleanliness Common Types of DfM Review Processes o Informal “Gut Check” Review o o o o Formal Design reviews o o o Internal team External experts Automated (electronic) design automation (ADA) software o o Performed by highly experienced engineers. Difficult with transition to original design manufacturers (ODM) in developing countries. “Tribal knowledge” Modules automate DfM rule checking. Electronic manufacturing service (EMS) providers o 8 Perform DfM as a service Design for Manufacturing (DfM) o Formal DfM Reviews and Tools Sometimes Overlooked o o o o DfM Reviews Needs to be Performed for: o o o o o Organization may lack specialized expertise. More design organizations completely insulated/disassociated from manufacturing. Dependence on local experience. Bare Board Circuit Board Assemblies Chassis/Housing Integration Packaging System Assembly DfM Needs to be conducted in conjunction with the actual electronic assembly source. o 9 What is good DfM for one supplier and one set of assembly equipment may not be good for another. DfM Statistics o o o 10 60% of overall product cost is determined by decisions made early in the design process 75% of manufacturing cost is determined by design drawings and specifications 70 – 80% of all products’ defects are directly related to design issues Use a Root Cause Problem Solving Methodology o 11 It is critical that your organization has a formal root cause problem solving methodology used both internally and externally. This is the best way to incorporate relevant material into your customized Design for Manufacturing and Sourcing guidelines. DfM Example (Plated Through Hole vs. Microvia) o o What should be the minimum diameter of a PTH in your design? What should be the maximum aspect ratio (PCB Thickness / PTH Diameter)? o When should you switch to microvias? o Answer: Depends! o o 12 Supplier Reliability needs PTH Diameter o Data from 26 board shops o o o Medium to high complexity 62 to 125 mil thick 6 to 24 layer Courtesy of CAT o Results o o Yield loss after worst-case assembly Six simulated Pb-free reflows Yield loss can results in escapes to the customer! 13 Are Microvias more reliable than PTHs? o o Depends!! Quality o o o o o Reliability o 14 Some fabricators have no problems Some have more problems with microvias Some have more problems with PTHs Some have problems with both A well-built microvia is more robust than a well-built PTH Courtesy of CAT PTH vs. Microvia PTH Quality Microvia Quality 15 Summary (PTH and Microvias) o The capability of the PCB industry in regards to hole diameter tends to segment o o o o If 8 mil drill diameter or less is required o o o 16 Very high yield (>13.5 mil) High yield (10 – 13.5 mil) Lower yield (< 10 mil) Consider using PCQR2 to identify a capable supplier Consider using interconnect stress test (IST) coupons to ensure quality for each build Consider transitioning to microvias (6 mil diameter) DfM Examples (cont.) o Utilize thermal reliefs on all copper planes when practical o o o Reduces thermal transfer rate between PTH and copper plane Allows for easier solder joint formation during solder (especially for Pb-free) Allows for better hole fill PTH Laminate Copper Plane Copper Spoke Courtesy of D. Canfield (Excalibur Manufacturing) 17 Component Selection Component Robustness 18 Robustness - Components o Concerns o o o Drivers o o o Initial observations of deformed or damaged components Failure of component manufacturers to update specifications Components of particular interest o o o o 19 Potential for latent defects after exposure to Pb-free reflow temperatures 215°C - 220°C peak → 240°C - 260°C peak Aluminum electrolytic capacitors Ceramic chip capacitors Surface mount connectors Specialty components (RF, optoelectronic, etc.) 19 Component Robustness Example: Electrolytic Capacitors Thru-hole electrolytic capacitors are not suitable for SMT and are not designed to handle reflow temperatures V-Chip is an adaptation of electrolytic capacitors to surface mount technology specifically designed to handle the high temperatures. Can they withstand the higher temperatures associated with Pb-free reflow? 20 20 Electrolytic Capacitors Primary electrolytic capacitor failure mode during Pb-free transition? o o Overheating during rework of microprocessor Drivers o o o o Electrolytic capacitors adjacent to the microprocessor Through-hole electrolytic capacitors have lower boiling point than surface-mount electrolytic capacitors Poorly controlled rework conditions (rework temps can reach 300C for over 5 seconds) Example of off-line processes being a critical source of failures o 21 Ceramic Capacitors: Thermal Shock Cracks o Due to excessive change in temperature o o o NAMICS AVX Maximum tensile stress occurs near end of termination o o o Reflow, cleaning, wave solder, rework Inability of capacitor to relieve stresses during transient conditions. Determined through transient thermal analyses Model results validated through sectioning of ceramic capacitors exposed to thermal shock conditions Three manifestations o o o 22 Visually detectable (rare) Electrically detectable Microcrack (worst-case) 22 Thermal Shock Crack: Visually Detectable AVX 23 23 Thermal Shock Crack: Micro Crack o o Variations in voltage or temperature will drive crack propagation Induces a different failure mode o 24 DfR Increase in electrical resistance or decrease capacitance 24 Corrective Actions in the Manufacturing Process o Solder reflow o o o o o o Wave soldering o o Maintain belt speeds to a maximum of 1.2 to 1.5 meters/minute Touch up o 25 Room temperature to preheat (max 2-3oC/sec) Preheat to at least 150oC Preheat to maximum temperature (max 4-5oC/sec) Cooling (max 2-3oC/sec) o In conflict with profile from J-STD-020C (6oC/sec) Make sure assembly is less than 60oC before cleaning Eliminate 25 Corrective Actions in the Design Process o o Orient terminations parallel to wave solder Avoid certain dimensions and materials for wave soldering o o o o o o Provide adequate spacing from hand soldering operations Use manufacturer’s recommended bond pad dimensions or smaller (critical for wave soldering) o 26 Maximum case size for SnPb: 1210 Maximum case size for SAC305: 0805 Maximum thickness: 1.2 mm C0G, X7R preferred Smaller bond pads reduce rate of thermal transfer 26 Flex Cracking of Ceramic Caps o o Due to excessive flexure of the board Occurrence o o o o 27 Depaneling Handling (i.e., placement into a test jig) Insertion (i.e., mounting insertion-mount connectors or daughter cards) Attachment of board to other structures (plates, covers, heatsinks, etc.) Flex Cracking (Case Studies) 28 Board Depaneling Screw Attachment Connector Insertion Heatsink Attachment Flex Cracking (cont.) 29 Flex Cracking (cont.) o Drivers o o o o Solutions o o o o o o 30 Distance from flex point Orientation Length (most common at 1206 and above; observed in 0603) Avoid case sizes greater than 1206 Maintain 30-60 mil spacing from flex point Reorient parallel to flex point Replace with Flexicap (Syfer) or Soft Termination (AVX) Reduce bond pad width to 80 to 100% of capacitor width Measure board-level strain (maintain below 750 microstrain, below 500 microstrain preferred for Pb-free) Summary o Risk areas o o o o Small volume V-chip electrolytic capacitors Through hole electrolyic capacitors near large BGAs Ceramic capacitors wave soldered or touched up Actions o Spec and confirm o o o o 31 Peak reflow temperature requirements for SMT electrolytics (consider elimination if volume < 100mm3) Time at 300°C for through-hole electrolytics Initiate visual inspection of all SMT electrolytic capacitors (no risk of latency if no bulging or other damage observed) Ban touch up of ceramic capacitors (rework OK) Peak Temperature Ratings o o AKA: ‘Temperature Sensitivity Level’ (TSL) Some component manufacturers are not certifying their components to a peak temperature of 260ºC o o Why lower than 260ºC? o o 32 260ºC is industry default for ‘worst-case’ peak Pb-free reflow temperature Industry specification Technology/Packaging limitation 32 Industry Specification (J-STD-020) o Package size o o o Number of component manufacturers rely on table and reflow profile suggested in J-STD-020C Larger package size, lower peak temperature Issues as to specifying dwell time o o 33 J-STD-020C: Within 5ºC of 260ºC for 20-40 seconds Manufacturers: At 260ºC for 5-10 seconds 33 J-STD-020D.1 Reflow Profile (Update) o Specification of peak package body temperature (Tp) o o o Users must not exceed Tp Suppliers must be equal to or exceed Tp Not yet widely adopted 34 34 TSL (cont.) o Limited examples of technology and package limitations o o o o Surface mount connectors (primarily overcome) RF devices (already sensitive to SnPb reflow) Opto-electronic (LEDs, optoisolators, etc.) B. Willis, SMART Group Examples o o Amphenol: “Amphenol connectors containing LEDs must NOT be processed using Lead-free infra-red reflow soldering using JEDEC-020C (or similar) profiles” Micron / Aptina: “Some Pb-free CMOS imaging products are limited to 235°C MAX peak temperature” http://download.micron.com/pdf/technotes/tn_00_15.pdf http://www.amphenolcanada.com/ProductSearch/GeneralInfo/Disclaimer%20for%20Connectors%20containing%20LEDs.htm 35 35 Moisture Sensitivity Level (MSL) o Popcorning controlled through moisture sensitivity levels (MSL) o o Defined by IPC/JEDEC documents J-STD-020D.1 and J-STD-033B Higher profile in the industry due to transition to Pb-free and more aggressive packaging o o o 36 Higher die/package ratios Multiple die (i.e., stacked die) Larger components 36 MSL: Typical Issues and Action Items o Identify your maximum MSL o o o o Cogiscan Not all datasheets list MSL o o Driven by contract manufacturer (CM) capability and OEM risk aversion Majority limit between MSL3 and MSL4 (survey of the MSD Council of SMTA, 2004) High volume, low mix: tends towards MSL4 Low volume, high mix: tends towards MSL3 Can be buried in reference or quality documents Ensure that listed MSL conforms to latest version of JSTD-020 37 37 MSL Issues and Actions (cont.) o o Most ‘standard’ components have a maximum MSL 3 Components with MSL 4 and higher o o o o o Large ball grid array (BGA) packages Encapsulated magnetic components (chokes, transformers, etc.) Optical components (transmitters, transceivers, sensors, etc.) Modules (DC-DC converters, GPS, etc.) MSL classification scheme in J-STD-020D is only relevant to SMT packages with integrated circuits o o 38 Does not cover passives (IPC-9503) or wave soldering (JESD22A111) If not defined by component manufacturer, requires additional characterization 38 Aluminum and Tantalum Polymer Capacitors Aluminum Polymer Capacitor Tantalum Polymer Capacitor 39 Popcorning in Tantalum/Polymer Capacitors o Pb-free reflow is hotter o o o Approach to labeling can be inconsistent o o o o o Aluminum Polymer are rated MSL 3 for eutectic (could be higher for Pb-free) Sensitive conductive-polymer technology may prevent extensive changes Solutions o o 40 Aluminum Polymer are rated MSL 3 (SnPb) Tantalum Polymer are stored in moisture proof bags (no MSL rating) Approach to Tantalum is inconsistent (some packaged with dessicant; some not) Material issues o o Increased susceptibility to popcorning Tantalum/polymer capacitors are the primary risk Confirm Pb-free MSL on incoming plastic encapsulated capacitors (PECs) More rigorous inspection of PECs during initial build 40 Component Summary o Know when peak temperature indicates true temperature sensitivity o o o o Consider requiring MSL on the BOM for certain component packaging and technologies o 41 Component manufacturer’s peak temperature ratings deviate from J-STD-020 Peak temperature ratings are very specific or nuanced in some fashion Ask component manufacturer for data confirming issues at temperatures below 260C Focus on polymeric and large tantalum capacitors Printed Circuit Boards Robustness Concerns Cracking and Delamination Trace Peeling Vias/PTH Laminate Selection 42 Printed Board Robustness Concerns Increased Warpage Solder Mask Discoloration Pad Cratering Blistering Delamination Land Separation 43 PTH Cracks 43 Printed Board Damage o Predicting printed board damage can be difficult o o o o o o 44 Driven by size (larger boards tend to experience higher temperatures) Driven by thickness (thicker boards experience more thermal stress) Driven by material (lower Tg tends to be more susceptible) Driven by design (higher density, higher aspect ratios) Driven by number of reflows No universally accepted industry model 44 Printed Board Damage: Industry Response o Concerns with printed board damage have almost entirely been addressed through material changes or process modifications o o 45 Not aware of any OEMs initiating design rules or restrictions Specific actions driven by board size and peak temperature requirements Industry Response (cont.) o Small, very thin boards o o o o Medium, thin boards o o o o Up to 10 x 14 and 75 mil thick Tend to have moderate-sized components; limits peak temperatures to 245ºC-248ºC Rigorous effort to upgrade laminate materials (dicy-cured may not be feasible) Large, thick boards o o o 46 Up to 4 x 6 and 62 mil thick Peak temperatures as low as 238ºC Minimal changes; most already using 150ºC Tg Dicy (tends to be sufficient) Up to 18 x 24 and 180 mil thick Difficulty in maintaining peak temperatures below 260ºC Very concerned Rothshild, APEX 2007 PCB Robustness: Laminate Material Selection Board thickness IR-240~250 ≤60mil Tg140 Dicy All HF materials OK 60~73mil Tg150 Dicy NP150, TU622-5 All HF materials OK 73~93mil Tg170 Dicy, NP150G-HF HF –middle and high Tg materials OK Board thickness ≤ 60mil 60~73mil IR-260 Tg150 Dicy HF- middle and high Tg materials OK Tg170 Dicy HF –middle and high Tg materials OK 73~93mil Tg150 Phenolic + Filler IS400, IT150M, TU722-5, GA150 HF –middle and high Tg materials OK 93~130mil Phenolic Tg170 IS410, IT180, PLC-FR-370 Turbo, TU7227 HF –middle and high Tg materials OK 93~120mil Tg150 Phenolic + Filler IS400, IT150M, TU722-5 Tg 150 HF –middle and high Tg materials OK 121~160mil Phenolic Tg170 IS410, IT180, PLC-FR-370 Turbo TU722-7 HF –high Tg materials OK ≧131mil Phenolic Tg170 + Filler IS415, 370 HR, 370 MOD, N4000-11 HF –high Tg materials OK PhenolicTg170 + Filler IS415, 370 HR, 370 MOD, N4000-11 HF material - TBD ≧161mil TBD – Consult Engineering for specific design review ≧161mil 1.Copper thickness = 2OZ use material listed on column 260 thickness >= 3OZ use Phenolic base material or High Tg Halogen free materials only 3.Twice lamination product use Phenolic material or High Tg Halogen free materials only (includes HDI) 4.Follow customer requirement if customer has his own material requirement 5.DE people have to confirm the IR reflow Temperature profile 2.Copper 47 J. Beers, Gold Circuits 47 Printed Board Damage: Prevention o Thermal properties of laminate material are primarily defined by four parameters o o o o o Each parameter captures a different material behavior o 48 Out of plane coefficient of thermal expansion (Z-CTE) Glass transition temperature (Tg) Time to delamination (T260, T280, T288) Temperature of decomposition (Td) Higher number slash sheets (> 100) within IPC-4101 define these parameters to specific material categories Thermal Parameters of Laminate o Out of plane CTE (below Tg or Z-axis: 50ºC to 260ºC) o o o Glass transition temperature (IPC-TM-650, ) o o o o o o Characterizes interfacial adhesion T-260 for SnPb is 5-10 minutes Pb-free: T-280 of 5-10 minutes or T-288 of 3-6 minutes Temperature of decomposition (IPC-TM-650, 2.3.40) o o o 49 Characterizes complex material transformation (increase in CTE, decrease in modulus) Tg of 110ºC to 170ºC for SnPb Pb-free: 150ºC to 190ºC Time to delamination (IPC-TM-650, 2.4.24.1) o o CTE for SnPb is 50ppm - 90ppm (50C to 260C rarely considered) Pb-free: 30ppm - 65ppm or 2.5 – 3.5% Characterizes breakdown of epoxy material Td of 300ºC for SnPb Pb-free: Td of 320ºC PCB Robustness: Material Selection o The appropriate material selection is driven by the failure mechanism one is trying to prevent o o o 50 Cracking and delamination Plated through fatigue Conductive anodic filament formation PCB Delamination o o o 51 Fiber/resin interface delamination occurs as a result of stresses generated under thermal cycling due to a large CTE mismatch between the glass fiber and the epoxy resin (1 vs. 12 ppm/ºC) Delamination can be prevented/resisted by selecting resin with lower CTE’s and optimizing the glass surface finish. Studies have shown that the bond between fiber and resin is strongly dependent upon the fiber finish 51 Delamination / Cracking: Observations o Morphology and location of the cracking and delamination can vary o o Even within the same board Failure morphology and locations o o o 52 Within the middle and edge of the PCB Within prepregs and/or laminate Within the weave, along the weave, or at the copper/epoxy interface (adhesive and cohesive) Additional Observations o Drivers o o o o o o o Controlled depth drilling Extensive debate about root-cause o o o 53 Sequential Lamination Limited information o o Higher peak temperatures Increasing PCB thickness Decreasing via-to-via pitch Increasing foil thickness (1-oz to 2-oz) Presence of internal pads Sequential lamination Non-optimized process Intrinsic limit to PCB capability Moisture absorption Rothschild, IPC APEX 2007 Delamination / Cracking: Root-Cause o Non-Optimized Process o o o Limit to PCB Capability o o o 54 Some PCB suppliers have demonstrated improvement through modifications to lamination process or oxide chemistry Some observations of lot-to-lot variability Difficult to overcome adhesion vs. thermal performance tradeoff (dicy vs. phenolic) High stresses developed during Pb-free exceed material strength of standard board material Moisture Absorption Cracking and Moisture Absorption o Does moisture play a role? o No o o o o Yes o o o o o o 55 DfR found delamination primarily around the edge and away from PTH sites after MSL testing IBM found minimal differences after a 24 hr bake of coupons with heavy copper (>2 oz) Delamination / cracking observed in board stored for short (<2 weeks) periods of time DfR customer found improvement after 48 hrs at 125C A number of companies now require 5 – 24 hour bake before reflow IBM found improvement with coupons with nominal copper DfR observed more rapid degradation of boards exposed to moisture, even after multiple reflows Some customers specifying maximum moisture absorption Where does the moisture come from? Cracking and Moisture (cont.) o o Storage of prepregs and laminates Drilling process o o o o 56 Moisture is absorbed by the side walls (microcracks?) Trapped after plating Storage of PCBs at PCB manufacturer Storage of PCBs at CCA manufacturer PCB Trace Peeling o Delamination of trace from surface of the board o Sources of increased stress o o o o Sources of decreased strength o o 57 Excessive temperatures during high temperature processes Insufficient curing of resin Insufficient curing of solder mask Improper preparation of copper foil Excessive undercut 57 Plated Through Holes (PTH) o Voids o o Can cause large stress concentrations, resulting in crack initiation. The location of the voids can provide crucial information in identifying the defective process o o o o o Etch pits o o o 58 Around the glass bundles In the area of the resin At the inner layer interconnects (aka, wedge voids) Center or edges of the PTH Due to either insufficient tin resist deposition or improper outer-layer etching process and rework. Cause large stress concentrations locally, increasing likelihood of crack initiation Large etch pits can result in a electrical open 58 Plated Through Holes (PTH) Spring-Loaded Pins o Overstress cracking o o o o Fatigue o o o 59 CTE mismatch places PTH in compression Pressure applied during "bed-of-nails" can compress PTH In-circuit testing (ICT) rarely performed at operating temperatures Circumferential cracking of the copper plating that forms the PTH wall Driven by differential expansion between the copper plating (~17 ppm) and the out-ofplane CTE of the printed board (~70 ppm) Industry-accepted failure model: IPC-TR-579 59 PCB Robustness: Qualifying Printed Boards o o o o 60 This activity may provide greatest return on investment Use appropriate number of reflows or wave o In-circuit testing (ICT) combined with construction analysis (cracks can be latent defect) o 6X Solder Float (at 288C) may not be directly applicable Note: higher Tg / phenolic is not necessarily better o Lower adhesion to copper (greater likelihood of delamination) o Greater risk of drilling issues o Potential for pad cratering Higher reflow and wave solder temperatures may induce solder mask delamination o Especially for marginal materials and processes o More aggressive flux formulations may also play a role o Need to re-emphasize IPC SM-840 qualification procedures 60 Material Selection - Laminate o Higher reflow and wave solder temperatures may induce delamination o o 61 Especially for marginal materials and processes o Specify your laminate by name – not type or “equivalent” Role of proper packaging and storage o PCBs should remain in sealed packaging until assembly o Reseal partially opened bricks o Package PCBs in brick counts which closely emulate run quantities o PCBs should be stored in temperature and humidity controlled conditions o Bake when needed o Packaging in MBB (moisture barrier bags) with HIC (humidity indicator cards) may be needed for some laminates PCB Robustness Strain Flexure Issues & Pad Cratering Electro-Chemical Migration (ECM) Cleanliness 62 Design for Manufacturability & Process Review o Depaneling Process o o 63 63 Look at how panel is supported during the process so that it is never allowed to “dangle” or flex Vulnerable BGA and ceramic components along the PCB edge Emerson Confidential Strain & Flexure: Pad Cratering o Cracking initiating within the laminate during a dynamic mechanical event o In circuit testing (ICT), board depanelization, connector insertion, shock and vibration, etc. G. Shade, Intel (2006) 64 6464 SAC Solder is More Vulnerable to Strain Tensile force on pad and Laminate Sources of strain can be ICT, stuffing through-hole components, shipping/handling, mounting to a chassis, or shock events. NEMI study showed SAC is more Sensitive to bend stress. LF Laminate Load Bearing Capability LF limit PbSn PbSn limit PCB deflection Oneway Analysis of Load (kN) By Solder Alloy 0.5 0.45 Load (kN) 0.4 0.35 0.3 0.25 0.2 0.15 0.1 SAC Sn-Pb Solder Alloy Each Pair Student's t 0.05 Means and Std Deviations Level SAC Sn-Pb 65 65 Number Mean Std Dev Std Err Mean Lower 95% 18 0.230859 0.056591 18 0.416101 0.040408 0.01334 0.00952 0.20272 0.39601 Upper 95% 0.25900 0.43620 Pad Cratering o Drivers o o o o o Finer pitch components More brittle laminates Stiffer solders (SAC vs. SnPb) Presence of a large heat sink Difficult to detect using standard procedures o 66 Intel (2006) X-ray, dye-n-pry, ball shear, and ball pull 6666 ICT Strain: Fixture & Process Analysis o o o o 67 67 Review/perform ICT strain evaluation at fixture mfg and in process: 500 us, IPC 9701 and 9704 specs, critical for QFN, CSP, and BGA http://www.rematek.com/download_center/board_stress_analysis.pdf To reduce the pressures exerted on a PCB, the first and simplest solution is to reduce the probes forces, when this is possible. Secondly, the positioning of the fingers/stoppers must be optimized to control the probe forces. But this is often very difficult to achieve. Mechanically, the stoppers must be located exactly under the pressure fingers to avoid the creation of shear points Solutions to Pad Cratering o Board Redesign o o Solder mask defined vs. non-solder mask defined Limitations on board flexure o o More compliant solder o o SAC305 is relatively rigid, SAC105 and SNC are possible alternatives New acceptance criteria for laminate materials o o 68 500 microstrain max, Component, location, and PCB thickness dependent Intel-led industry effort Attempting to characterize laminate material using high-speed ball pull and shear testing, Results inconclusive to-date 6868 Laminate Acceptance Criteria o Intel-led industry effort o o o Alternative approach o 69 Attempting to characterize laminate material using highspeed ball pull and shear testing Results inconclusive to-date Require reporting of fracture toughness and elastic modulus Electro-Chemical Migration: Overview Insidious failure mechanism o Self-healing: leads to large number of no-trouble-found (NTF) o Can occur at nominal voltages (5 V) and room conditions (25C, 60%RH) o elapsed time 12 sec. Due to the presence of contaminants on the surface of the board o Strongest drivers are halides (chlorides and bromides) o Weak organic acids (WOAs) and polyglycols can also lead to drops in the surface insulation resistance o Primarily controlled through controls on cleanliness o Minimal differentiation between existing Pb-free solders, SAC and SnCu, and SnPb o Other Pb-free alloys may be more susceptible (e.g., SnZn) o 70 70 Cleanliness Analysis & Failure Analysis o o o Cleanliness Measurement Techniques Failure Analysis Techniques/Descriptions Components of Concern 71 71 Cleanliness Measurement Techniques Test Name Acronym Method Description Surface Insulation Resistance SIR IPC-TM-650, 2.6.3.3 Performed on test article, >1E8 Ω after min 168 hrs, standard comb pattern [8 more test methods identified by DfR] Ion Chromatography IC IPC-TM-650, 2.3.28 Heat sample in 80˚C, 75/25 IPA/H20 solution, 1 hr, [column specified by TM? AS11 column for anion analysis and a CS12A column for cation analysis used on GSFC project]. No established accept/reject standard. Resistance of Solvent Extract ROSE IPC-TM-650, 2.3.25 Pass 75/25 IPA/H20 solution over both sides of finished PWA, measure resistivity of solution, >2E6 Ω-cm NASA-STD-8739.2, para 11.7 Tests cleaning bath using automated equipment and a salt-equivalency standard, <1.55 µg/cm2 (<10 µg/in2) IPC-TM-650, 2.6.14.1 Performed on a test article, 10V, 65˚C/88.5% RH, 596 hrs, IRfinal must not degrade by more than a decade from IRinitial, no filament growth reducing electrode spacing by >20%, no corrosion Sodium Chloride Salt Equivalent Ionic Contamination (Omega Meter) Electrochemical Migration Technique ROSE EM Equivalency Factor 1 Omega-Meter ~1.5 Ion-Chromatography ~4.0 72 Source: PCBA Cleanliness Guidelines, C. Hillman, http://www.dfrsolutions.com/uploads/webcasts/PCBA_Cleanliness/in dex.htm Equivalency factor in last row confirmed by Trace Laboratories in white paper Solvent Extraction Matrix Selection and its Potential Affects on Cleanliness Test Results, K. Sellers, J. Radman, via testing. Weak Organic Acid Detection o o o o ROSE and Omega-Meter tests DO NOT detect WOAs (weak organic acids). Successfully passing these “cleanliness” tests does not ensure cleanliness. Why? o “Bulk” testing best used for process equipment monitoring o ROSE has insufficient fidelity1/ o IPA reduces solubility of water soluble WOAs (more testing is planned) 1/ ROSE and Omega-Meter are suitable for bare PCB cleanliness testing and for finding halide residues. [note: some halides will be built into the board by design or by low quality and cannot be removed with cleaning by the user, they will be released at soldering temperatures] Ion Chromatography (IC) is only test that finds and quantifies WOAs o No uniform/standard accept/reject limits WOAs change approach to cleanliness assurance: o item-level testing (screening) is not available o emphasis falls to production line monitoring o method of monitoring is time consuming and involves additional expense o Lot jeopardy may be larger due to longer time between quality monitor data sets 1/ Solvent Extraction Matrix Selection and its Potential Affects on Cleanliness Test Results, K. Sellers, J. Radman, Trace Laboratories 73 STI Washed 1/ DfR2/ Chloride <6 <2 Nitrite <3 <2-4 Sulfate <3 Bromide <10 <10 Nitrate <3 <2-4 Phosphate <3 Anions Acetate <3 Formate <3 MSA, Adipic, Succinic (total) <25 GE2/ DoD2/ IPC2/ ACI2/ “Medical”3/ (90/10 DI/IPA) <2 <3.5 <6.1 <6.1 <10 All units in μg of ion per in2 <10 <10 <7.8 <7.8 <3 <4 <15 <6 <4 <4 <175 Weak Organic Acids Foresite <150 Users are establishing their own pass/fail limits while no standard exists <30 <4 <4 <2 No obvious trend for WOA acceptance limit Cations May be seeing mixtures of absolute Max limits and control limits Lithium <3 Sodium <3 Ammoniu m <3 <4 Potassium <3 <4 74 1/ Analytical Techniques to Identify Unexpected Contaminants On Electronic Assemblies, K. Freeman, STI Electronics 2/ PCBA Cleanliness Guidelines, C. Hillman, http://www.dfrsolutions.com/uploads/webcasts/PCBA_Cleanliness/index.htm 3/ Solvent Extraction Matrix Selection and its Potential Affects on Cleanliness Test Results, K. Sellers, J. Radman, Trace Laboratories <4 Reduce & Control Cleanliness Concerns o Incoming PCB Cleanliness o o Consider cleanliness requirements in terms of IC (ion chromatography) test for PCBs using WS flux o o o o Cleanliness testing performed using ROSE (resistivity of solvent extracted) or Omega-Meter method (ionic cleanliness, NaCl equivalent) Don’t use ROSE or Omegameter test as single option (at all? Risk from dirty IPA) Inspection method with accept/reject limit Sampling criteria Control cleanliness throughout the process from start to finish. 75 Recommendations – Process Qualification o o 76 Validate compatibility of all new process materials using SIR testing. Continue spot check testing of cleanliness using ion chromatography under low profile SMT parts QFN, CSP & Low Profile Cleanliness Issues o Low or no standoff parts are particularly vulnerable to cleanliness / residual flux problems o o o 77 77 Difficult to clean under Short paths from lead to lead or lead to via Can result in leakage resistance, shorts, corrosion, electromigration, dendritic growth Cleanliness: Dendritic Growth o o Large area, multi-I/O and low standoff can trap flux under the QFN Processes using no-clean flux should be requalified o o Those processes not using no-clean flux will likely experience dendritic growth without modification of cleaning process o o o 78 78 Particular configuration could result in weak organic acid concentrations above maximum (150 – 200 ug/in2) Changes in water temperature Changes in saponifier Changes to impingement jets Soldering 79 Reflow Profile Optimization - 4 Main Criteria o Preheating Phase - Ramp & Soak vs. Straight Ramp preheating profiles o Ramp & Soak (soak period just below liquidus), more common, more forgiving. o o Allow flux solvents to fully evaporate and activate to deoxidize the surfaces to be soldered. Allows temperature equalization across the entire assembly. Consistent soldering and reduces tomb stoning. However, If too long, flux may be consumed resulting in excessive oxidation. Flux my be come volatile producing solder balls or voiding defects. o o o o Straight Line is faster and causes less thermal damage to materials o o Peak Temperature and Time at (above) Liquidus (TAL) A balance between being hot enough for long enough to achieve good consistent solder wetting and bonding for proper joint formation, across the entire assembly. o Yet as quickly as possible to prevent thermal damage to the components and board and to prevent excessive copper dissolution and excessive intermetallic growth. Cooling Rate of SnAgCu effects the Microstructure & Bulk Intermetallics o Faster cooling rates produce a finer, stronger microstructure and limits intermetallics but is riskier for low standoff height components Overall Time (Costs & Efficiency) o Over all throughput is determined the board size/complexity and the oven's heat transfer capabilities. o o o But more susceptible to defect and quality variation, does not work well on complex assemblies. 80 Example: Incomplete Hole Fill o Poor solder hole fill can cause lead to solder joint crack failures. Can be caused by: o o o o 81 Insufficient top side heating prevented solder from wicking up into PTH Barrel Insufficient flux or flux activity for the surface finish in use Lack of thermal relief for large copper planes PCB hole wall integrity issues – voids, plating, contamination Soldering Copper Dissolution Mixed Assembly 82 Solders: Copper Dissolution The reduction or elimination of surface copper conductors due to repeated exposure to Sn-based solders Bath, iNEMI Significant concern for industries that perform extensive rework o o o Telecom, military, avionics ENIG Plating 60 sec. exposure 274ºC solder fountain 83 83 Solders: Copper Dissolution (cont.) o o PTH knee is the point of greatest plating reduction Primarily a rework/repair issue o o Already having a detrimental effect o 84 Celestica identified significant risk with >1X rework Major OEM unable to repair ball grid arrays (BGAs) S. Zweigart, Solectron 84 Copper Dissolution (Contact Time) Contact time is the major driver o o o Some indications of a 25-30 second limit Preheat and pot temp. seem to have a lesser effect Optimum conditions (for SAC) o o o o 85 Contact time (max): 47 sec. (cumulative) Preheat temperature: 140-150°C Pot temperature: 260-265°C A Study of Copper Dissolution During Pb-Free PTH Rework Using a Thermally Massive Test Vehicle , C. Hamilton (May 2007) Dissolution: Copper vs. Nickel Albrecht, SMTA 2006 o Nickel (Ni) plating has a dissolution rate approximately 1/10th of copper (Cu) plating o 86 Albrecht, SMTA 2006 Given similar solder temperatures and contact times 86 Solutions to Cu Dissolution o o o Option 1: restriction on rework o Number of reworks or contact time Option 2: solder material o Indications that SNC can decrease dissolution rates o Reduced diffusion rate through Sn-Ni-Cu intermetallics Option 3: board plating o Some considering ENIG o Some considering SNC HASL A Study of Copper Dissolution During Pb-Free PTH Rework Using a Thermally Massive Test Vehicle , C. Hamilton (May 2007) 87 87 Mixed Assembly o o Primarily refers to Pb-free BGAs assembled using SnPb eutectic solder paste Why? o o 88 UIC Area array devices (e.g., ball grid array, chip scale package) with eutectic solder balls are becoming obsolete Military, avionics, telecommunications, industrial do not want to transition to Pb-free…yet 88 SnPb BGAs and the Component Industry Prismark, iNEMI SnPb-Compatible BGA Workshop (IPC/APEX 2007) For certain device types, HiRel dominates market share o o Mil/Aero is ~10% of Hi-Rel Hi-Rel products tend to be of higher value o o 89 Greater profit for part suppliers 89 Mixed Assembly: Reflow o o Initial studies focused on peak temperature Identified melt temperature of solder ball as critical parameter o o o Recommendations o o o 90 217°C for SAC305 Ensured ball collapse and intermixing Minimum peak reflow temperature of 220°C Reflow temperatures below 220°C may result in poor assembly yields and/or inadequate interconnect reliability For increased margin, >225 to 245°C peak 90 Mixed Assembly: Solder Joint Morphology Motorola 91 91 Mixed Assembly: Peak Temp Statements o Cisco Systems: o o o o o 245°C Minimum time above liquidus (TAL) of 80 seconds Need to watch for voiding o 92 > 217°C 215 - 230°C 220°C peak used in exceptional circumstances 230°C peak recommended IBM: o o Formation of SnPbAg phase (Tm = 179°C) may allow for lower reflow temperatures Intel: Infineon: o > 210°C Talk to your paste supplier 92 Mixed Assembly: Time Above Liquidus o 93 Effect is inconclusive Kinyanjui, Sanmina-SCI, iNEMI SnPb-Compatible BGA Workshop (IPC/APEX 2007) 93 Mixed Assembly: Solder Paste Volume Kinyanjui, Sanmina-SCI, iNEMI SnPb-Compatible BGA Workshop (IPC/APEX 2007) Moderate solder paste volume Large solder paste volume o Some conflict o o o o Sanmina claims no effect Celestica claims significant effect Other factors may play a greater role Additional investigation necessary 94 Snugovsky, Celestica (2005) 94 Mixed Assembly: Effect of Pitch o Intel: reduced self alignment o o Degree of difficulty: 0.5mm > 0.8mm > 1 - 1.27mm pitch component Sanmina: improved mixing Kinyanjui, Sanmina-SCI, iNEMI SnPb-Compatible BGA Workshop (IPC/APEX 2007) 95 95 Mixed Assembly: Temp Cycling Results HP: 0 to 100ºC, 214ºC Peak Temp 99 Cumulative Failure (%) SnPb 30 SnAgCu/SnPb 3 SnAgCu/SnAgCu 0.3 0.03 10 100 1,000 8,000 Cycles to Failure 96 96 Mixed Assembly (Other) o iNEMI recently reported issues with low silver (Ag) Pb-free alloys o o High pasty range creates voiding and shrinkage cracks o 97 SAC105, SAC0307, etc. Mixed assembly with low-silver SAC is not recommended Mixed Assembly: Conclusions o A potentially lower risk than complete transition to Pb-free o o The preferred approach for some high reliability manufacturers (military, telecom): o 98 Important note: more studies on vibration and shock performance should be performed Acceptance of mixed assembly could be driven by GEIASTD-0005-1 98 Mixed Assembly: Alternatives o Other options on dealing with Pb-free BGAs other than mixing with SnPb o o Two flux options o o o Application of Pb-free solder paste Application of flux preform Two soldering options o o 99 Placement post-reflow Hot air (manual) Laser soldering (automatic) 99 Design for Sourcing 100 Design for Sourcing (DfS) o o o 101 Supply Chain Failures New Process Technology and Product Development Methodology New Technology: Supply Chain Failures o Failure in experimental design o o Failure to properly pre-condition o o o No attempt to understand how the new technology could fail and adjust qualification procedures accordingly Testing not performed after reflow Most component testing not performed after exposure to all realistic manufacturing stresses Failure to use appropriate samples o 102 Must be representative of realistic worst-case (materials, manufacturing, use) 102 10 Failures of Inadequate Testing o Failure to monitor relevant behavior o o o Failure of testing o o o 103 E.g., leakage currents not monitored during temperature / humidity / bias (THB) testing o Assumed a particular failure mechanism (Kirkendall voiding, which induces a voltage drop) Functional tests not performed in-situ THB testing not performed o Interfered with launch date o Not aware of new compound Failures during integrity testing not always communicated to customers o Strong impetus to report zero failures Changes in materials not always communicated to the customer 103 10 New Product Development Gate 1 Market Research Idea Generation Gate 2 Concept Feasibility Idea Submission o o 104 Gate 3 Gate 4 Concept Design Development & & Project Development Planning Project Charter Business Plan Simultaneously optimize the design in 4 areas Start Design for Sourcing and Design for Manufacturing early Gate 5 Ramp Up Update Plan & AR Gate 6 Launch & Production Start-Up Final Check Production Process Audit Functional Performance Design for Reliability Design for Manufacture Design for Sourcing Why Emphasize DfS? o o o One of the most common design issues Cannot assure reliability unless robust and controlled manufacturing processes are in place Design for Sourcing is a “must” on new products o o 105 Complete specifications and supplier qualification ensure a smooth manufacturing start up Provides flexibility to change suppliers Design for Sourcing Identify CTQs Specify Tolerances Assess Supplier Capability Change Design or Supplier 106 Obtain Cost Estimate Ongoing Learning Opportunities o Some ideas for low cost continuing DfM education inside and outside of your company o o o o 107 E-Learning at dfrsolutions.com Organize “Your Company Days”, Poster Sessions, Demos Use internal electronic bulletin boards an resources Brown Bags &” Lunch and Learns” from your internal gurus and from your suppliers o PCB o Contract Manufacturers o Component Suppliers o Electronics Materials - paste, fluxes, cleaners Summary & Recap o o DfM is a proven, cost-effective strategic methodology. Early, effective cross functional involvement: o o o o o 108 Reduces overall product development time (less changes, spins, problem solving) Results in a smoother production launch Speeds time to market Reduces overall costs o Designed right the first time o Optimizes # of parts o Optimizes # of process steps and use of correct, efficient steps o Reduces labor costs to repair and resolve issues o Improves overall production efficiency o Build right the first time = less rework, scrap, and warranty costs Improves quality and reliability results in: o Higher customer satisfaction o Reduced warranty costs Contact Information o Questions: o o o 109 Contact Cheryl Tulkoff, ctulkoff@dfrsolutions.com, 512-913-8624 askdfr@dfrsolutions.com www.dfrsolutions.com PCB Supply Chain Best Practices 110 PCBs as Critical Components o 111 PCBs should be considered critical components or a critical commodity. Without stringent controls in place for PCB supplier selection, qualification, and management, long term product quality and reliability is simply not achievable. This section will cover some common best practices and recommendations for management of your PCB suppliers. PCB Best Practices: Commodity Team o Existence of a PCB Commodity Team with at least one representative from each of the following areas: o o o o o 112 Design Manufacturing Purchasing Quality/Reliability The team should meet on a minimum monthly basis to discuss new products and technology requirements in the development pipeline. Pricing, delivery, and quality performance issues with approved PCB suppliers should also be reviewed. The team is also tasked with identifying new suppliers and creating supplier selection and monitoring criteria. PCB Best Practices: Selection Criteria o Established PCB supplier selection criteria in place. The criteria should be unique to your business, but some generally used criteria are: o o o o o o o o o o 113 Time in business Revenue Growth Employee Turnover Training Program Certified to the standards you require (IPC, MIL-SPEC, ISO, etc.) Capable of producing the technology you need as part of their mainstream capabilities (don’t exist in their process “niches” where they claim capability but have less than ~ 15% of their volume built there.) Have quality and problem solving methodologies in place Have a technology roadmap Have a continuous improvement program in place PCB Best Practices: Qualification Criteria o Rigorous qualification criteria which includes: o o 114 On site visits by someone knowledgeable in PCB fabrication techniques. An onsite visit to the facility which will produce your PCBs is vital. The site visit is your best opportunity to review process controls, quality monitoring and analytical techniques, storage and handling practices and conformance to generally acceptable manufacturing practices. It is also the best way to meet and establish relationships with the people responsible for manufacturing your product. Sample builds of an actual part you will produce which are evaluated by the PCB supplier and that are also independently evaluated by you or a representative to the standards that you require. PCB Best Practices: Supplier Tiering o Use of supplier tiering (Low, Middle, High ) strategies if you have a diverse product line with products that range from simpler to complex. This allows for strategic tailoring to save cost and to maximize supplier quality to your product design. Match supplier qualifications to the complexity of your product. Typical criteria for tiering suppliers include: o o o o o o o 115 Finest line width Finest conductor spacing, Smallest drilled hole and via size Impedance control requirment Specialty laminate needed (Rogers, flex, mixed) Use of HDI, micro vias, blind or buried vias. Minimize use of suppliers who have to outsource critical areas of construction. Again, do not exist in the margins of their process capabilities PCB Best Practices: Relationship Mgt. o Relationship Management. Ideally, you choose a strategy that allows you to partner with your PCB suppliers for success. This is especially critical is you have low volumes, low spend, or high technology and reliability requirements for your PCBs. Some good practices include: o o o 116 Monthly conference calls with your PCB commodity team and each PCB supplier. The PCB supplier team should members equivalent to your team members. QBRs (quarterly business reviews) which review spend, quality, and performance metrics, and also include “state of the business updates” which address any known changes like factory expansion, move, or relocation, critical staffing changes, new equipment/capability installation etc. The sharing is done from both sides with you sharing any data which you think would help strengthen the business relationship – business growth, new product and quoting opportunities, etc. At least twice per year, the QBRs should be joint onsite meetings which alternate between your site and the supplier factory site. The factory supplier site QBR visit can double as the annual on site visit and audit that you perform. Semi-Annual “Lunch and Learns” or technical presentations performed onsite at your facility by your supplier. All suppliers perform education and outreach on their processes and capabilities. They can educate your technical community on PCB design for manufacturing, quality, reliability, and low cost factors. They can also educate your technical community on pitfalls, defects, and newly available technology. This is usually performed free of charge to you. They’ll often spring for free lunch for attendees as well in order to encourage attendance. PCB Best Practices: Supplier Scorecards o Supplier Scorecards are in place and performed quarterly and yearly on a rolling basis. Typical metrics include: o o o o o o 117 On Time Delivery PPM Defect Rates Communication – speed, accuracy, channels, responsiveness to quotes Quality Excursions / Root Cause Corrective Action Process Resolution SCARs (Supplier Corrective Action Requests) Reporting Discussion of any recalls, notifications, scrap events exceeding a certain dollar amount PCB Best Practices: Cont. Quality Monitoring o Continuous Quality Monitoring is in place. Consider requiring and reviewing the following: o o o o o Top 3 PCB factory defects monitoring and reporting Process control and improvement plans for the top 3 defects Yield and scrap reporting for your products Feedback on issues facing the industry Reliability testing performed (HATS, IST, solder float, etc.) o o 118 As a starting point, review the IPC-9151B, Printed Board Process Capability, Quality, and Relative Reliability (PCQR2) Benchmark Test Standard and Database at: http://www.ipc.org/html/IPC-9151B.pdf Your PCB suppliers may be part of this activity already. Ask if they participate and if you can get a copy of their results. PCB Best Practices: Prototype Development o Prototype Development o 119 In an ideal environment, all of your PCBs for a given product should come from the same factory from start to finish – prototype (feasibility), pre-release production (testability & reliability), to released production (manufacturability). Each factory move introduces an element of risk since the product must go through setup and optimization specific to the factory and equipment contained there. While this is not always possible for prototypes, all PCBs intended for quality and reliability testing should come from the actual PCB production facility. Disclaimer & Confidentiality o o o ANALYSIS INFORMATION This report may include results obtained through analysis performed by DfR Solutions’ Sherlock software. This comprehensive tool is capable of identifying design flaws and predicting product performance. For more information, please contact DfRSales@dfrsolutions.com. DISCLAIMER DfR represents that a reasonable effort has been made to ensure the accuracy and reliability of the information within this report. However, DfR Solutions makes no warranty, both express and implied, concerning the content of this report, including, but not limited to the existence of any latent or patent defects, merchantability, and/or fitness for a particular use. DfR will not be liable for loss of use, revenue, profit, or any special, incidental, or consequential damages arising out of, connected with, or resulting from, the information presented within this report. CONFIDENTIALITY The information contained in this document is considered to be proprietary to DfR Solutions and the appropriate recipient. Dissemination of this information, in whole or in part, without the prior written authorization of DfR Solutions, is strictly prohibited. From all of us at DfR Solutions, we would like to thank you for choosing us as your partner in quality and reliability assurance. We encourage you to visit our website for information on a wide variety of topics. Best Regards, Dr. Craig Hillman, CEO 120