Integrated Magnetic Filter Transformer Design for Grid Connected

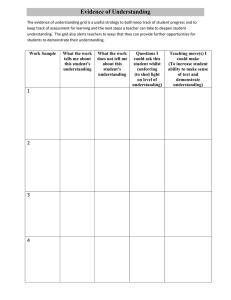

advertisement