IEEE

advertisement

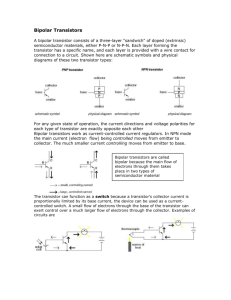

IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 50, NO. 3, MARCH 2003 645 Transistor Design and Application Considerations for >200-GHz SiGe HBTs Greg Freeman, Senior Member, IEEE, Basanth Jagannathan, Member, IEEE, Shwu-Jen Jeng, Jae-Sung Rieh, Member, IEEE, Andreas D. Stricker, David C. Ahlgren, and Seshadri Subbanna, Member, IEEE Invited Paper Abstract—SiGe HBT transistors achieving over 200 GHz and MAX are demonstrated in this paper. Techniques and trends in SiGe HBT design are discussed. Processing techniques available to silicon technologies are utilized to minimize parasitic resistances and capacitances and thereby establish raw speeds exceeding III–V devices despite the higher mobility in those materials. Higher current densities and greater avalanche currents, which are required for establishing such high performance, are discussed as they relate to device self-heating and reliability and the degradation of the devices. Simple circuit results are shown, demonstrating 4.2-ps ring-oscillator delays. Index Terms—BiCMOS integrated circuits, bipolar transistors, heterojunctions, semiconductor devices. I. INTRODUCTION B IPOLAR transistors have historically attained faster transit times compared to silicon FET transistors. This is in part because, compared to FET transistors, the bipolar transistor relies on vertical layer dimensions rather than leading edge lithographic dimensions to attain its speed performance. Vertical transit time from the emitter, through the base, and to the neutral collector is determined largely by the thickness of the base layer and base-collector space-charge regions and not by lithography. A further favorable factor in transistor design is that the structural flexibility available to the designer in constructing the transistor (especially in silicon technologies) provides degrees of freedom in minimizing the parasitic access resistances and parasitic capacitances. This speed advantage, together with transconductance noise, and (i.e., current drive), high self-gain, low matching/reproducibility, continue to make the bipolar transistor the device of choice for many demanding applications. Forty-gigabit/s applications are now being produced utilizing of SiGe bipolar and BiCMOS production technologies with 120 GHz. At the same time, near-production 0.13- m CMOS of approximately 90 GHz are used to technologies with figure produce 10-Gb/s applications. The similarity of the of merit and, at the same time, the factor of four difference in Manuscript received May 28, 2002; revised October 3, 2002. The review of this paper was arranged by Editor J. D. Cressler. The authors are with the IBM Microelectronics Semiconductor Research and Development Center, Hopewell Junction, NY 12533 USA (e-mail: freemang@us.ibm.com). Digital Object Identifier 10.1109/TED.2003.810467 Fig. 1. f versus I for different generations of SiGe HBT. Near twice-minimum emitter areas are shown for each technology at 1 m , 0.26 m , and 0.18 m from bottom to top. application-speed illustrates the strength of the bipolar transistor. Other applications, such as high-speed test equipment and high-frequency radar systems also take advantage of the highest speed transistors. The high-speed performance may also be traded for lower versus current comparison for power. Shown in Fig. 1 is an three different transistor generations: a 0.5- m 47-GHz SiGe HBT, a 0.18- m 120-GHz SiGe HBT, and a 0.12- m 210-GHz SiGe HBT. With the lateral and vertical scaling to be discussed in this paper, each successive transistor has higher performance at the same current compared to the one below in the chart. Applications not requiring the higher performance of each successive transistor may instead operate the transistor at a lower current. As one can see from the chart, a 2 higher frequency may be traded for approximately a 10 reduction in power dissipation at the same performance. Further, an alternate transistor may be designed with reduced collector doping only, to achieve a similar low current , but at a more favorable collector–base capacitance and breakdown. With the recent demonstration of SiGe transistors operating and [1], it is interesting to at greater than 200 GHz take note that SiGe HBT speeds are now surpassing the best 0018-9383/03$17.00 © 2003 IEEE 646 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 50, NO. 3, MARCH 2003 production III–V HBTs [2], [3]. The possibility to design the very high-performance bipolar device on the same chip as high performance CMOS and with it, the large menu of passive elements including resistors, capacitors, inductors, varactors, and low-loss transmission lines opens up numerous possibilities that are not attainable in III–V technologies. For instance, the high-performance optical networking parts, in addition to containing the very high-speed functional blocks served well by the high-speed bipolar transistors, also have a need for de-skew logic, self-test, and forward error correction. These elements may be implemented with a low-power solution in a relatively small amount of CMOS logic, but would be prohibitive to implement in bipolar transistors. Lower speed analog elements more favorable to implementation in CMOS, such as op-amps and quadrature voltage-controlled oscillators (VCOs) are also possible. Further, the on-chip digital CMOS supports the trend to integrate more and more of the framer logic onto the same chip as the high-speed physical layer portions. By having available the wide range of devices in BiCMOS technologies on a single chip, system architectures have greater flexibility, and power hungry and signal degenerating off-chip connections are avoided. Also important is that complex design system discontinuities are avoided as is required to design systems in multiple chips. The capability to combine the high-speed bipolar with the CMOS will be a strong motivator to implement in silicon technologies wherever possible. Obtaining such high performance with a silicon bipolar transistor does not come without breaking some perceived barriers. For instance, the well-known “Johnson limit” predicts that silicon (also SiGe) bipolar transistors will be limited to an product of 200 GHz V [3]. This of course predicts a of below 1 V for 200-GHz transistors, yet this is now products exceeding being routinely broken with values for over 350 GHz-V [1], [5], [6]. Still, typical transistors are less than 2 V, and this has caused 100 GHz some concerns to designers whose load lines extend beyond this value of collector–emitter voltage. Higher current densities compared to prior generations of silicon bipolar transistor also have caused some concern. Although in each transistor generation transistor dimensions shrink while the current density increases (see, for example, Fig. 1), it has been found that transistor parameter degradation can be exacerbated by this current density. In this paper, we first describe SiGe HBT transistor design, covering critical attributes essential to producing greater than and . In the process, we compare to 200 GHz in both both other published SiGe HBT results and InP HBT results. We then discuss such application-related issues as just described, addressing the viability of over 200-GHz transistors in applica, and retions swinging collector–emitter voltages over liable operation of these transistors at high current density. We then describe some ring-oscillator results demonstrating record stage delays. II. TRANSISTOR DESIGN In high-speed transistor design, it is beneficial to decouple optimization from the task of base resistance and the task of Fig. 2. Scaling the SiGe HBT involves reducing the base width, increasing the Ge ramp, and increasing the collector concentration. Simultaneous structural are also changes to improve in R and R and minimize increase in C required for highest performance. collector–base capacitance reduction. The former requires attention to the vertical profile, while the latter is a task of creating a transistor structure that minimizes the parasitic elements optiand at the same time, does not negatively influence the mization covered in the former task. The benefit not only holds in a method to describe the elements of design, but also in the transistor development procedures, as was done with development of the transistor reported here (see sequential reports [7] and [1]). In this section, we compare our 200-GHz transistor design to our 120-GHz transistor design, to illustrate the significant modifications to prior state-of-the-art. A. Vertical Profile Design improvement is achieved through improvement in each in the well-established of the delay components, related to relation where itance, and are emitter–base and base-collector capacand are collector and emitter resistance, and are neutral base and base-collector space charge layer width, respectively, is Boltzmann’s constant, is temperais ture, is the unit electron charge, is field factor, and the electron saturation velocity. (base transit time) and The transit time elements (base-collector space-charge layer transit time) are reduced through vertical dimension minimization and Ge profile optimization. The base film is deposited through a low-temperature UHVCVD, incorporating a thin boron layer with a graded Ge concentration. As shown in Fig. 2, a thinner as-deposited FREEMAN et al.: TRANSISTOR DESIGN AND APPLICATION CONSIDERATIONS FOR (a) 200-GHz SiGe HBTs 647 (b) 3 Fig. 3. f versus (a) J (b) and f versus linear current (=J W ) for 0.12 2.5 and 0.2 6.4 m transistors. Note that the plot on the right is relevant to the metal system, which provides similar current per unit transistor length for both transistors. 2 2 boron results in a smaller base width after processing and base broadening by diffusion, and the graded Ge profile results in an accelerating field for electrons across the base, both of component of delay. which have a strong effect on the Carbon is incorporated within the base layer during growth in order to minimize undesirable boron widening in subsequent high-temperature process steps [8], [9]. Improvement of involves reducing the base-collector space-charge layer width, and this is accomplished by increasing the collector doping transistor, we concentration. Compared to our 120-GHz term by 37% to have been able to reduce the 0.48 ps. Increasing the collector concentration has additional performance enhancing benefits. First, it enables the transistor to operate at higher currents (pushing out the Kirk effect) and thus term of the above relaminimizing the tion. Second, together with reduction in emitter resistance and minimization of collector epitaxy thickness, it reduces the access resistance portion of the delay relation . The key difficulty in increasing the collector dose is that it component as well. Significant improveincreases the ments incorporating increased collector dose thus must go hand in hand with structural or layout modifications, such is not increased substantially with increased dose. that Layout improvements, such as reduced emitter and collector implant (pedestal) dimensions, have limited effect due to the perimeter components of capacitance. Structural and process are modifications that reduce the extrinsic portions of performance in SiGe essential to achieving the highest HBTs, and these will be the topic of the next section. Self-heating and metal interconnect current capability are key considerations in creating a reliable transistor and dictate that, with increased current density in the transistor, a more narrow emitter stripe width is required. Shown in Fig. 3 is a comparison scale and of the two technologies on both a current density on a current scale, defined as the product of the current density and the emitter stripe width . The value approx- Fig. 4. Estimated ECL delay components for the 120- and 210-GHz technologies. Leftmost bars are the portion from transistor transit times . The remaining four are the R C delay components, where C is the weighted capacitance charged through the associated resistance. 3 imates the current through a unit width of metal, corresponding to a unit length of the emitter. Design guidelines specify a maximum current per unit metal width for reliable operation. Maintaining a similar value between generations is required to maintain reliable operation of the metal system, and thus the more scale. important comparison is on the B. Transistor Structure Improvements Delay in a circuit is not well predicted by the transistor paalone and is a function of the device parasitic acrameter cess resistances and parasitic capacitances as well. We have utilized the method described in [10] and [11] to estimate the delay components in an ECL circuit as shown graphically in Fig. 4. delays, This shows the transit-time related delay and the is the load resistor, is the base resistance, where the collector resistance, and the emitter resistance. , , , and , are the total weighted capacitances to be charged through the load, base, collector, and emitter resistances according to this technique. The comparison between the 120-GHz technology and the 210-GHz technology in this chart is illustrative of several important observations. First, the with the asso120-GHz technology is largely limited by ciated capacitances. These components have been greatly improved moving to the 210-GHz device, yet remain as significant delay limiters. Note that, even though the base resistance is a strong limiting resistance in the device, it does not influence figure of merit. Improvement in this key parameter will the be discussed shortly. figure of merit attempts to be As is well known, the more relevant to capture such RC delays as highlighted in the above analysis. Reduction in base resistance, without sacrificing or , is the critical challenge. It is interesting to compare generations of technology in these key parameters. With genervalues, ations of technology represented by their respective and versus the technology we plot in Fig. 5 the 648 Fig. 5. Unit length C and R versus f . C increases only slightly despite the higher dose required between generations. R decreases between generations to improve circuit speed. Also note that the R and C for the 210-GHz SiGe transistor are comparable to the best reported InP (nontransferred substrate) devices [1], [3], [12]–[17]. for several published technologies. Note that in this plot, is decreased between generations, and remains relatively constant despite the increased collector dose required to achieve values. the higher Also shown in this plot are InP HBT published results. Contrasting the mesa structures of InP technology, where the base sheet resistance is low, yet limited extrinsic base resistance lowbetween ering options are available, results in similar total is lower in InP the material systems. Similarly, unit area technologies, yet it is uniform over the total area under the device. This compares to silicon bipolar devices where the capacitance is dominated by the patterned pedestal implant under a small portion of the total device. The lowest InP points in the chart are not apparent to be production devices, due to the substantial shrink and dependence on small features of wet etches to achieve such low numbers. Structure flexibility in silicon processing appears to have matched or overcome the material advantages of InP transistors. For the 210-GHz device shown here, these low values for and result in an value of 285 GHz (extracted from Mason’s unilateral power gain). Such values are achieved through a new self-aligned raised extrinsic base structure, which has substantial benefits beyond other common structures. One common structure, where the extrinsic base is implanted into the SiGe epitaxy layer, is represented in the 120-GHz device used for reference in this paper. This is also utilized in technologies from other companies [5]. Another common structure is characterized by selective epitaxy following an opening in a low-resistance extrinsic base polysilicon film [6], [14], [12]. Both these structures appear to have limiting issues as will be described here. We have found that, in the implanted extrinsic base structure, and are both limited by the implant and that cannot easily be decoupled from the extrinsic base construction. The implanted extrinsic base structure is shown in Fig. 6(a). This figure depicts two key issues found in this structure. First, the depth of the implant is necessarily deeper than the intrinsic region, and thus the collector pedestal will intersect this and col- IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 50, NO. 3, MARCH 2003 Fig. 6. (a) Implanted extrinsic base device structure. (b) Raised extrinsic base structure. lector–base capacitance is increased. A shallower implant or for lower .A further lateral distance trades off higher second factor is the implant damage and the effect this has on the intrinsic region of the device. Implant damage creates silicon interstitials which migrate to the base region of the device and create excess diffusion, increasing base transit time, and reducing . Thus, the implanted extrinsic base has a wide influence on a variety of parameters and thus limits are found to and . achievable Similarly, the selective epitaxy approach has its limitations. As described in [18] and [19], the growth and link-up of the selective film on the underside of the extrinsic base polysilicon presents issues. First, growth defects such as twins and silicon dislocations are found in close proximity to the device and the collector–base junction, and this causes emitter–base and collector–base leakage issues. Second, the thickness of the epitaxy intrinsic layer put down prior to boron layer growth is constrained, since this also grows on the underside of the extrinsic base polysilicon. A thicker film will make link-up between the extrinsic polysilicon and the selective epitaxy film more difficult. Distance to the emitter and extra thermal processing may be required to minimize the effects. Thus, the base resistance optimization. minimization is not decoupled from the The raised extrinsic base structure utilized on the 210-GHz device described here contains a raised base that is deposited after the SiGe epitaxy film, and is self-aligned to the emitter. This is illustrated in Fig. 6(b). Because there is no implant into resulting from the SiGe epitaxy film, there is little impact on proximity of the extrinsic base to the emitter. In addition, because the extrinsic base diffuses into the SiGe film only a small amount, the base side of collector–base junction is the same as is minimized. Comthe intrinsic base dopant. In this way, pared to the selective epitaxy processes, the SiGe epitaxy film is deposited across the entire wafer, and most importantly, the active device and junctions are contained in a film that is influenced strictly by growth on single crystal. The linkage between the raised extrinsic base and the intrinsic base film occurs over a larger distance. These various factors are significant to make the next step in silicon bipolar improvements. FREEMAN et al.: TRANSISTOR DESIGN AND APPLICATION CONSIDERATIONS FOR Fig. 7. (a) Gummel and (b) output characteristics for a 0.12 m 207-GHz f device. 2 2.5 m 200-GHz SiGe HBTs 649 Fig. 8. (a) f and f versus collector current and Mason’s unilateral gain (U) and (b) maximum stable and maximum available gain (MSG/MAG) versus frequency at peak bias. C. Device Results The devices reported here have pinched-base sheet resistance of 1.7 V, of 2.5 k /sq, a peak dc current gain of 400, of 5.5 V. Shown in Fig. 7 are dc characteristics for and an NPN with 0.12 2.5 m emitter area. The Gummel characteristic shows a collector current ideality of 1.02 and a base current ideality of 1.15. The negative slope in the output characteristics reflects self-heating in the device, which is discussed in more detail in a later section and in [20]. On-wafer high-frequency measurements up to 110 GHz were performed. Measured pad parasitics were de-embedded at every frequency point using on-chip open-short calibration. Fig. 8 and (both U and MAG) for shows room temperature of 1 V. a device with a 0.12 2.5 m size emitter at a in excess of 200 GHz is seen for a current density range of 8.3–16.5 mA/ m (linear current of 1.0–1.98 mA/ m), in excess of 270 GHz is achieved peaking at 207 GHz. from the 20 dB/dec extrapolation of Mason’s unilateral power gain (U) at 40 GHz for the same current range with a peak value extrapolation from maximum of 285 GHz. Alternatively, available gain (MAG) in the 50–80-GHz range of frequencies values of 194 GHz. The actual values results in peak for power gain at various discrete frequencies of interest are to understand perhaps more practical than extrapolated the real-world performance potential of a device. Fig. 8 also illustrates both U and MAG versus frequency for the 0.12 2.5 m device, revealing values for U and MAG at 40 GHz of 17.0 and 15.9 dB, respectively. These values advance the SiGe HBT state of the art by 4-5 dB compared to previously reported figures in the range of 160–170 GHz [14], [5]. The gain data exhibit a 20 dB/dec slope in U between 20–60 GHz and of 50 a 23 dB/dec slope in MAG between 50–80 GHz. and of 4.2 fF is obtained from measured -parameters on this same device. Small device performance is key to achieving large transistor counts on a single chip with reasonable overall power dissipation. Fig. 9 shows ac characteristics for a small device (0.12 0.5 m at 1 V . A peak of 180 GHz is obtained Fig. 9. (a) f and f versus collector current for a small device (0.12 m 0.5 m), with (b) measured h power gain versus frequency at peak bias. 2 at 800- A current. For applications requiring bias with equivtechnology (e.g., 40 Gb/s netalent gain as the 120-GHz at a much lower curworking), this device provides such an rent of 175 A, which is a 78% decrease from the prior gencharacteristics are well beeration. As shown in Fig. 9, haved at 20 dB/dec roll-off, yet measurements on such small devices are problematic in obtaining accurate U, shown for refbias. From these measurements erence in Fig. 9(b) at peak and for and comparison of the product of extracted both large and small devices, we estimate this smallest device to values equal to or greater than the longer devices. have Some transistor designs, utilizing for instance low base dopant concentration or nonmanufacturable dimensions or overlay requirements, may achieve high performance yet not have sufficient robustness to achieve the same performance over normal process variations. The design should be robust enough to ensure device performance in the limits when process 650 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 50, NO. 3, MARCH 2003 Fig. 11. f and f Fig. 10. R f and f = 3500 /sq. versus pinched-base sheet resistance R . across a wafer and with different emitter widths. parameters drift, resulting in unintentional modifications to dopant diffusion, layer thickness, or lithography dimensions. The design described thus far utilizes high base dopant concentration and, as will be shown, such a doping level ensures ) and minimal variation in neutral base width (and hence avoids punch-through concerns even for relatively high values . Additionally, the design takes into account the tolerof ances of the emitter–base junction depth and collector–base depletion width, resulting in a well-controlled collector current to the first order is affected by and . The tolerance of and distributions. Process variations in are acthe counted for by understanding the tolerances of its intrinsic and extrinsic components. The intrinsic component depends on the intrinsic base doping and the definition of the emitter dimension. The emitter dimension and its separation from the extrinsic base are defined by standard CMOS processes and thus well-controlled dimension variations are ensured. In addition, because is of the high base doping, the intrinsic portion of the total is further insensitive to the emitter width. small and thus Formation of the raised extrinsic base with a shallow junction depth and minimal TED results in a tight distribution of the and . Furthermore, the extrinsic component of both raised extrinsic base scheme minimizes the effects of variable and unwanted slower perimeter component of device operation by minimizing the perimeter base diffusion effects and controlling the counterdoping of the emitter at the perimeter. and dependence Shown in Figs. 10 and 11 are the , reon emitter width and pinched-base sheet resistance spectively, for a set of wafers run to explore these dependencies. is slightly different from that reported The nominal value of above due to slight process differences. Fig. 10 shows relatively and , where the variation is tight distribution in largely due to uncertainties in the unilateral gain due to meawith surement variability. Approximately 5% change in 33% larger emitters is observed, and this is due to an increase from the larger area device. Extracted appears to be in similar between emitter widths. Further, we show process tolerance as a function of nominal pinched-base sheet resistance design points through simulation. values with high pinched-base sheet One can obtain high Fig. 12. Influence on I and R with variations in base and emitter concentrations for device designs of nominal 4 and 20 K /sq. resistance (low base doping and narrow base widths), yet device sensitivity to process variations is sacrificed. Numerical simulations [21] were employed to compare device sensitivities with nominal pinched-base resistance of 4 and 20 K /sq. For values, the base and boron doses corresponding to such emitter dopant concentrations were varied 20% and 20%, representing expected process variations. Such variations result values and in device parameter variations as in different well. Shown in Fig. 12 is a plot of the collector current for these individual process variations as a function of the value. Simultaneous variations in process parameters will result in greater variations in transistor properties. From this plot, it is observed that sensitivities to process variation become subdesign point. Greater base stantially greater at the higher design point rewidth sensitivity exhibited in the higher as shown, but also in , early sults in variations not only in , making the lower design point prevoltage, and ferred for a manufacturable process. III. APPLICATION ISSUES The high-performance SiGe HBT described in this paper has value and a higher current density as coma reduced pared to prior generations of slower devices. The devices devalues of approximately half scribed here demonstrate FREEMAN et al.: TRANSISTOR DESIGN AND APPLICATION CONSIDERATIONS FOR that of the 50-GHz devices of prior generation and seven times the current density of the same generation. This section addresses concerns relating to such trends necessary to achieve the higher performance, and shows that designs utilizing higher and higher current denperformance devices with lower sity are possible and that the device degradation under such conditions is well within acceptable specifications. 200-GHz SiGe HBTs 651 TABLE I ESTIMATED JUNCTION TEMPERATURE RISE AT PEAK f BIAS CURRENT AND V = 1:5 V FOR VARIOUS 150–200-GHz HBT TECHNOLOGIES, WITH DEVICE SIZES CHOSEN FOR THE SAME 6-mA PEAK I [20], [25] A. Current Density High current density causes concern in two areas: 1) device parameter degradation with long-term operation and 2) HBT device self-heating and impact on degradation and long-term reliability. While these effects are related, since the latter influences the former, the high current (without the heat) directly influences device degradation and may be viewed separately. Relative to current-induced device degradation, many concerns appear to come from the experience with III–V devices where high current density has historically caused severe device degradation and sudden collapse of gain. The observed mechanism has been the migration of dopant atoms in the crystal lattice of the base film, with movement of the dopant atom beyond the heterojunction causing catastrophic effects [22]. One can easily understand that this effect does not occur in silicon and silicon-germanium systems since the bonding energy of silicon systems is so much greater than III–V systems. This is observed in the difference in diffusion constants of dopants and in the practical fact that silicon systems must achieve 900 C temperatures for significant diffusion to occur, compared to maximum allowable temperatures of 400 C–500 C for III–V systems. Degradation mechanisms observed for silicon systems in forward bias are quite different, and appear to relate to hydrogen trapping and detrapping in the polysilicon to single crystal interfacial region as a function of current density. As reported in [23], [24], this effect results principally in an ideal base current shift. Effects on collector current appear to be observed principally at higher currents where emitter resistance shifts are observed. Degradation in devices stressed at peak current densities of 8 mA/ m has been detailed in [24], with junction temperatures tested up to 235 C, and extrapolations to over 10 h with acceptable degradation. With careful attention to engineering the polysilicon/single-crystal interface, the degradation can be minimized as current densities are increased. Similar device stress results are currently under investigation for the 200-GHz transistors described here. High current densities are also responsible for heating of the device. The heating of the device will translate to the metal system, where a higher temperature will cause earlier failure of the metal interconnect above the device. Table I compares self-heating approximations across different 150–200-GHz technologies. Namely, the SiGe HBT device described here is compared to the reported self-heating characteristics of InP HBTs [25]. Since thermal resistance in InP devices is a strong function of the collector design, with InGaAs collectors or subcollectors inhibiting heat dissipation compared to InP collectors, both types of devices are shown. In this comparison, we normalize to an operating current for a mA, since normalized thermal dissipation transistor, at 2 Fig. 13. Comparison of temperature rise for the 0.12 2.5 m SiGe HBT transistor and 1 3 m InGaAs collector InP HBT transistors presented in [25]. Of the two InP transistors, the higher f values result from reduced parasitics from improved lithography overlay and smaller base mesa structure. 2 - m varies with device size. The InP thermal resistance values are comparable to those reported in [26]–[28]. Note that although the typical operation current densities between material systems are very different to achieve peak , the thermal resistance of an InP device with the InGaAs collector is very high and results in very large self-heating. In Fig. 13, the results for this type of collector design are shown from [25] compared to the 200-GHz SiGe HBT self-heating characteristics. The all-InP collector design results in compavalues from rable self-heating at peak to the SiGe HBT, yet production transistors with InP collector are approximately 20% lower than in the SiGe HBT reported in this paper. For the SiGe transistor, the principle engineering solution to the increasing current density is to narrow the emitter stripe width inversely with the current density, resulting in a fixed current along the length of the device from one generation to the next. Because of the narrowed width, the device lengthens for a given emitter area or device peak current, and the thermal resistance is reduced. Still, as shown in Fig. 14, the thermal resistance does not scale directly with the stripe width and as a result, a device with higher current density will become hotter operating at peak current compared to a prior generation [20]. Alternate solutions are also feasible. An increase in performance is one alternative, such as shown in Fig. 3, where the 652 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 50, NO. 3, MARCH 2003 Fig. 14. Measured (symbols) and calculated (lines) thermal resistance for various device dimensions. From [20]. improved device operates at lower current densities for comparable performance. This provides the designer the flexibility to use a larger device with lower current density, (and same total current), achieving the same high-frequency gain. Further, careful thermal considerations in circuit design can ensure reliable operation. For this, the designer knows that the backside of the chip is maintained at a certain temperature, and a temperature rise may be determined for each device in the circuit. Utilizing this method and typical backside temperatures of 85 C, one finds that most devices are well under the typically assumed junction temperature of 125 C, corresponding to a 40 C temperature rise due to self-heating and neighboring device effects. Those devices that operate at high bias and peak current (or are tightly packed) require extra attention in design, by spreading the heat into a larger footprint in the device design or through special attention to the metal interconnect (such as strapping metal levels together). Guidance may be provided to the designers from the transistor model, incorporating circuit operating conditions and thermal resistance dependencies on geometry. The self-heating typically incorporated in the model may be used to highlight devices which have become the hottest. Alternatively, graphical methods may be utilized. One graphversus , is instructive to ical method, applied to a plot of define what constraints exist on where a device may be biased. and high region of the plot is the On such a plot, the high region of high self-heating. The typical electromigration guideline of a maximum current as a function of temperature can take into account the self-heating of the device (which is a function of bias) and a solution to the electromigration and self-heating equations may be plotted to define the limit. Such a plot is defined in Fig. 15 for the 200-GHz device design and a copper metal system with parts per trillion failure rates, as well as moderate packing densities. One can observe that, while not all desired biasing options are possible with the metal configuration used to define this set of constraints, the device can nonetheless be operated such that peak performance and reliable operation may be obtained. Note that the limit does not result from the intrinsic device characteristic, but is related to an extrinsic factor, Fig. 15. Bias constraints for the metal system on a simple one-stripe device layout, taking into account self-heating of the device as a function of bias condition and the dependence of the metal system reliability on this device temperature. All data is for 0.12-m-wide emitters, with the length shown in the legend. The load line is for the 0.12 2 m device in the ring-oscillator circuit of Fig. 16. 2 which is the characteristic of the metal interconnect. This implies that the limit can be relaxed with layout modifications. B. Breakdown Even though the Johnson limit of 200 GHz V is now being exvalues of these deceeded by today’s 200-GHz devices, vices remain less than 2 V. Designers thus must face the prospect . It has been of designing load lines that extend beyond is not a fundamental limit pointed out by others that for allowed bias voltage, but that it simply marks the value of where the base current reverses because of avalanche multiplication in the collector–base space-charge region. Instead, have been explored for the practical limits larger than device, and realistic reliability issues have been defined. These are covered in detail in [29]. One practical issue is in the effect of the negative base current on the device bias. Device output conductance is increased because of the avalanche current passing through the internal and external base resistance components, and further turning on the base-emitter junction. This effect may be managed well through careful device modeling, such that the designer is made aware of the effects of the base current. Another issue related to the base current reversal is the device “pinch-in,” where the potential drop resulting from avalanche current flowing out of the device through the internal base resistance, eventually drives the large majority of collector current through the center of the device, resulting in hot-spots during operation. This is apparent at voltages above 3.5 V for the devices described here. Power amplifier designs and modulator drivers routinely limits to achieve high voltage swings break the FREEMAN et al.: TRANSISTOR DESIGN AND APPLICATION CONSIDERATIONS FOR Fig. 16. Stage delay versus collector current (tail current) for ring oscillators fabricated with 0.12- and 0.16-m emitter width (enw) NPN and different load resistors (R ). The inset shows the schematic of a single ECL gate. approaching the device . Power amplifiers utilizing GHz devices with V and roughly achieve voltage swings up to 20 V at a 2-GHz operating frequency [30]. Modulator drivers operating to 40 Gb/s have also been reported, and these demonstrate 2.5–3.5 V peak–peak and 5 V voltage voltage swings, requiring between and , swings on devices with 1.8 and 6.5 V respectively [31], [32]. IV. CIRCUIT RESULTS We describe here record ring-oscillator results of a ring-os-GHz device described cillator fabricated with the earlier. The ring oscillator implemented here is based on a standard ECL topology. A single ECL stage consists of seven NPN transistors, all of which are 0.12 m 2 m in size (see the inset of Fig. 16). The design consists of 14 stages and is fully differential. The tail current (collector current) in the differential pair is set up through a current mirror that generates current proportional to an input voltage. Further, the bias conditions are such that device self-heating is kept below the limits of the metal system (Fig. 15). It is estimated that 1 mA is consumed in the emitter follower of the ECL stage at a 3.6-V nominal supply voltage. ECL stage-to-stage wiring was done in the first level of metal. Fig. 16 compares room-temperature (25 C) stage delay curves for ring oscillators with emitter width (enw) of 0.12 m combinations. For and 0.16 m with various load resistor a 3.6-V supply, minimum delay of 4.3 ps is obtained for rings (as designed) at designed with 0.12- m emitters and 105 a collector current of 2.2 mA. Increasing power supply to 4.0 V reduces the delay further to 4.2 ps. As expected, increasing the load resistor values leads to an increase in delay times. All other aspects of the design remaining the same, increasing the emitter width to 0.16 m leads to a 5% increase in delay times, reduction in larger device which is comparable to the 200-GHz SiGe HBTs 653 Fig. 17. (a) ECL stage delay comparison for ring oscillators fabricated in 90SiGe technologies. (b) Bipolar ring-oscillator stage delay and 285-GHz f as a function of f (unilateral gain) from this work and recently reported data in literature. References A = [34], B = [35], C = [36]. sizes. From -parameter measurements, a increase of 10% results from increasing the emitter width to 0.16 m, and and the rise this contributes to the observed reduction in in delay. ECL ring oscillators were also fabricated in a previous and 90-GHz (unilateral gain) technology 90-GHz 4 m with [33]. This design uses NPN devices sized 0.2 and was biased from a 3.6-V power supply as 100 well. The prior generation NPNs have 2 larger transit time, 2 higher base resistance, 2 higher emitter resistance, 2 higher collector resistance, and 35% lower compared to the 200-GHz NPN devices. Fig. 17(a) compares the ECL delays in the two technologies. Similar to the delay component breakdown shown in Fig. 4, we find that a large portion of the 50% delay reduction is a result of the base resistance improvement. The strong dependence of ring-oscillator delays on NPN parasitics is shown in Fig. 17(b), where stage delay (from unilateral gain) for this work as is plotted against well as recent ECL and CML gate delay data reported in the literature. V. CONCLUSION We have shown that 200-GHz devices can be achieved in SiGe systems and discussed the relevant aspects of device design that are important to achieve high performance, manufacturable devices, and reliable systems. Compared to InP devices, and and, importantly, opthese devices have higher erate at substantially lower temperature rise. In transistor design, minimization of parasitic elements improviding the greatest leverage. proves performance, with Common silicon processing techniques are employed to obtain minimized extrinsic base resistance, and minimal increase in collector–base capacitance. Due to such techniques, we find that silicon transistors can surpass III–V device performance despite 654 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 50, NO. 3, MARCH 2003 the well-known III–V material system benefits, and bring with it the integration benefits well known to silicon technology. [21] J. Johnson, A. Stricker, A. Joseph, and J. Slinkman, “A technology simulation methodology for AC-performance optimization if SiGe HBTs,” in IEDM Tech. Dig., 2001, pp. 489–492. [22] M. Hafizi and M. J. Delaney, “Reliability of InP-based HBT’s and HEMT’s: Experiments, failure mechanisms, and statistics,” in Proc. Int. Conf. InP and Related Materials, 1994, pp. 299–302. [23] M. S. Carroll, A. Neugroschel, and C.-T. Sah, “Degradation of silicon bipolar junction transistors at high forward current densities,” IEEE Trans. Electron Devices, vol. 44, pp. 110–117, Jan. 1997. [24] J.-S. Rieh, K. Watson, F. Guarin, Z. Yang, P.-C. Wang, A. Joseph, G. Freeman, and S. Subbanna, “Wafer level forward current reliability analysis of 120GHz production SiGe HBT’s under accelerated current stress,” in Proc. IEEE Int. Reliability Physics Symp., Apr. 2002, pp. 184–188. [25] S. Thomas, III, J. A. Foschaar, C. H. Fields, M. M. Madhav, M. Sokolich, R. D. Rajavel, and B. Shi, “Effects of device design on InP-based HBT thermal resistance,” IEEE Trans. Device Mater. Reliab., vol. 1, pp. 185–189, 2001. [26] W. Liu, H. F. Chau, and E. Beam, III, “Thermal properties and thermal instabilities of InP-Based heterojunction bipolar transistors,” IEEE Trans. Electron Devices, vol. 43, pp. 388–395, Mar. 1996. [27] S. R. Bahl, N. Moll, V. M. Robbins, H. C. Kuo, B. G. Moser, and G. E. Stillman, “Be diffusion in InGaAs/InP heterojunction bipolar transistors,” IEEE Electron Device Lett., vol. 21, pp. 332–334, July 2000. [28] M. Ray, D. Hill, O. Hartin, K. Johnson, and P. Li, “Thermal impact of InGaAs on InP based HBTs,” in Proc. GaAs IC Conf., 2001, pp. 261–264. [29] M. Rickelt, H. M. Rein, and E. Rose, “Influence of impact-ionization-induced instabilities on the maximum usable output voltage of Si-Bipolar transistors,” IEEE Trans. Electron Devices, vol. 48, pp. 774–783, Apr. 2001. [30] D. R. Greenberg, M. Rivier, P. Girard, E. Bergeault, J. Moniz, D. Ahlgren, G. Freeman, S. Subbanna, S. J. Jeng, K. Stein, D. Nguyen-Ngoc, K. Schonenberg, J. Malinowski, D. Colavito, D. L. Harame, and B. Meyerson, “Large-signal performance of high-BV/sub CEO/ graded epi-base SiGe HBT’s at wireless frequencies,” in IEDM Tech. Dig, 1997, pp. 709–802. [31] R. Schmid, T. F. Meister, M. Rest, and H.-M. Rein, “40 Gbit/s EAM driver IC in SiGe bipolar technology,” Electron. Lett., vol. 34, no. 11, pp. 1095–1097, May 1998. [32] G. Freeman, M. Meghelli, Y. Kwark, S. Zier, A. Rylyakov, M. A. Sorna, T. Tanji, O. Schreiber, K. Walter, J.-S. Rieh, B. Jagannathan, A. Joseph, and S. Subbanna, “40 Gbit/s circuits built from a 120 GHz f SiGe technology,” IEEE J. Solid State Circuits, vol. 37, pp. 1106–1114, Sept., 2002. [33] G. Freeman, D. Ahlgren, D. R. Greenberg, R. Groves, F. Huang, G. Hugo, B. Jagannathan, S. J. Jeng, J. Johnson, K. Schonenberg, K. Stein, R. Volant, and S. Subbanna, “A 0.18 m 90 GHz f SiGe HBT BiCMOS, ASIC-compatible, copper interconnect technology for RF and microwave applications,” in IEDM Tech. Dig., 1999, pp. 569–572. [34] J. Bock, H. Schafer, H. Knapp, D. Zoschg, K. Aufinger, M. Wurzer, S. Boguth, R. Stengl, R. Schreiter, and T. F. Meister, “High-speed SiGe : C bipolar technology,” in IEDM Tech. Dig., 2001, pp. 344–347. [35] E. Ohue, R. Hayarni, K. Oda, H. Shimarnoto, and K. Washio, “5.3-ps ECL and 71-GHz static frequency divider in self-aligned SEG SiGe HBT,” in Proc. BCTM, 2001, pp. 26–29. [36] M. Sokolich, A. R. Kramer, Y. K. Boegeman, and R. R. Martinez, “Demonstration of sub-5 ps CML ring oscillator gate delay with reduced parasitic AlInAs/InGaAs HBT,” IEEE Electron Device Lett., vol. 22, pp. 309–311, 2001. REFERENCES [1] B. Jagannathan, M. Khater, F. Pagette, J.-S. Rieh, D. Angell, H. Chen, J. Florkey, F. Golan, D. R. Greenberg, R. Groves, S. J. Jeng, J. Johnson, E. Mengistu, K. T. Schonenberg, C. M. Schnabel, P. Smith, A. Stricker, D. Ahlgren, G. Freeman, K. Stein, and S. Subbanna, “Self-aligned SiGe and 207GHz f in a manufacNPN transistors with 285GHz f turable technology,” IEEE Electron Device Lett., vol. 23, pp. 258–260, May 2002. [2] W. E. Stanchina, M. Sokolich, and K. R. Elliott, “Process and integration technologies for InP ICs,” in Int. Conf. on Indium Phosphide and Related Materials, 2001, pp. 489–492. [3] D. Sawdai, E. Kaneshiro, A. Gutierrez-Aitken, P. C. Grossman, K. Sato, W. Kim, G. Leslie, J. Eldredge, T. Block, P. Chin, L. Tran, A. K. Oki, and D. C. Streit, “High performance, high yield InP DHBT production process for 40 Gb/s applications,” in Proc. Int. Conf. Indium Phosphide and Related Materials, 2001, pp. 493–496. [4] E. O. Johnson, “Physical limitations on frequency and power parameters of transistors,” RCA Rev., vol. 26, pp. 163–177, June 1965. [5] M. Racanelli, K. Schuegraf, A. Kalburge, A. Kar-Roy, B. Shen, C. Hu, D. Chapek, D. Howard, D. Quon, F. Wang, G. U’ren, L. Lao, H. Tu, J. Zheng, J. Zhang, K. Bel, K. Yin, P. Joshi, S. Akhtar, S. Vo, T. Lee, W. Shi, and P. Kempf, “Ultra high speed SiGe NPN for advanced BiCMOS technology,” in IEDM Tech. Dig., 2001, pp. 336–338. [6] K. Oda, E. Ohue, I. Suzumura, R. Hayami, A. Kodama, H. Shimamoto, and K. Washio, “Self-aligned selective-epitaxial-growth Ge C HBT technology featuring 170-GHz f ,” in Si IEDM Tech. Dig., 2001, pp. 332–335. [7] S. J. Jeng, B. Jagannathan, J.-S. Rieh, J. Johnson, K. T. Schonenberg, D. Greenberg, A. Stricker, H. Chen, M. Khater, D. Ahlgren, G. Freeman, K. Stein, and S. Subbanna, “A 210 GHz f SiGe heterojunction bipolar transistor with a nonself-aligned (NSA) structure,” IEEE Electron Device Lett., vol. 22, pp. 542–544, 2001. [8] L. D. Lanzerotti, J. Sturm, E. Stach, R. Hull, T. Buyuklimanli, and C. Magee, “Suppression of boron outdiffusion in SiGe HBT’s by carbon incorporation,” in IEDM Tech. Dig, 1996, pp. 249–252. [9] H. Rucker, B. Heinemann, D. Bolze, D. Knoll, D. Kruger, R. Kurps, H. J. Osten, P. Schley, B. Tillack, and P. Zaumseil, “Dopant diffusion in C-doped Si and SiGe: Physical model and experimental verification,” in IEDM Tech. Dig., 1999, pp. 345–348. [10] W. Fang, “Accurate analytical delay expressions for ECL and CML circuits and their applications to optimizing high-speed bipolar circuits,” IEEE J. Solid-State Circuits, vol. 25, pp. 572–583, 1990. [11] M. Rodwell, M. Urteaga, Y. Bester, T. Mathew, P. Krishnan, D. Scott, S. Jagannathan, D. Mensa, J. Guthrie, R. Pullela, Q. Lee, B. Agarwal, U. Bhattacharya, and S. Long, “Scaling to InGaAs/InAlAs HBT’s for high speed mixed signal and mm-wave ICs,” Int. J. High Speed Electron. Syst., vol. 11, no. 1, pp. 159–215, 2001. [12] J. Bock, H. Schafer, H. Knapp, D. Zoschg, K. Aufinger, M. Wurzer, S. Boguth, R. Stengl, R. Schreiter, and T. F. Meister, “High-speed SiGe : C bipolar technology,” in IEDM Tech. Dig., 2001, pp. 344–347. [13] M. Sokolich, C. H. Fields, S. Thomas, III, B. Shi, Y.-K. Boegeman, M. Montes, R. Martinez, A. R. Kramer, and M. Madhav, “A low power 72.8-GHz static frequency divider in AlInAs/InGaAs HBT technology,” IEEE J. Solid State Circuits, vol. 36, pp. 1328–1334, Sept. 2001. [14] K. Washio, M. Kondo, E. Ohue, K. Oda, and R. Hayami, “A 0.2m self-aligned SiGe HBT featuring 107-GHz f and 6.7-ps ECL,” in IEDM Tech. Dig., 1999, pp. 557–560. [15] T. Oka, K. Hirata, K. Ouchi, H. Uchiyama, T. Taniguchi, K. Mochizuki, and T. Nakamura, “Advanced performance of small-scaled InGaP/GaAs over 250 GHz,” in IEDM Tech. HBT’s with f over 150 GHz and f Dig., 1998, pp. 653–656. [16] D. Gloria, S. Gellida, and G. Morin, “A new extraction method of high frequency noise parameters in the temperature range 55/150deg. for SiGe HBT in BiCMOS process,” in Proc. ICMTS, 2000, pp. 229–234. [17] G. Freeman, D. Greenberg, K. Walter, and S. Subbanna, “SiGe HBT performance improvements from lateral scaling,” in Proc. Eur. SolidState Device Research Conf., 1999. [18] D. Terpstra and W. B. de Boer, “Anomalous collector base leakage in selectively grown SiGe base heterojunction bipolar transistors,” in Proc. 29th Eur. Solid State Device Research Conf., 1999, pp. 720–723. [19] K. Oda, E. Ohue, T. Onai, and K. Washio, “Heterojunction bipolar transistor,” U.S. Patent 5 962 880, Oct. 5, 1999. [20] J.-S. Rieh, D. Greenberg, B. Jagannathan, G. Freeman, and S. Subbanna, “Measurement and modeling of thermal resistance of high speed SiGe heterojunction bipolar transistors,” in Silicon Monolithic Integrated Circuits in RF Systems Dig., 2001, pp. 110–113. 0 Greg Freeman (S’82–M’90–SM’03) received the B.S.E.E. degree from the University of Delaware, Newark, in 1984 and the M.S.E.E. and Ph.D. degrees from Stanford University, Stanford, CA, in 1986 and 1991, respectively. His dissertation dealt with data analysis for semiconductor process diagnosis. He has been with IBM’s East Fishkill, NY, facility since 1991 in the development of advanced semiconductor processes, including DRAMs, CMOS, and, since 1995, SiGe BiCMOS. His recent achievements include leading a team to develop the world’s first 210-GHz silicon–germanium heterojunction transistor. Since 2000, he has been a Senior Engineering Manager in IBM Microelectronics, responsible for communications technology research and development including device design, circuit applications, and process integration for SiGe HBTs as well as RF-CMOS. His past and current research interests are in device diagnostics, detailed device design, and the application of semiconductor devices and technologies. He has authored or coauthored over 40 technical publications and presentations in the fields of electrical characterization and SiGe HBT BiCMOS technology. FREEMAN et al.: TRANSISTOR DESIGN AND APPLICATION CONSIDERATIONS FOR Basanth Jagannathan (M’98) received the B.Tech. (Hons.) degree from the Indian Institute of Technology, Kharagpur, in 1992 and the Ph.D. degree in electrical engineering from the State University of New York at Buffalo in 1997. His doctoral work was on the growth of amorphous and micro crystalline silicon for solar cells and thin film transistors. Since 1997, he has been with IBM Microelectronics communication research and development, Hopewell Junction, NY, where he now an Advisory Engineer. He has contributed to the development of SiGe epitaxy and HBT design in IBM’s SiGe BiCMOS technologies. He is involved with SiGe technology definition and evaluation for high-speed communication applications. His current interests are toward understanding technology design and circuit topologies for implementing wireless and wired communication chips. Shwu-Jen Jeng received the B.S. degree in materials science and engineering from National Tsing-Hua University, Hsinchu, Taiwan, R.O.C., and the Ph.D. degree in materials science and engineering from the University of Illinois, Champaign-Urbana, in 1986. She was a Post-Doctoral Associate studying the reactive ion etching damage at the IBM T. J. Watson Research Center, Yorktown Heights, NY, from 1986 to 1988. She joined IBM Semiconductor Development Lab, Hopewell Junction, NY, in 1988 and worked on in situ oxide removal and silicidation of Si and wide bandgap emitter. In 1994, she joined IBM Microelectronics Semiconductor Research and Development Center and has been working on SiGe BiCMOS process and technology development. Jae-Sung Rieh (S89–M’91) received the B.S. and M.S. degrees in electronics engineering from Seoul National University, Seoul, Korea, in 1991 and 1995, respectively, and the Ph.D. degree in electrical engineering from The University of Michigan, Ann Arbor, in 1999. His doctoral research involved the development of SiGe-based electrical and optical devices and their application to microwave and optoelectronic integrated circuits. In 1999, he joined IBM Communications R&D Center, where he has been involved in the design and characterization of ultrahigh-speed SiGe HBTs for analog and mixed-signal applications and the analysis and modeling of the thermal and avalanche behavior of the SiGe HBTs. 200-GHz SiGe HBTs 655 Andreas D. Stricker was born in Bern, Switzerland, in February 1965. He received the M.S. degree in applied physics from the University of Bern in 1992 and the Ph.D. degree from the Swiss Federal Institute of Technology, Zürich, in 2000. His dissertation was titled “TCAD of ESD protection devices.” While at the University of Bern, he worked in the field of LASER interactions with solid state materials. His fields of interest were on-chip ESD-protection circuits as well as their development using process and device simulations. He is now with IBM Microelectronics, Burlington, VT, where he joined the SiGe design kit development group. David C. Ahlgren received the B.A. frhtrr from DePauw University, Greencastle, IN, in 1973 and the Ph.D. degree in chemical physics from The University of Michigan, Ann Arbor, in 1979. He joined IBM, Hopewell Junction, NY, in 1979, conducting semiconductor process development. His early work was in the area of silicon defects resulting from ion implantation and isolation stress, as well as process integration issues which lead to the development and subsequent production of IBM’s first double polysilicon bipolar technology in 1983. In 1989, his attention turned to Si/SiGe HBTs as the next step in the advancement of IBM’s bipolar mainframe semiconductor technology. His early device studies, process technology work, and semiconductor production experience has lead him into his role in the Advanced Semiconductor Technology Center as a Senior Engineer in device and process development of high-performance Si/SiGe BiCMOS technology and its introduction into manufacturing. He is currently Senior Engineering Manager of SiGe Advanced BiCMOS Technology Development. He has published over 30 technical papers and holds eight patents in semiconductor device and process technology. Seshadri Subbanna (S’79–M’83) received the is B. Tech. degree in electrical engineering from the Indian Institute of Technology, Bombay, and the M.S.E.E. and Ph. D. degrees in electrical engineering and materials science from the University of California at Santa Barbara. His doctoral work was on optical and electronic properties of antimonide superlattices and heterostructures, including the first observation of quadratic piezo-electrooptic effect in strained superlatties. From 1989 to 2002, he was with IBM Microelectronics, East Fishkill, NY. Since joining IBM, he has worked on advanced bipolar and CMOS processes, high-density SRAM development, and BiCMOS technology. From 1996 to 2002, he was manager of advanced silicon-germanium (SiGe) heterojunction bipolar transistor (HBT) BiCMOS development at the IBM Microelectronics Semiconductor Research and Development Center. This group was the first to achieve over 200-GHz high-frequency performance in a silicon-based technology, and his group is recognized world-wide as a leader in development of high-speed networking technology. He was also a senior business counsel charged with intellectual property development and patent generation. Currently he is on assignment in IBM Systems Group (previously IBM Server Group). He has given many invited talks and has over 50 publications and 20 patents to his credit.