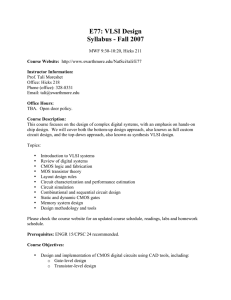

Digital VLSI Design I: Basic Subsystems

advertisement

f10s_dvls.fm - 1

Lecture: MWF 2.00-2.50 PL-3200

Offfice hours: MWF 3.00-4.00PM in NI-2049

Lab: F 3:00-4:50 NE-1026

The University of Toledo

Dr. Anthony D. Johnson

EECS:4610/5610/7610 Digital VLSI Design I: Basic Subsystems

Digital VLSI Design I: Basic Subsystems

SYLLABUS

Week Starting Date

1. August

2. August

3. September

4.

5.

6.

7.

Subject

23

Ch.1. Introduction to CMOS technology.

30

Ch.3. CMOS Processing technology.Basic CMOS technology.

6

Section 3.3 Layout Design rules. Physical design of basic logic gates.[Hwk#1:NOR gate hand

layout]

September

13

CAD tools: The layout editor IC Station.

September

20

Section 8.9 Interchange Formats: CIF, EDIF, GDS II.. [Hwk #2: NOR gate Led layout].

September

27

Section 8.8. CMOS Physical Design Styles ]. [Hwk #3: NOR gate CIF file]

October

4

8. October.

11

Ch.10. Datapath subsystems: Adders and munltipliers functions.

Ch.10. Datapath subsystems: Counters, comparators, zero-detectors, parity generators,

ALUs.{Begin term projects}

18

9. October

25

10. October

11. November 1

Section .8.3 Design methodology and tools: 8.3.3 Gate arrays, CPLDs, FPGAs.

12.

13.

14.

15.

16.

Ch.4. Circuit characterization and performance Estimation: 4.2.3Logical effort

Ch. 6. Combinational circuit design:

November

8

Ch. 7. Sequential logic gate design: Latches and Registers

November

15

Section 4.4.3 Low-power Design. Midterm Exam.

November

22

Ch. 12. Special purpose subsystems: 12.4 I/O structures.

November

29

Instruction on preparing the Term Project Design for fabrication

December

6

Ch.8. Design methodology and tools.

(Thursday 12:30 to 2:30?) Student presentation on projects.

Goals:

Gaining the knowledge of basic and advanced concepts and methods in VLSI Design. Hands-on

knowledge of the industry level state of the art VLSI design tools for Electronic Design Automation.

Textbook:

Weste, N., D. Harris: CMOS VLSI Design, Addison-Wesley, 2005, ISBN 0-321-14901-7.

Lab tutorial:

Extract from Mentor Graphic's manuals for ADK.

Suggested reading:

Michael S. Smith: Application Specific Integrated Circuits, Addison-Wesley,1997. (This same

book is the course textbook for two other VLSI courses: EECS 4630/5630 Physical Design of

VLSI Circuits, and EECS 6660/8660 Field Programmable Gate Arrays.

Grading Policy:

Homeworks /Lab/ Midterm /Project = 12 /12/ 36 / 40.

Instructor:

Dr. A.D. Johnson; office NI-2049; phone X-8176.

T.A.

Mr. Michael Cassavar, office NE-2036, office hours WR 3.00-4.00PM , phone X-8292; email:

mcassava@eng.utoledo.edu.

The University of Toledo

Dr. Anthony D. Johnson

EECS:4610/5610/7610 Digital VLSI Design I: Basic Subsystems

f10s_dvls.fm - 2

Lecture: MWF 2.00-2.50 PL-3200

Offfice hours: MWF 3.00-4.00PM in NI-2049

Lab: F 3:00-4:50 NE-1026

Lab schedule

Lab#

1o

2o

3o

4o

5o

6o

topic

week assigned

Organizing the Course File System in the student Environment

1

NOR3 circuit model using the Frame Maker Editor

2

Circuit models using the Design Architect tool

3

Simulating circuits based on the Design Architect models

4

Using the IC Station tool for creating circuit layouts

5

LVS test using the Caliber (batch processing) tool

7

week due

2

3

4

5

7

8

Homework schedule

Hwk#

1o

2o

3o

topic

week assigned

Hand layout of NOR3 and a project leaf-cell gate

3

CIF description file of the NOR3 gate hand-layout.

5

Complex gate design using single rows of n- and p-diffusion.

6

week due

5

6

7

Project progress report schedule

Phase

1.

2.

3.

4.

5.

6.

7.

8.

Report Topic

week assigned

week due

Behavioral description of the project circuit.

#6

#7

Architecture, logic design, and floor planning.

#7

#8

Technology mapping of leaf-cells and logic circuit models on all

hierarchical levels. Simulation of circuit models on all levels.

#8

#10

Leaf-cell layout design and LVS testing.

#10

#11

Whole circuit Layout design and LVS testing.

#11

#13

Framing the core logic and submitting for fabrication.

#13

#15

Public presentation and defense of the final report.

#8

#17

The chip test report

chip delivery one week later

Policy on the submission of homework and project reports

1.

2.

3.

4.

5.

6.

All text, figures, and tables in the reports must be computer generated and formatted. Usage of the FrameMaker text

editor is encouraged because of its extended capabilities, and because of the technical support available from the instructor. All progress reports must be structured as the chapters of the Final report.

To encourage a high quality work, the successful completion of term projects, and a professional look of the reports,

up to one resubmission of the reports will be accepted in the next week after the regular due week for full credit. To

qualify for the full credit resubmission, the original reports must be turned in on time, at least 80% completed.

All homework and Project progress reports are due at the beginning of the third class of the week. In order to discourage the practice of finishing the reports by working in a computer lab during the time scheduled for classes, the absolute deadline for turning in the reports is five minutes after the time scheduled for the beginning of the class.

All reports must be defended in person during the first scheduled office hours following the submission deadline. Students inrolled in other classes scheduled at that time should arrange for the defense at a different time.

All late submissions are accepted under equal late terms until the beginning of the first class of the next week.

This policy promotes good working habits. Therefore, the fact that the server was down the morning of the second

class of the week does not make a case for delaying the submission due time. Computers will always go down on us

from time to time, we ought to be prepared for the day when it happens.