Literature Number: DS-SY1007

January 31, 2014

Rev. 1.4

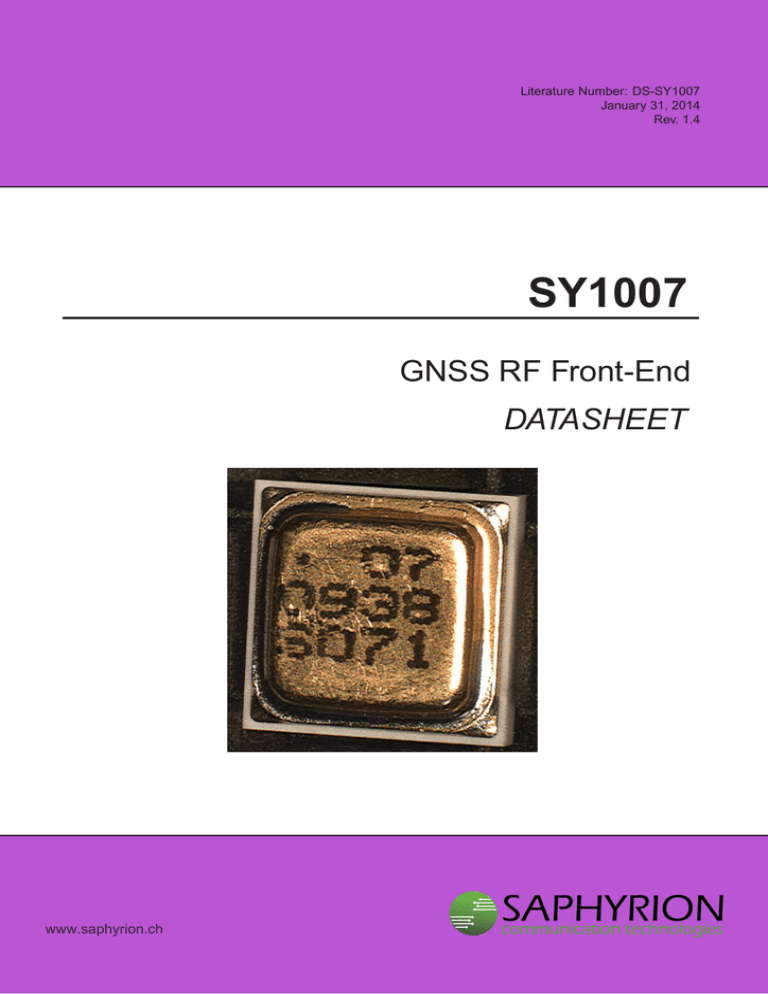

SY1007

GNSS RF Front-End

DATASHEET

www.saphyrion.ch

DATASHEET

SY1007 GNSS RF Front-End

Document Team

Author

Francesco Piazza

Reviewers

Lorenzo Moriggia

Christian Iera

Mariano Perna

Angelo Consoli

Revision History

Rev.

1.0

1.1

1.2

1.3

1.4

Date

September 16, 2009

November 26, 2009

October 4, 2011

August 19, 2013

January 31, 2014

Who

fp

fp

fp

fp

fp

Description

SPH document created, loosely derived from previous versions.

Expanded all sections (based on customer support requests).

Corrected errors and typos, added new sections (10 to 15).

Extended Sections 4, 5, 7 and 13, corrected typos (all sections),

added application example (Section 16).

Re-characterization of the VCOs: updated VCOs tuning curves

and phase noise specs, added VCOs phase noise graph. Added

handling precautions (Section 14), corrected IF PLL range.

Contents

1 General Description

1

2 Features

1

3 Applications

1

4 Absolute Maximum Ratings

2

5 Electrical Characteristics

2

6 Device Marking

4

7 Typical Operating Characteristics

5

8 Pin Description

6

9 Equivalent Circuits

7

10 Circuit Description

9

11 Serial Interface

10

12 Register File

11

13 Applications Information

12

14 Handling Precautions

17

15 Radiation Tolerance

17

16 Application Example

18

17 Layout Recommendations

21

18 PCB Recommendations

21

19 Mounting Recommendations

22

20 Package Drawing

23

ii

Saphyrion Sagl

Rev. 1.4, January 31, 2014

SY1007 GNSS RF Front-End

DS-SY1007 Rev. 1.4 - January 31, 2014

DATASHEET

2 Features

1 General Description

The SY1007 is a programmable dual conversion superheterodyne receiver. Both the RF and the IF local oscillators

can be independently programmed to accommodate various

frequency plans. It can be configured to receive all GPS,

all GLONASS and most Galileo signals in the L-band up to

a bandwidth of 24MHz by selecting the appropriate external

components and configuring the RF and IF PLLs. The output

is analog quadrature (I/Q) at base-band. Four low latency

power down modes are provided to aid in implementing different power saving schemes.

Complete, highly integrated RF front-end. Supports all

GNSS signals up to 24MHz bandwidth.

Compact, low bill-of-materials, small PCB area.

Low voltage operation, low power consumption.

•

The SY1007 is a radiation hardened L-band RF downconverter for GNSS receivers aimed at the professional and

space markets. This device is designed in a 0.35µm SiGe

process and includes all functional blocks needed to implement the complete RF front-end of multiband GNSS receivers, thus allowing a substantial reduction of BOM, size

and weight with respect to discrete designs. It directly interfaces to the ESA AGGA-4 GNSS base-band processor.

•

•

–

–

–

–

–

AVDD: 2.4V to 3.6V, DVDD: 2.2V to 3.6V.

Fully active: 12.3mA

Stand-by: 3.3mA

Doze: 280µA

Sleep: < 1µA

Supports passive and active antennas.

Flexible 2MHz to 5MHz reference frequency.

Analog quadrature I/Q outputs.

Compact 6mm x 6mm ceramic-metal BGA package.

•

•

•

•

3 Applications

Since the SY1007 mainly targets the space market, a

variant qualified to ESA ESCC9000 for satellite applications

is available. This variant has demonstrated latch-up and radiation damage free operation. The SY1007 comes into a

compact 6mm x 6mm ceramic-metal hermetic BGA package

containing no organic materials.

Space-borne GNSS receivers.

Precise orbit determination.

Antenna arrays, beam forming, attitude determination.

Multi-frequency precision/monitoring GNSS receivers.

Reliable GNSS receivers, safety of life.

•

•

•

•

•

Figure 1: SY1007 Block Diagram.

C4

A5

B4 A4

IF2P

B5

IF1P

RFP

C3

MIXN

A6

MIXP

C5

RFN

LNO

B6

C5

SAW

or LC

SAW

D6

AVDD

DVDD

IF-Filter 2

L4

C6

B3

E6

AVDD

B1

DVDD

DBM

I

LNA

RFin

C1

DBM

IF-Amp

VGA

L2

LPF

(15MHz)

LNI

F6

DBM

L1

F2

:N1

D1

D2

Buffers

Q

:4

OIP

OIN

log

OQP

C1

OQN

C2

AGCI

A3

RCP

A1

VB

bias

E5

I

:2

Q

:2

:N2

VBG

C8

C3 C4 C6

D3 D4 F5

RL1

D5

RL2

F3

L5

RF LO

inductor

F4

IF

VCO

PFC

RPLL

AVSS

RENB

RF

VCO

SY1007R

E3

R1

C9

IENB

C7

E4

C10

RF

Loop

filter

PFC

To ADC, base-band processor

IF-Filter 1

C2

IF2N

RF-Filter

L3

IF1N

GNSS

Antenna

A2

reg

DIO

IL1

IL2

E1

L6

IF LO

inductor

F1

IPLL

DVSS

E2

R2

C11

B2

C12

IF

Loop

filter

c 2014 Saphyrion SAGL. All Rights Reserved. All trademarks and registered trademarks are the property of their respective

Copyright owners. Saphyrion SAGL reserves the right to change the detail specifications as may be required to permit improvements in the design

of its products. Saphyrion SAGL assumes no responsibility for this product’s use, nor for any infringement of patents or other rights from

third parties which may result from its use. No license is implied under any patent or patent right by Saphyrion SAGL.

Saphyrion SAGL, CH-6934 Bioggio, Switzerland, http://www.saphyrion.ch

1

DATASHEET

SY1007 GNSS RF Front-End

4 Absolute Maximum Ratings

Max. supply voltage, AVDD, DVDD . . . . . . . . . . . . . . . . . . . . . . . . . 4.0V

Max. RF input on LNI, RFx . . . . . . . . . . . . . . . . . . . . . . . . . . . . +10dBm

ESD susceptibility, HBM, JESD22-A114 . . . . . . . . . . Class 1B, 1KV

Continuous power dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . 300mW

Current on any pin except LNI, RFx . . . . . . . . . . . . . . . . . . . . . . ±1mA

Current on supply and VB pins . . . . . . . . . . . . . . . . . . . . . . . . . .±50mA

Current on VBG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±10mA

Operating junction temperature . . . . . . . . . . . . . . . . . −55 to +125◦ C

Storage temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . −65 to +150◦ C

Lead temperature (soldering, 40s) . . . . . . . . . . . . . . . . . . . . . . . . 240◦ C

Voltage on any pin except LNI, RFx . . . . . . . . . . −0.3V / xVDD+0.3

Voltage on LNI (note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±0.3V

Voltage on RFx (note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +1.5V

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. Absolute maximum ratings are

short term stress ratings only; functional operation of the device at these or any other conditions beyond those indicated in the recommended

operating conditions is not implied. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

ESD sensitive device: Use proper precautions when handling this device.

Pb

Device contains lead: Product is not RoHS compliant and shall be handled accordingly. Do not disperse into the environment.

5 Electrical Characteristics

AVDD = 2.4V to 3.6V, DVDD = 2.2V to AVDD+0.2V, f(RCP) = 2.0MHz, Tjunction = −40◦ C to +125◦ C, no load, unless otherwise stated. All

voltages are referred to their respective VSS. Typical values are at AVDD = 3.0V, DVDD = 3.0V, Tjunction = +25◦ C.

Parameter

Conditions

Min

Typ

Max

Unit

Notes

1575MHz, noise matched

1575MHz, Z-matched

1575MHz, noise matched

1575MHz, Z-matched

Input referred

Noise matched

IP3, Input referred

S11, noise matched

S11, Z-matched

S22

18.2

18.9

20

1.6

4.5

−23

1.25

−10

−2

−15

−12

25.0

dB

dB

dB

dB

dBm

ns

dBm

dB

dB

dB

2

2

2

2

2

2

2

2

2

2

15

26

11.0

−13

−3

16

29

13.5

dB

dB

dB

dBm

dBm

dB

Ω

Ω

kΩ

pF

3

3

dB

dB

mV/dB

V

mV

Vpp

MHz

MHz

Ω

pF

5

5

5

LNA

Power gain

Noise figure

1dB compression point

Group delay

Third order intercept

Input refl. coefficient

Output refl. coefficient

−24

1.19

−14

1.8

−20

1.29

RF Mixer and 1st IF Stage

Conversion voltage gain

SSB noise figure

1dB compression point

Third order intercept

Input refl. coefficient

Differential resistances

Diff. capacitance

To MIXP-MIXN, no load

To IF1P-IF1N, no load

Differential output

Input referred, to MIXP-MIXN

Input referred, to MIXP-MIXN

S11 at 1.5742 GHz

MIXP to MIXN

IF1P to IF1N

IF2P to IF2N

MIX, IF1 and IF2

14

24

−16

500

500

54

600

600

65

0.5

64

50

6

1.5

−30

1.4

10

12

120

66

80

9

1.8

−15

720

720

81

3

3

4

4

4

IF Amplifier and Base-Band Section

VCA voltage gain

VCA gain control range

VCA sensitivity

DC output voltage

DC offset voltage

Output signal amplitude

IF amp bandwidth

I/Q 3dB Bandwidth

I/Q output Impedance

I/Q load capacitance

2

I/Q output, V(AGCI) ≥ 2V

V(AGCI) = 0.3V to 2V, Fig. 8

pin AGCI

I/Q to AVSS, VDD=2.5V

I/Q outputs

≤ 1dB compression

Internal low-pass filter

See note 6!

No bandwidth reduction

Saphyrion Sagl

12

2.1

+30

1.8

15

125

400

18

150

10

6

Rev. 1.4, January 31, 2014

DATASHEET

Parameter

SY1007 GNSS RF Front-End

Conditions

Min

Typ

Max

Unit

Notes

1.50

1050

255

63

GHz

MHz/V

14

14

Local Oscillator, RF PLL

VCO frequency range

VCO sensitivity

Main PLL divider range

Charge Pump Current

PLL SSB phase noise

PLL spurs

Ext. RF LO amplitude

Ext. RF LO resistance

Ext. RF LO capacitance

L=4.7nH between RL1 & RL2

L=4.7nH between RL1 & RL2

Pin RPLL

100Hz offset

1kHz offset

10kHz offset

100kHz offset

1MHz offset

Recommended loop filter

Between RL1 & RL2, RENB=1

Between RL1 & RL2, RENB=1

Between RL1 & RL2, RENB=1

1.35

740

64

42

880

50

−58

−66

−68

−70

−100

−40

+5

−17

10

1.5

µA

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc

dBu

kΩ

pF

7,14

7,14

7,14

7,14

7,14

15

Local Oscillator, IF PLL

VCO frequency range

VCO sensitivity

Main PLL divider range

Charge Pump Current

PLL SSB phase noise

PLL spurs

Ext. IF VCO amplitude

Ext. IF VCO resistance

Ext. IF VCO capacitance

L=47nH between IL1 & IL2

L=47nH between IL1 & IL2

Pin IPLL

100Hz offset

1kHz offset

10kHz offset

100kHz offset

1MHz offset

Recommended loop filter

Between IL1 & IL2, IENB=1

Between IL1 & IL2, IENB=1

Between IL1 & IL2, IENB=1

360

160

32

42

250

50

−78

−86

−88

−95

−110

−60

420

298

255

63

+5

−17

10

2.0

MHz

MHz/V

µA

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc

dBu

kΩ

pF

16,17

16,17

7,16

7,16

7,16

7,16

7,16

7

15,17

Voltage Regulator

Band-gap voltage

Band-gap output current

Band-gap load regulation

Regulator output voltage

Regulator line regulation

Regulator output current

Regulator load regulation

No load

1.12

200

I(VGB) = 0 to −200µA

No load

AVDD 2.4V to 3.6V

1.8

1.17

1.22

2

1.9

4

5

2.0

10

7

15

1

I(VB) = 0 to −4mA

V

µA

mV

V

mV

mA

mV

8

8

9

Digital Interface

Reference Freq. Range

Input capacitance

Input high level

Input low level

Output high level

Output low level

Output rise time

Output fall time

1.9

RCP and DIO

5

1.0

0.7 DVDD

−0.2

0.9 DVDD

I(OH) = −1mA

I(OL) = +1mA

C(LOAD) = 5pF

C(LOAD) = 5pF

3.4

2.8

MHz

pF

DVDD+0.2 V

0.3 DVDD V

V

0.1 DVDD V

6.1

ns

4.8

ns

10

10

Power Supply

Supply Voltage

Supply Current

Analog

Digital

Fully active

Stand-by

Doze

Sleep

Rev. 1.4, January 31, 2014

AVDD

DVDD

AVDD

DVDD

AVDD

DVDD

AVDD

DVDD

AVDD/DVDD

2.4

2.2

9.5

20

2.0

20

180

2

Saphyrion Sagl

12.5

40

3.3

40

280

5

3.6

AVDD+0.2

19.0

80

5.5

80

380

10

100

V

V

mA

µA

mA

µA

µA

µA

nA

11

11

11

11

3

DATASHEET

SY1007 GNSS RF Front-End

Parameter

Conditions

Min

Typ

Max

Unit

+125

+125

◦

Notes

Thermal Characteristics

Operating temp. range

Guaranteed performance

No degradation

Junction to case

Thermal resistance Rth

−40

−55

25

C

C

◦

C/W

◦

Radiation Characteristics

Total dose (C60)

Dose rate (C60)

LET

100

12

No latch-up

45

kRad(Si)

Rad/min

2

MeV cm

mg

18

Notes

Note 1: LNI and RFx pins shall be AC coupled. Setting LNI to 0V disables the LNA. Shorting RFx to VSS will damage the device.

Note 2: LNA with recommended input and output matching networks (see section 13.3.1).

Note 3: Voltage conversion gain, differential, input is RFP-RFN, output as indicated, unloaded.

Note 4: I/O impedances track to 5% or better.

Note 5: Voltage gain, from IF2P-IF2N, differential, to OIP-OIN or OQP-OQN, also differential.

Note 6: Caution: OIP-OIN and OQP-OQN shall not be loaded with less than 10kΩ, or severe distortion and amplitude limiting will occur.

Note 7: Closed PLL loop, with 33µF decoupling capacitors on VBG pins to reduce noise of bias circuit.

Note 8: Minimum current available to an external load under worst-case conditions.

Note 9: Doze mode, internal loads are turned off.

Note 10: Measured between the 10% and 90% points. Load capacitance on these pins must be minimized (preferably below 5pF).

Note 11: Supply current increases with temperature (see Figure 12).

Note 12: Minimum and maximum frequency allowed.

Note 13: Voltage range needed to guarantee full AGC regulation.

Note 14: With L = 4.7nH, muRata LQW18, reference test board. Other frequency ranges may be obtained using different inductor values.

Note 15: Referred to 50Ω (0dBu=223.6mV). Signal levels between −8dBu and 0dBu give the best, most stable performances.

Note 16: With L = 47nH, muRata LQW18, reference test board. Other frequency ranges may be obtained using different inductor values.

Note 17: IF local oscillator frequency is half the VCO frequency, i.e. f(LO) = f(VCO)/2 (see Section 10).

Note 18: DUTs have been tested at 85◦ C and xVDD=3.6V until a cumulated fluence of 1E+7 ions/cm2 without detecting any latch-up.

6 Device Marking

The marking of the device is in accordance with the requirements of ESCC Basic Specification No. 21700. The information

to be marked on the component shall as a minimum be:

•

•

•

Terminal identification.

Component number.

Traceability information.

Engineering model marking may occasionally deviate from the specification shown here. Please consult with Saphyrion in

case of doubt.

SY1007R – Engineering Model (EM) Marking

07

YYWW

Rxxx

A1 dot and die part number: 07=SY1007.

YYWW = Year and week of sealing.

R = EM part, xxx = Unique serial number.

SY1007S – Flight Model (FM) Marking

07

YYWW

Sxxx

4

A1 dot and die part number: 07=SY1007.

YYWW = Year and week of sealing.

S = FM part, xxx = Unique serial number.

Saphyrion Sagl

Rev. 1.4, January 31, 2014

DATASHEET

SY1007 GNSS RF Front-End

7 Typical Operating Characteristics

Figure 3: LNA Linearity

+20

15

0

LNA noise matched

at 1.57GHz

10

NF (dB)

5

Figure 4: LNA S11 and S22

+10

+5

CP

0

S11-S22 (dB)

20

Pout (dBm)

Gain (dB)

Figure 2: LNA Gain and NF.

IP3

-20

-40

2

-5

-10

-15

-30

-60

1.5

-25

1

1.0

1.2

1.4

1.6

1.8

Frequency (GHz)

-80

-50

2.0

Figure 5: RF Mixer Gain

-40

-30

-20

Pin (dBm)

-10

0

Figure 6: RF Mixer Linearity

30

S11

S22

-30

1.0

1.2

1.4

1.6

1.8

Frequency [GHz]

2.0

Figure 7: LNA S21 and S12

+30

+30

+20

+10

To MIXP-MIXN

CP

+10

-10

S21-S12 (dB)

20

Vout (dBu)

Voltage Gain (dB)

To IF1P-IF1N

IP3

-30

10

0.0

-10

-20

-30

-50

-40

0

-60

-30

0

30

60

90

Temperature (°C)

-70

-40

120

Figure 8: IF Amp Gain vs. AGC

-30

-20

-10

Pin (dBm)

0

-50

1.0

+10

Figure 9: RF VCO tuning curve

L(IF) = 47nH

-40°C

0

-55°C

3.6V

1.55

3.6V

1.50

3.0V

2.4V

1.45

1.40

1.35

-40°C

25°C

125°C

-30

1.30

-60

0

1

2

AGC Voltage (V)

3

Figure 11: VCOs phase noise

1.25

0.0

-80

IF-LO

-100

2.4V

200

IF LO frequency is

shown (VCO is at

2x LO frequency).

190

180

-40°C

25°C

125°C

160

0.0

2.5

0.5

1.0

1.5

2.0

Tuning Voltage (V)

2.5

Figure 13: VBG/VB vs. Temp.

1.914

VB

16

RF-LO

-60

1.0

1.5

2.0

Tuning Voltage (V)

18

f(RF-LO) = 1400MHz

f(IF-LO) = 185MHz

f(RCP) = 2.0MHz

-40

0.5

3.0V

210

170

Figure 12: I(AVDD) vs. Temp.

14

I AVDD (mA)

Phase noise (dBc/Hz)

-20

Frequency (MHz)

27°C

2.0

220

3.6V

2.4V

12

10

Output Voltage (V)

125°C

30

Frequency (GHz)

Gain (dB)

85°C

1.4

1.6

1.8

Frequency [GHz]

230

L(RF) = 4.7nH

1.60

60

1.2

Figure 10: IF VCO tuning curve

1.65

90

S21

S12

1.910

1.184

VBG

8

1.181

-120

1

10

100 1k 10k 100k 1M

Frequency offset (Hz)

Rev. 1.4, January 31, 2014

6

-60

-30

0

30

60

90 120

Temperature (°C)

Saphyrion Sagl

-40

-20

0

20

40

60

Temperature (°C)

80

5

DATASHEET

SY1007 GNSS RF Front-End

8 Pin Description

1

2

3

4

5

6

A

B

C

D

E

F

Figure 14: SY1007 pin-out (top view).

Name

RCP

DIO

AGCI

IF2P

IF1P

MIXP

DVDD

DVSS

IF2N

IF1N

MIXN

RFP

OQP

OQN

AVSS

AVSS

RFN

AVSS

OIP

OIN

AVSS

AVSS

RENB

LNO

IL1

IPLL

RPLL

IENB

VBG

AVDD

IL2

VB

RL1

RL2

AVSS

LNI

6

Ball

A1

A2

A3

A4

A5

A6

B1

B2

B3

B4

B5

B6

C1

C2

C3

C4

C5

C6

D1

D2

D3

D4

D5

D6

E1

E2

E3

E4

E5

E6

F1

F2

F3

F4

F5

F6

Domain

DVDD

DVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

AVDD

Description

External reference clock.

Digital input output interface, needs a weak pull down. Test: scan output.

Set the AGC IF conversion gain, to be connected to a decoupling capacitor.

IF VGA positive input.

First IF amplifier positive output.

RF mixer IF positive output.

Positive digital supply voltage.

Negative digital supply voltage.

IF VGA negative input.

First IF amplifier negative output.

RF mixer IF negative output.

Radio frequency positive mixer input.

Quadrature base-band GNSS positive signal.

Quadrature base-band GNSS negative signal.

Negative analog supply voltage.

Negative analog supply voltage.

Radio frequency negative mixer input.

Negative analog supply voltage.

In-phase base-band GNSS positive signal.

In-phase base-band GNSS negative signal.

Negative analog supply voltage.

Negative analog supply voltage.

RF PLL enable – active low. Test: scan enable (SE).

LNA output.

IF VCO tank-circuit – first terminal.

IF PLL loop filter.

Output of the PLL phase frequency comparator, connect to the output filter.

IF PLL enable – active low. Test: scan input (SI).

Band-gap voltage reference output, 1.2V. Decouple to AVSS close to the chip.

Positive analog supply voltage.

IF VCO tank-circuit – second terminal.

Voltage regulator output, 1.9V. Decouple to AVSS close to the chip.

RF VCO tank-circuit – first terminal.

RF VCO tank-circuit – second terminal.

Negative analog supply voltage.

LNA input.

Saphyrion Sagl

Rev. 1.4, January 31, 2014

DATASHEET

SY1007 GNSS RF Front-End

9 Equivalent Circuits

Pin

A1

A2

D5

E4

Description

RCP

DIO

RENB

IENB

Equivalent circuit

Digital inputs and outputs

xVDD

RENB, IENB,

RCP, DIO

ESD

ESD

ESD

ESD

xVSS

E3

E2

RPLL

IPLL

DVDD

DIO

DVSS

PLL charge pump outputs

AVDD

50µA

UP

RPLL

IPLL

DN

ESD

CLAMP

50µA

AVSS

F6

D6

LNI

LNO

LNA input and output

AVDD

500

ESD

LNO

bias-1

bias-2

18k

LNI

ESD

ESD

AVSS

B6

C5

RFP

RFN

RF mixer input

(internally matched to 50Ω)

AVDD

ESD

ESD

Bias

RFP

RFN

ESD

ESD

AVSS

A6

B5

A5

B4

MIXP

MIXN

IF1P

IF1N

IF input/output

AVDD

300Ω

MIXP,

IF1P

300Ω

ESD

ESD

MIXN,

IF1N

Mixer

IF-amp

ESD

ESD

AVSS

Rev. 1.4, January 31, 2014

Saphyrion Sagl

7

DATASHEET

Pin

A4

B3

SY1007 GNSS RF Front-End

Description

IF2P

IF2N

Equivalent circuit

IF VCA input (AGC)

AVDD

VBG

ESD

65kΩ

65kΩ

ESD

IF2P

IF2N

ESD

ESD

ESD

ESD

AVSS

A3

AGC

AGC control circuit, gain control input

AVDD

ESD

AGCI

ESD

AVSS

C1

C2

D1

D2

OQP

OQN

OIP

OIN

Quadrature I/Q base-band outputs

AVDD

ESD

OIP

OQP

OIN

OQN

ESD

AVSS

F3

F4

E1

F1

RL1

RL2

IL1

IL2

RF and IF voltage controlled oscillators

AVDD

RL1

IL1

RPLL

IPLL

8

Saphyrion Sagl

ESD

ESD

ESD

ESD

RL2

IL2

AVSS

Rev. 1.4, January 31, 2014

DATASHEET

10

SY1007 GNSS RF Front-End

Circuit Description

The SY1007 is a radiation hardened super-heterodyne RF

front-end for GNSS receivers aimed at aerospace applications. It offers a high degree of versatility and can be configured to receive all GPS, all GLONASS and most Galileo

signals in the L-band up to a bandwidth of 24MHz by selecting the appropriate external components and configuring the RF and IF PLLs. The output is base-band analog

I/Q. All active building blocks needed to construct a GNSS

RF receiver channel are included on-chip. RF and IF filters

are external to the chip such that their bandwidth and order

can be selected to suit the needs of various applications.

10.1 LNA

The LNA is a single stage cascode amplifier. It requires external matching networks at both its input and output and

can be configured for all GNSS frequencies by adjusting

the matching networks. It provides about 20dB gain and

1.6dB NF under noise matching conditions. Pin LNI is the

LNA input, is biased to about 0.7V and shall be AC coupled. Pin LNO is the output of the LNA and needs to be

biased at AVDD. If desired the LNA can be disabled permanently by connecting its input to AVSS. In that case an

external LNA is needed.

as a vectorial I/Q signal on pins OIP, OIN, OQP and OQN.

In order to obtain an accurate I/Q output the quadrature LO

signal is obtained with a divider-by-2. In consequence, the

IF-VCO frequency shall always be set to 2x the required

LO frequency to compensate this division. The VCO signal can be generated either by the on-chip IF-VCO or can

be supplied by an external PLL to pins IL1 and IL2 as a

differential signal. Pin IENB selects between internal PLL

(IENB = 0) and external LO signal (IENB = 1).

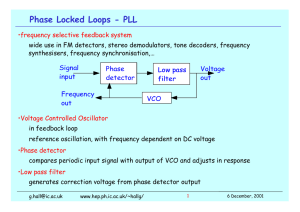

10.5 RF and IF PLLs

The SY1007 requires 2 local oscillator signals: one for the

RF and a second one for the IF downconverters. These

signals can be either generated by the on-chip RF and IF

local oscillators or supplied externally. The VCOs are balanced LC oscillators and require one external coil.

(Register)

N

Loop Filter

RF

Mixer

VCO

RCP

LO

(Register)

N

(4-255)

:2

:2

Loop Filter

2xLO

I/Q

Mixers

VCO

10.2 RF Mixer

RCP

The RF mixer converts the RF signal to the 1st IF. The

mixer is double-balanced, provides a voltage gain of 15dB

and a SSB noise figure of 11dB. The input is balanced and

provides a broad-band 50Ω impedance to directly match

typical SAW filters for GNSS use. The output of the mixer

is balanced, has an impedance of 600Ω and is meant to

be connected to an LC tank-circuit (part of the IF filter).

It is directly connected to the 1st IF amplifier stage internally. The local oscillator signal is either generated by the

on-chip RF-VCO or can be supplied externally to the pins

RL1 and RL2 as a differential signal.

10.3 IF-Strip

The IF-strip consists of a fixed gain (11dB) amplifier followed by a 3-stage variable gain IF amplifier with logarithmic (dB-linear) gain control. A differential amplifier structure has been used to achieve rejection to common mode

signals. The input of the fixed gain stage is connected to

the mixer, while the 600Ω output is available on pins IF1P

and IF1N, which are meant to be connected to the 2nd section of the LC IF-filter. The variable gain amplifier provides

about 45dB gain and ≥ 50dB control range. The input is

balanced, has an impedance of about 65kΩ and is biased

at 1.2V by the band-gap voltage reference. The output is

internally connected to the following stages and is not accessible externally.

10.4 I/Q Downconverter

The I/Q downconverter converts the output of the IF-strip

to a base-band signal. This quadrature downconverted

signal is then low-pass filtered by a 3rd order Bessel active

filter with 15MHz bandwidth, amplified by 12dB and output

Rev. 1.4, January 31, 2014

:4

(64-255)

Figure 15: SY1007’s RF and I/Q PLL configuration.

The integer-N PLLs are independent from each other

and can be programmed via the serial interface. They both

use the clock signal applied to pin RCP as reference. Their

output frequency is calculated as follows (see figure 15):

• RF PLL: f(RF-LO) = 4*N1*f(RCP); 64≤N1≤255.

• IF PLL: f(IF-LO) = N2*f(RCP)

⇒ f(IF-VCO) = 2*N2*f(RCP); 32≤N2≤255.

The CRC loop filters shall be connected to pins RPLL and

IPLL respectively. The RF and IF PLLs can be enabled independently by setting pins RENB and IENB to logic low.

When disabled (pins xENB to logic high) the balanced external local oscillator signals shall be applied to pins RL1RL2 and IL1-IL2 respectively while pins RPLL and IPLL

shall be left open. The PLL enable pins RENB and IENB

are also used as test inputs by the testability logic.

10.6 Band-Gap Reference

It is a band-gap voltage reference generating approximately 1.17V. It is used by most analog blocks and its output is available on pin VBG. It is able to source up to 200µA

but can sink a couple µA at most. It requires an external

capacitor ≥1µF for stability, although larger capacitors are

recommended to reduce noise voltage.

10.7 LDO Voltage Regulator

It is a linear low drop-out voltage regulator meant to generate the supply voltage for the parts of the SY1007 that

are sensitive to power supply noise and ripple (mainly the

Saphyrion Sagl

9

DATASHEET

SY1007 GNSS RF Front-End

PLL). The nominal output voltage is 1.9V. A ≥1µF capacitor – which can be increased without limit – is required

for stability. The LDO is able to source up to 15mA and

its output is the VB pin. Although not explicitely meant to

supply external loads, the LDO can power external circuits

consuming up to 1mA, provided that they don’t generate

power supply noise that would disturb the internal SY1007

sensitive parts.

aborted. The second 8-bit block contains the data read or

written to the selected register, in LSB-first form.

Back-to-back communications (no idle cycles between

two consecutive communications) are supported. If DIO is

pulled high immediately after the completion of the previous communication, the SY1007 accepts a new communication already at the clock cycle following the last data bit

(bit D7).

10.8 Serial Bus and Register File

11.2 Timing Diagram

A configuration register, accessible via a single-wire serial

interface, is implemented on the SY1007. Its purpose is to

configure the RF and IF PLLs and control the power modes

of the device. The register is protected against SEU with a

Hamming error correction mechanism.

The SY1007 samples the DIO line on the falling edge

of RCP. If requested to return data (read operation), the

SY1007 will drive DIO and send data bits on RCP falling

edge. At the end of a communication the DIO line goes

low, the interface then remains idle as long as the DIO line

is kept low. Figure 16, and tables 5 and 6 show the timing

diagram of the serial interface.

11

Serial Interface

tcp

The SY1007 can be programmed via a single wire synchronous interface.

The following can be accessed

through the serial interface:

•

•

•

RCP

tsu

Power modes;

RF PLL main divider;

IF PLL main divider.

All registers are read/write in order to allow reading

back their contents for verification purposes. In case an

error is detected (may happen only under a high radiation

environment) the affected register needs to be rewritten.

tpd

DIO(W)

T

WR

A0

DIO(R)

T

WR

A0

D4

D4

tpZ

D5

D5

D6

D6

tr

D7

D7

tf

Figure 16: Serial interface timing diagram.

Name

tcp

tsu

th

tpdLH

tpdHL

tpZ

tr

tf

11.1 Communications Protocol

Communication to the SY1007 occurs through a singlewire synchronous bidirectional interface (pin DIO) that is

synchronous to RCP. The SY1007 works as a slave and

never initiates a communication.

A communication always consists of packets of two

blocks: a control word and a data byte. Figure 17 shows

a write and a read packet respectively. A packet consists

of a start bit, followed by 6 bits (read) or 7 bits (write) depending on the operation requested, then by 8 data bits.

The master device cannot abort an on-going packet. An

aborted packet may cause register corruption.

The control word – always sent by the master device

(typically a SY1017) – specifies the kind of operation required (read or write) and the address of the register to be

accessed. A communication is initiated by setting the DIO

pin to logic 1 for one clock cycle. A parity bit (odd parity) is

required, and in case a parity error occurs the operation is

Parameter

Clock cycle time

Setup time

Hold time

Propagation delay L→H

Propagation delay H→L

Propagation delay to Z

Output rise time, 10-90%

Output fall time, 90-10%

Min

200

15

Typ

Max

4.0

5.5

4.0

3.6

3.3

0

8.5

7.6

7.0

6.1

4.8

Unit

ns

ns

ns

ns

ns

ns

ns

ns

Table 5: Conditions: 2.2V, 125◦ C, Cl=5pF.

Name

tcp

tsu

th

tpdLH

tpdHL

tpZ

tr

tf

Parameter

Clock cycle time

Setup time

Hold time

Propagation delay L→H

Propagation delay H→L

Propagation delay to Z

Output rise time, 10-90%

Output fall time, 90-10%

Min

200

10

Typ

Max

2.4

4.0

2.4

3.4

2.8

0

6.4

5.7

5.5

4.9

3.8

Unit

ns

ns

ns

ns

ns

ns

ns

ns

Table 6: Conditions: 3.0V, 125◦ C, Cl=5pF.

RCP

DIO(W)

ST

WR

A0

A1

A2

P

R

DIO(R)

ST

WR

A0

A1

A2

P

R

R

D0

D0

D1

D1

D2

D2

D3

D3

D4

D4

D5

D5

D6

D6

D7

D7

Figure 17: SY1007 read and write packets.

10

Saphyrion Sagl

Rev. 1.4, January 31, 2014

DATASHEET

SY1007 GNSS RF Front-End

11.3 Packet Structure

A packet consists of 2 blocks: a control word followed by

a data byte. The structure of the control word is shown in

table 7 and the meaning of the various fields in the control

word is shown in table 8.

Field

Position

Start

0

WR

1

Addr

2:4

P

5

Res

6(7)

these locations results in no operation, in future versions it

could results in temporary malfunctions.

RW

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

Data

8:15

Table 7: Structure of the control word.

Field

Start

WR

Addr[0:2]

P

Res

Data[0:7]

Description

Must go HIGH to start communication.

Transfer direction:

0 : READ operation.

1 : WRITE operation.

Register address, LSB first (see table 9).

Parity. It is calculated on Start bit, Write and Address fields. Parity is ODD, i.e. the number of 1’s in

bits [4:0] of the control word must be odd.

Reserved (1 bit for read, 2 bit for write).

Write operation: the master sends the data to be

written in register.

Read operation: the SY1007 returns the register

content.

Table 8: Description of the control word.

11.4 Parity Check

As a means to prevent registers corruption during write under a high radiation environment, parity check is performed

on the control word. Parity is calculated on the valid fields

of the control word, i.e. Start, WR and Addr[0:2]. The

Res[0:1] bits are not used to calculate parity. The expected

parity type is odd, i.e. the total number of 1’s in bits [0:5] of

the control word must be odd. If a parity error is detected

during a write operation, e.g. a SEU occurs, that operation

is immediately aborted, i.e. the data is discarded and the

corresponding register is not updated.

The parity bit is ignored during a read operation,

i.e. the data is returned regardless of the value of the parity

bit. It is highly recommended that every write is followed by

a read operation to verify that the write actually succeeded

and that the written value is the intended one.

12

Register File

12.1 Register Map

The register map is reported in table 9. Register locations marked as Reserved are reserved for future developments. To maintain compatibility with new releases of the

SY1007 no attempt should be made to access these locations. While in the current release an attempt to access

Address

A1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

A0

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

A2

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Dir

Register

R

R

R

R

R

R

R

R

W

W

W

W

W

W

W

W

RF-PLL (8-bit)

Reserved

Pwr-Modes (2-bit)

Reserved

IF-PLL (8-bit)

Reserved

Reserved

Reserved

RF-PLL (8-bit)

Reserved

Pwr-Modes (2-bit)

Reserved

IF-PLL (8-bit)

Reserved

Reserved

Reserved

Table 9: Register map.

12.2 Register Fields

The meaning of the fields of all registers is shown in table 10. The fields marked as Reserved are reserved for

future developments. To maintain compatibility with new

releases of the SY1007 it is recommended that these fields

are written with zeros. When read back these fields return

zeros. The content of all registers is undefined until written, there is no default value.

12.3 Hamming Error Correction

As a means to protect the register’s content from single

event upset (SEU) errors that may occur under high radiation, Hamming error correction has been implemented on

all registers. This error correction mechanism is able to

correct up to one error per register per clock cycle.

To implement Hamming error correction 12-bit registers are used, as shown in figure 18. Each register holds

the actual data value and 4 check-sum bits. During a register write cycle the new check-sum is computed by the

generation matrix and stored in the register together with

the actual data.

Error-correction occurs on each clock cycle (except

during register write cycle). The correction matrix computes corrected data out of the data stored in the 12 bit

registers and rewrites it back at the following clock falling

edge, thus removing any single SEU error. Every register

has its independent error correction system, thus several

simultaneous errors will be corrected as long as they occur

in different registers.

Register

Pwr-Modes

Bits

0:1

Count

2

Field

Power Modes

RF-PLL

2:7

0:7

6

8

(Reserved)

RF-PLL Divider

IF-PLL

0:7

8

IF-PLL Divider

Description

00=Sleep

01=Doze

11=Stand-By

10=Fully active

Currently ignored, set to 0

RF-PLL division factor:

D0 20 + D1 21 + · · · + D7 27

IF-PLL division factor:

D0 20 + D1 21 + · · · + D7 27

Type

RW

N/A

RW

RW

Table 10: Register fields description.

Rev. 1.4, January 31, 2014

Saphyrion Sagl

11

DATASHEET

DI[7:0]

SY1007 GNSS RF Front-End

Hamming

Code

Generator

0

C[3:0]

Hamming

Code [3:0]

1

1

Data [7:0]

Error

Correction

DO[7:0]

D[7:0]

0

WR

RCP

Figure 18: Hamming error correction register.

The various circuit blocks of the SY1007 receive data

directly from the correction matrix rather than from the output of the registers. This ensures that in case of a SEU error the correct value is available immediately within a combinational delay and not with a clock cycle latency. Glitch

suppression logic removes the eventual error correction

glitch, as well as single event transient (SET) glitches.

During a read operation, if a SEU occurs in the same

clock cycle when data is latched by the read shift register,

the incorrect value might be returned back, although the

content of the register itself will be corrected on the next

clock cycle.

13

Applications Information

13.1 Power Control

The SY1007 provides 4 different power modes that can be

used to implement various power saving methods. These

power modes are listed in Table 11 and their purpose is

the following:

• Sleep: In sleep mode all circuits of the SY1007 are

powered down. In this mode, the registers can still

be read or written. Power consumption will mainly

depend on the input clock frequency and the number of accesses that are made to the registers. If the

clock frequency is set to zero, the power consumption consists mainly of leakage currents.

• Doze: In doze mode the band-gap reference and

the voltage regulator are turned on. The time required to enter this state is dominated by the time

required by the voltage regulator to turn on. With a

33µF capacitor it approximately 50ms.

• Stand-By: In stand-by mode the PLL is turned on

while the signal path stays powered down. This

state may be used to allow the PLL to stabilize before entering the fully active mode.

• Fully active: In fully active mode the SY1007 is fully

on and operating.

The power modes of the SY1007 may be selected via the

digital interface by writing in the Pwr-Modes register (bits

[0:1], see table 10). Table 11 shows the approximate time

required to reach stable operation (latency) from the previous state. Exiting any power mode is much faster and

typically takes less than 100µs. Gray coding has been

used to simplify avoiding glitches while switching from one

power mode to the other. Switching from one power mode

to the other may be done in any order.

12

Mode

Sleep

Doze

Stand-By

Code

00

01

11

Fully Active

10

Latency

50ms

5-10ms (depends

PLL loop filter)

150-250µs

on

Table 11: SY1007 power modes.

13.2 Frequency Plans

Since the SY1007 has independent RF and IF local oscillators, it offers a great freedom in the selection of frequency

plans. Basically, any frequency plan that places the IF

somewhere around 100-300MHz and the near base-band

signal bandwidth inside the I/Q filter bandwidth (12MHz

worst-case) is potentially suitable. In the interest of reducing the PLL spurious content a high reference frequency

can be used. The limiting factor is however the resolution of the integer-N PLLs that is 4x RCP for the RF PLL

and RCP for the IF PLL. Using excessively high reference

frequencies may prevent good frequency plans to be designed.

Table 12 shows a few frequency plans examples that

can be implemented using the on-chip PLLs. In these examples the use of either a common RF or IF local oscillator frequency has been assumed together with a reference

frequency of 5MHz. This gives a resolution of 20MHz and

5MHz for the RF PLL and IF PLL respectively. Using a

common IF frequency may simplify the design of the IF

filters, as one single filter type may serve several bands.

The performances of the SY1007’s on-chip PLLs were

tailored for generic GNSS navigation receivers. For more

critical applications requiring better phase noise than the

SY1007 can offer, external local oscillators can be used. In

the interest of reducing the effect of phase noise, in multichannel receivers it is best to share the signal of a single

low-noise local oscillator among all channels rather than

regenerating the local oscillator signals locally. The phase

noise will then be coherent on all channels, such that it can

be rejected as a common-mode signal.

Good frequency plans with shared local oscillators

may be achieved e.g. by using a common RF local oscillator frequency of 1400MHz, as shown in table 12. A single

external RF PLL would then be required, while the on-chip

IF PLLs can still be used. A phase noise improvement of

up to approximately 20dB at offsets below 100Hz may be

achieved this way, without requiring any external IF PLLs.

Saphyrion Sagl

Rev. 1.4, January 31, 2014

DATASHEET

SY1007 GNSS RF Front-End

13.3 Analog Blocks

13.3.1

Low Noise Amplifier (LNA)

The LNA requires matching networks at its input and output. Figure 19 depicts a typical configuration for the LNA

with its matching networks.

AVDD

L2

C2

RF

IN

R1

L1

LNA

LNI

100pF

LNO

L3

C3

100pF

RF

OUT

Band

Frequency

C1

L1

L2

L3

R1

Gain

NF

S11

S22

L1/E1

1575MHz

N/F

3.9nH

5.6nH

6.8nH

N/F

18.9dB

1.6dB

−2.6dB

−14.6dB

L2

1227MHz

N/F

6.8nH

12nH

12nH

N/F

20.4dB

1.5dB

−2.1dB

−23.1dB

L5/E5a

1176MHz

N/F

6.8nH

15nH

12nH

N/F

21.2dB

1.4dB

−1.9dB

−23.3dB

Table 13: Noise matching networks.

C1

Figure 19: LNA configuration (matching networks).

Depending of the type of signal source used (antenna,

external LNA), the input of the LNA may need to be configured for noise matching or for impedance matching, while

the output of the LNA – which typically is connected to

a SAW filter – needs to be impedance matched to 50Ω.

Tables 13 and 14 show typical values for the matching networks and the resulting LNA performances, obtained on

the SY1007 test board.

For the impedance-matched case a RLC network has

been proposed in order to broaden the impedance matching bandwidth. The 100Ω resistor will however increase

the noise figure by about 1.5dB, which is usually acceptable if sufficient gain is placed in front of the SY1007’s

LNA. If the gain of the external LNA is above ≈25dB an

attenuator can be used to further improve matching and

achieve a higher interferer resilience.

As with any GHz RF circuit, RLC component types and

design of the PCB are critical to the performances of the

LNA. Proper RF PCB design is needed, while components

with size 0805 or smaller shall be used. The values of all

matching components depend on the layout of the PCB

or the substrate dielectric constant. The component values shown in Tables 13 and 14 have been found experimentally on the SY1007 test board and may (will) vary and

require optimization. LNA S-parameters in Touchstone format are available.

Band

Frequency

C1

L1

L2

L3

R1

Gain

NF

S11

S22

L1/E1

1575MHz

3.3pF

4.7nH

5.6nH

6.8nH

100Ω

20.0dB

4.5dB

−17.6dB

−12.6dB

L2

1227MHz

3.3pF

8.2nH

12nH

12nH

100Ω

22.5dB

3.5dB

−16.13dB

−13.6dB

L5/E5a

1176MHz

3.3pF

10nH

15nH

12nH

100Ω

21.0dB

4.2dB

−21.3dB

−13.2dB

Table 14: Impedance matching networks.

Coupling between LNI and LNO shall be minimized.

Stray inductances and capacitances will create a Hartley

oscillator tank-circuit around the LNA. If the capacitance

between LNI and LNO is not minimized the LNA will break

into sustained oscillation. A ground track running between

LNI and LNO is usually needed. Please make also sure

that AVDD is very well decoupled. Any stray impedance

on AVDD will appear in series with L2, thus upsetting output matching.

In systems having a gain >30-35dB in front of the

SY1007, the on-chip LNA may not be necessary or may

even lead to poor front-end linearity if used. In such cases

the on-chip LNA may be disabled by tying its input (LNI) to

ground and leaving its output (LNO) open. In such case

no components need to be mounted around the LNA.

GNSS signal

GNSS Freq.

LO freq.

IF1

IF2

20-25MHz Signals, RCP=5.0MHz, RF-LO=1400MHz, fs=40-50MHz

GPS L1, GAL E1bc

1575.42MHz

175MHz

175.42MHz

0.42MHz

GLO L1

1601.71MHz

200MHz

201.71MHz

1.71MHz

GPS L2

1227.60MHz

170MHz

172.40MHz

2.40MHz

GLO L2

1245.78MHz

155MHz

154.22MHz

0.78MHz

GPS L5, GAL E5a

1176.45MHz

225MHz

223.55MHz

1.45MHz

GAL E5b

1207.14MHz

195MHz

192.86MHz

2.14MHz

GAL E6 (BPSK5)

1278.80MHz

120MHz

121.20MHz

1.20MHz

20-25MHz Signals, RCP=5.0MHz, IF-LO=175MHz (⇒IF-VCO=350MHz), fs=40-50MHz

GPS L1, GAL E1bc

1575.42MHz

1400MHz

175.42MHz

0.42MHz

GLO L1

1601.71MHz

1420MHz

181.71MHz

6.71MHz

GPS L2

1227.60MHz

1400MHz

172.40MHz

2.60MHz

GLO L2

1245.78MHz

1420MHz

174.22MHz

0.78MHz

GAL E5b

1207.14MHz

1380MHz

172.86MHz

2.14MHz

GAL E6 (BPSK5)

1278.80MHz

1460MHz

181.20MHz

6.20MHz

Table 12: Some possible frequency plans (for GPS, GALILEO and GLONASS).

Rev. 1.4, January 31, 2014

Saphyrion Sagl

13

DATASHEET

13.3.2

SY1007 GNSS RF Front-End

An RF filter is always required with the SY1007, in order

to remove out-of-band signals that could disturb chip performance. A filter with sufficient selectivity to suit the operating environment should be chosen. The most important

filter parameters to look at are:

•

•

•

Attenuation of the image frequency (≥20dB recommended).

Attenuation of signals from on-board transmitters.

Insertion loss, especially if passive antennas and no

external LNAs are used (≤2.5dB recommended).

Either SAW filters or dielectric filters may be used as long

as sufficient performances are available. Suitable filters

can be found e.g. by Vectron, ComDev or Norspace, in

some cases already qualified for Space use (ESCC 9000

or MIL-STD-883 Class S).

The PCB layout around the RF filter is critical to filter

performance. Input and output of the filter shall be very

well isolated, otherwise the RF signal would be allowed to

bypass the filter, thus compromising its out-of-band rejection. Figure 20 shows a possible PCB layout (for a SAW

filter in LCC package). A fence between filter’s input and

output – well connected to the ground plane with several

vias – minimizes capacitive coupling that would bypass the

filter.

Ground

Ground

IN

OUT

Ground

Ground

Figure 20: Suggested SAW filter PCB layout.

13.3.3

Band

Low, 1.2GHz (L2-L5)

High, 1.6GHz (L1)

RF Filter (SAW or Dielectric)

RF Mixer Input

C

2.7pF

2.0pF

L

6.8nH

5.6nH

Table 15: Component values for LC balun.

Again – as usual with RF designs – good PCB RF

layout is necessary, as any stray impedance will upset input matching, reduce the conversion gain of the mixer and

worsen its noise figure.

The input of the RF mixer is biased to about 400mV

and shall never be DC shorted to ground or receive any DC

biasing from outside, otherwise the SY1007 will be permanently damaged. If the RF filter or balun has a DC path to

ground DC blocking series capacitors shall be used. Such

capacitors may also be used to compensate possible stray

inductance of the PCB trace; as a starting point the recommended value is 18pF, which should then be optimized

experimentally.

13.3.4

IF Filter

The SY1007 requires an external IF filter for channel selection and to filter off noise at the images of the ADconverter. Various IF filter types may be accommodated by

the SY1007 in order to suit different operating conditions.

When selecting an appropriate IF filter it is however important to consider that all receiver’s filtering requirements

shall be implemented by the RF and IF filters, before the

high gain IF-strip, otherwise poor receiver performances

may result.

Although the SY1007 accommodates various IF-filter

types, in most cases a 4th or 6th order bandpass LC-filter

is used. Figure 22 shows the schematic diagram of such

filter. It consists of a parallel resonator (L1-C1, implementing 2 poles of the filter) followed by a coupled resonator 4th

order stage (L2-C2, L3-C3-R3 and the coupling capacitors

C4-C5).

The RF mixer input is 50Ω balanced and can typically be

connected directly to either a SAW filter (with balanced

output) or to a 1:1 balun. Suitable baluns for the SY1007

are transformer, transmission line or discrete LC designs.

LC baluns may be preferable since they use simple LC

parts readily available in space-qualified quality.

R3

L1

L2

L3

C4

C1

C3

C5

C2

C

C

MIXP

L

RF-IN

Unbal.

(50Ω)

Mixer

IF2N

IF Amp

IF VC Amp

Figure 22: IF LC-filter configuration.

C

Figure 21: LC balun schematic diagram.

A possible LC balun structure is shown in Figure 21.

Since an LC balun is selective, the values of the components must be adapted to the operating frequency of the

balun. In order to cover all GNSS bands two designs are

sufficient. Table 15 shows the LC values for these two

designs (low and high band), which must be adjusted experimentally to fit PCB parasitics.

14

IF1N IF2P

RFN

RFP

RF-OUT

Balanced

(50Ω)

L

C

MIXN IF1P

The whole IF filter is best considered as a single filter

(rather than separate filters) and may be calculated with

readily available computer programs or using filter tables.

Since the input impedance of the VCA is high, resistor R3

is necessary if a 6th order filter is to be implemented. This

resistor however causes the insertion loss of the filter to

increase. In order to avoid an excessive insertion loss that

can no longer be compensated by the IF VCA this resistor should be selected to be ≥600Ω. A good starting point

could be 1.0-1.5kΩ. A 600Ω resistor already results in an

extra 6dB insertion loss.

Saphyrion Sagl

Rev. 1.4, January 31, 2014

DATASHEET

SY1007 GNSS RF Front-End

In many cases a 4th order filter is sufficient. In this

case C4 and C5 shall be set to 100pF and C3-L3-R3 omitted. 4th order IF filters for 3 different IF frequencies are

shown in the application example (Section 16, Figure 29).

Figure 23 shows a measured frequency response (from

120MHz to 220MHz) of the 4th order 174MHz IF filter of

the application example.

both I and Q outputs. Traces with equal length and width

should be used as well.

C1

100nF

OIP

OIN

SY1007

SY1008

C2

100nF

I1N

C3

100nF

OQP

OQN

I1P

C4

I0P

SY1017

I0N

100nF

AGCI

AGCO

C5

174MHz IF Filter

1.0nF

10

Figure 24: Typical SY1007 to SY1017 interface.

5

0

Amplitude

5.0 dB/

−5

−10

−15

−20

−25

−30

−35

−40

120

130

140

150

160

170

180

190

200

210

220

Center 170.0 MHz

Span 20.0 MHz

#Res BW 1.0 MHz

VBW 1.0 MHz

Sweep 401 pts

Figure 23: Measured 4th order IF-filter response.

Accurate, temperature stable components shall be

used in the IF filter. Ceramic NPO capacitors with 2%

(maximum 5%) tolerance are recommended. Placing two

capacitors in parallel as shown in Figure 29 allows an easy

fine tuning of the IF filter. Wire-wound or multi-layer inductors (again with maximum 5% tolerance) can be used

for values below about 500nH, while shielded ferrite-core

inductors are useful for higher values. Unshielded opencore ferrite inductors shall never be used in the IF filter.

Open-core ferrite inductors are in fact efficient antennas

(rod antennas) that would easily pick-up any interference

around the frequency to which the IF filter is tuned.

13.3.5

IF-Strip and Quadrature Output

The IF-strip of the SY1007 comprises a VCA with logarithmic (dB-linear) control input and a quadrature downconverter. The gain of the VCA is controlled by the voltage applied to pin ACGI, which is typically obtained with

the DA-converter of a SY1017. When used in combination

with the SY1017 a gain step of about 1dB is obtained. If a

different device is used to generate the AGC control voltage it must be able to produce a V(AGCI) = 0.2V to 2V in

order to cover the whole gain control range. Please observe the temperature dependence of gain vs. V(AGCI),

Fig. 8. Since the AGC control is rather sensitive (about

9mV/dB) the control voltage shall be kept clean, otherwise

gain modulation will occur. An RC low-pass filter may be

used to reduce possible noise on pin AGCI.

The near base-band quadrature output is available on

pins OIP, OIN, OQP, OQN. Typically these outputs are ACcoupled to a SY1017 AD-converter ASIC, as shown in

Fig. 24. 100nF ceramic X7R (or better) capacitors are recommended.

These outputs are filtered with on-chip 3rd order lowpass filters and are internally buffered with low output

impedance (about 125Ω) amplifiers to minimize errors due

to loading effects. In order to keep amplitude and phase

errors low it is however mandatory that load impedances –

including PCB strays – are kept as similar as possible on

Rev. 1.4, January 31, 2014

Although the output impedance of the I/Q outputs is

125Ω, this does not mean that they can drive a 125Ω load.

OIP-OIN and OQP-OQN shall in fact not be loaded with

less than 10kΩ, or severe distortion and amplitude limiting

will occur.

Adding base-band off-chip filtering on the I and Q outputs as a means to improve channel filtering is strongly

NOT RECOMMENDED. Such filtering – if used – will introduce quadrature errors (unless the filters are carefully

aligned) and will very likely cause AGC misbehavior or

receiver blocking in presence of near-band interferers. If

base-band filtering is required please make sure that any

and all interferers are removed at RF and IF, before they

can reach the high gain IF-strip (pins IF2P-IF2N).

13.3.6

RF and IF Frequency Synthesizers

The SY1007 contains two frequency synthesizers which

generate the required RF and IF local oscillator signals.

RF and IF PLLs are enabled with pins RENB and IENB

(active on low logic level) respectively, and can be enabled

or disabled independently from each other.

Both RF and IF synthesizers need an off-chip inductor

for the VCO, whose value depends on the required local

oscillator frequency and that shall be adjusted depending on PCB strays. In order to align the PLL, a VCO inductor value of 4.7nH and 47nH respectively can be used

as starting point, then the reference frequency of the PLL

shall be swept and the loop filter voltage measured and

recorded. Curves similar to the ones shown in Figures 9

and 10 (Section 7) should be obtained. The VCO inductors

shall then be adjusted (replaced) until the PLL operating

point is in the middle of the measured PLL curve.

The Q of the inductors is instrumental in obtaining reasonable VCO performances and phase noise. If inductors

with excessively low Q are used phase noise will increase,

while the VCO may even stop operating, especially at the

higher temperature limit. If such behavior is noticed inductors with higher Q shall be used.

Caution: great attention has to be paid to the PCB

layout around the VCO inductors, especially the one of the

RF VCO. The shortest, straightest tracks shall be used to

connect the inductor to the SY1007, otherwise the desired

VCO frequency may not be attainable with any inductor

value, or spurious oscillations, not defined by the VCO inductor, may result. The stray inductance of the PCB traces

connecting the inductor to the RF VCO shall be evaluated

if inductors below about 2.7nH are required to reach the

proper VCO operating frequency, or if the SY1007 RF PLL

fails to lock or behaves in a strange manner. Please remember that 1nH (about 1.2-1.5mm PCB track) and 1pF

(a small PCB area, 2-3 footprints) at 1.6GHz are already a

reactance of 10Ω and 100Ω respectively.

Saphyrion Sagl

15

DATASHEET

13.3.7

SY1007 GNSS RF Front-End

13.3.8

RF and IF PLL Loop Filters

The loop filters for the RF and IF PLLs are external and

shall be connected to pins RPLL and IPLL respectively. A

CRC network, as shown in Figure 25, is recommended.

The components can be calculated using the VCO sensitivity data and the desired division ratio. The nominal

current of the charge pump is 50µA.

RPLL, IPLL

External Local Oscillators

In applications that require better phase noise than the

SY1007 can offer, the SY1007’s on-chip PLLs can be disabled by setting RENB or IENB to logic high and external

oscillators can be used instead. The signal of a balanced

external oscillator shall be applied to pins RL1-RL2 (RFVCO) and/or IL1-IL2 (IF-VCO). The external RF-VCO shall

be set to the desired RF-LO frequency, while the external

IF-VCO shall be set to twice the desired IF-LO frequency

to account for the dividing-by-two quadrature LO generator

(see Section 10 and Figure 15).

C2

C1

xL1

SY1007

SY1007

R1

xL2

xL1

xL2

C1

Figure 25: PLL loop filter schematic diagram.

The cut-off frequency of the loop filter is a trade-off

between phase noise and spurious signals power, and

should therefore be dimensioned according to the needs of

the given application. Figure 26 shows schematically the

idealized behavior of the phase noise of the SY1007’s RF

PLL for two different loop filter bandwidths (purple: wideband, red: narrow band loop filter) as well as the contributions of the VCO and the charge pump alone.

-50

VCO phase noise

(free running)

-3d

B/o

ct.

-70

Charge pump

thermal noise

-80

Charge pump

flicker noise

/o

dB

-6

-90

.

ct

Phase noise [dBc/Hz]

-60

-100

-110

100

1k

10k

100k

1M

Frequency offset [Hz]

Figure 26: Phase noise of RF PLL (idealized).

A wide-band loop filter (faster PLL, purple curve) gives

better phase noise performances at the expense of higher

spurious signals. In contrast, a narrow-band loop filter attenuates the spurious signals to the detriment of the phase

noise performance (slower PLL, red curve). A phase margin around 50-55◦ is recommended if fast lock time is desired, otherwise lower phase margins can be used if spurious signals have to be reduced. Examples of loop filter

designs are shown in the application example (Section 16).

The loop filter – or at least C2 (in Figure 25) – should

be mounted close to the RPLL and IPLL pins in order to

provide a low inductance RF path to ground. PCB tracks

carrying noisy signals (e.g. digital lines) should be kept

away from the loop filter, otherwise noise could be injected

into the PLL, thus degrading phase noise performances by

directly modulating the VCO.

16

1nF

Transmission line

(balanced, 100Ω)

R1

100Ω

C2

1nF

Figure 27: LO distribution (bridging).

The VCO inputs are high impedance and may be terminated with an inductor to compensate their input capacitance if necessary. These inputs are internally biased to

AVDD and shall not be forced. A termination resistor may

also be used to properly terminate the LO transmission

line if necessary.

If an on-chip PLL is disabled no loop filter is required

on its respective pin (RPLL or IPLL). In that case these

pins shall be left open and no connection shall be made to

them. Pins RPLL and IPLL are internally biased (to AVDD)

when on-chip PLLs are disabled and shall not be forced.

In systems using many RF channels in parallel that

share the same local oscillator frequencies, the local oscillator signals can be distributed in a simple and effective

way using a single transmission line as shown in Figure 27.

This LO signal sharing structure is possible thanks to the

high input impedance of the SY1007’s LO inputs.

The transmission line – e.g. 100Ω – shall be terminated

at its end, while the taps to the SY1007 shall be very short

to avoid stubs that would cause line mismatch. By bridging

many SY1007 on the same transmission line lossy power

splitters are avoided and the LO power can be lower. With

careful PCB layout, up to 4-5 SY1007 can be bridged on

a single transmission line. Please observe the signal level

requirements (Section 5 and Note 15).

13.4 Voltage Reference and Regulator

Biasing to the SY1007 is provided by an on-chip 1.17V

band-gap voltage reference and a 1.9V voltage regulator.

These voltages are available on pins VBG and VB respectively. The 1.9V regulator provides power to the VCO.

Both band-gap reference and voltage regulator are active

in doze mode and up.

A capacitor of at least 1µF (ceramic X5R or X7R) is

required for stability on both VBG and VB, which shall

be mounted close to the chip. To improve noise performances, in particular the phase noise of the VCO, a capacitor of at least 33µF is recommended for VBG.

Saphyrion Sagl

Rev. 1.4, January 31, 2014

DATASHEET

SY1007 GNSS RF Front-End

Both outputs may supply power to an external load if

desired. The maximum available output current is 200µA

and 1mA respectively. It is however important that these

loads, if used, do not introduce any noise into VBG and

VB. In particular, noise into VBG may disturb the whole

chip, while noise into VB may disturb especially VCO and

PLL.

13.5 Power Supply

The SY1007 requires two power supplies: analog (AVDD)

and digital (DVDD). The recommended ranges are shown

in Table 16. The power supplies need not be well regulated but must be well filtered. This applies in particular to

the analog power supply AVDD. DVDD may be taken either from AVDD via an RC or LC network or from some

other (clean) voltage. Using a general power supply –

e.g. the power supply for some micro-controller or GNSS

base-band processor – as DVDD is not recommended, as

digital switching noise would be injected into the SY1007

thus degrading its performance.

Power Supply

AVDD (Analog)

DVDD (Digital)

Min

2.4V

2.2V

Max

3.6V

AVDD+0.2V

Table 16: Power supply ranges.

No particular sequencing is needed while applying

power to the SY1007. AVDD and DVDD may be applied

simultaneously or in any order. Increasing DVDD above

its maximum operating level (AVDD+0.2V) is not recommended except during the power on transient. This will

not cause any permanent damage, but the SY1007 will not

operate correctly if the condition is violated. Once DVDD

is returned to the allowed range the SY1007 will resume

proper operation from itself while no data is lost if DVDD is

kept above its minimum rating of 2.2V.

Signal voltages shall not be applied to the SY1007 before the power supply is applied, otherwise the ESD protection diodes may become forward biased and possibly

be damaged. Digital signals may track DVDD during power

transients, as long as the DVDD+0.2V condition is not violated.

Power supply decoupling is always required. A 100nF

ceramic capacitor (X7R) mounted very close to the device

body is recommended on each AVDD and DVDD pins. A

2.2µF (or higher) ceramic or tantalum capacitor may be required on AVDD, especially if AVDD is not well regulated.

A 1nF capacitor has to be mounted very close to the LNA

output matching network on the AVDD supply.

14

Handling Precautions

14.1 Hazardous Substances

The SY1007’s solder balls contain lead (Sn60-Pb40),

therefore the SY1007 is not RoHS compliant and shall

be handled accordingly. Discarded SY1007 devices shall

not be dispersed into the environment or disposed of with

common waste.

Apart from the lead contained in the solder balls,

the SY1007 does not contain any other hazardous materials, in particular no mercury (Hg), cadmium (Cd) or

Rev. 1.4, January 31, 2014

hexavalent chromium (Cr6+), the flame retardants polybrominated biphenyls (PBB) and polybrominated diphenyl

ethers (PBDE), or berillium oxide (BeO) ceramic.

14.2 Storage

The SY1007 is packaged in a ceramic-metal package that

is not sensitive to humidity, however improper storage may

cause contamination or oxidation of the solder balls thus

impacting solderability. The product shall not be exposed

to high humidity or to direct sunlight, harmful/corrosive

gases or dust. Also avoid storing it in locations where sudden temperature changes may occur.

To ensure long shelf life, the product should be stored

in a controlled temperature (≈20-25◦ C) and humidity

(<60%) environment, possibly in its original shipping bag.

Do not open the bag until just before product’s use. If longterm storage of several years is anticipated, the product

should be stored in a dry cabinet.

15

Radiation Tolerance

The SY1007 is a rad-hard device and several countermeasures have been taken during its design to achieve a high

degree of radiation tolerance. The extensive use of guard

rings and other latch-up prevention techniques – especially in the I/O area – yields excellent latch-up immunity.

2

have proven the

Heavy ion tests up to a LET of 45MeV cm

mg

chip’s robustness against both latch-up and SEU. Several

DUTs have been tested at temperatures up to 85◦ C and a

maximum supply voltage of 3.6V until a cumulated fluence

of 1E+7 ions/cm2 without detecting any latch-up.

2

If requirements higher than 45MeV cm

have to be fulmg

filled some latch-up protection is required. This may consist of a current limited (40-50mA) voltage regulator with a

fast acting disable function to release the latch-up. Specific latch-up protection circuits are also available on the

market, which can be used with the SY1007. The total decoupling capacitor on the SY1007’s power supply shall be

limited to <10µF to avoid burn-out of the SY1007 due to

the capacitor surge.

All registers are protected against SEU with a Hamming error correction mechanism, while a parity bit protects communications from the master device to the

SY1007. It is however good practice not to rely on the

built-in SEU protection alone. It is recommended that after a write operation a read operation to the same register is performed, while all registers should periodically

be read back to check their contents. If corrupted data

is found then re-read the register, if the data is still wrong

then rewrite the register and check it again. Checking back

the registers is the first thing to do in case of suspicion of

configuration loss of the device (e.g. if the receiver stops

working suddenly). Since the RF-PLL register remains selected when the SY1007’s interface is idle, accessing it

at the end of a register verification operation further minimizes risks of SEU.

The SY1007 comes into a ceramic-metal hermetic

package containing no organic materials, while eutectic –

rather than epoxy – die attach has been used. This device

will therefore not decompose or release any substantial

amount of gas or organic contaminants under vacuum or

high radiation levels.

Saphyrion Sagl

17

DATASHEET

16

SY1007 GNSS RF Front-End

Application Example

Figure 28: Application example: top level.

18

Saphyrion Sagl

Rev. 1.4, January 31, 2014

DATASHEET