RF IV Waveform Engineering Applied to VSWR Sweeps and RF

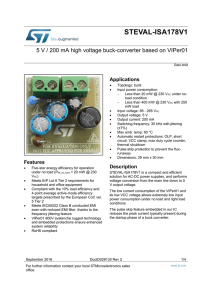

advertisement